0% found this document useful (0 votes)

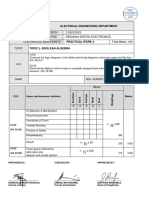

85 views8 pagesDigital Electronics Syllabus

This document outlines the syllabus for a Digital Electronics course. It provides details on course description, desired learning outcomes, assessment procedures, and learning plan. Key topics include fundamentals of digital circuits, logic variables like NOT, AND, OR, and assessment will evaluate mastery of practical and presentation skills.

Uploaded by

ldp100476Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as DOCX, PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

85 views8 pagesDigital Electronics Syllabus

This document outlines the syllabus for a Digital Electronics course. It provides details on course description, desired learning outcomes, assessment procedures, and learning plan. Key topics include fundamentals of digital circuits, logic variables like NOT, AND, OR, and assessment will evaluate mastery of practical and presentation skills.

Uploaded by

ldp100476Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as DOCX, PDF, TXT or read online on Scribd

/ 8