0% found this document useful (0 votes)

83 views31 pagesIntroduction To x86 Architecture

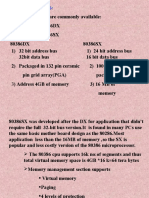

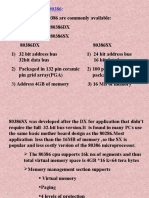

The document provides an overview of x86 architecture, detailing the evolution of Intel microprocessors from the 8080 to modern IA-32 and P6 families. It discusses CPU modes, memory layout, assembly syntax, and calling conventions, highlighting the complexity and features of x86 architecture. Additionally, it covers data types, including numeric and floating-point types, and presents examples of assembly instructions and memory encoding.

Uploaded by

ameerscoursesdCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

83 views31 pagesIntroduction To x86 Architecture

The document provides an overview of x86 architecture, detailing the evolution of Intel microprocessors from the 8080 to modern IA-32 and P6 families. It discusses CPU modes, memory layout, assembly syntax, and calling conventions, highlighting the complexity and features of x86 architecture. Additionally, it covers data types, including numeric and floating-point types, and presents examples of assembly instructions and memory encoding.

Uploaded by

ameerscoursesdCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 31