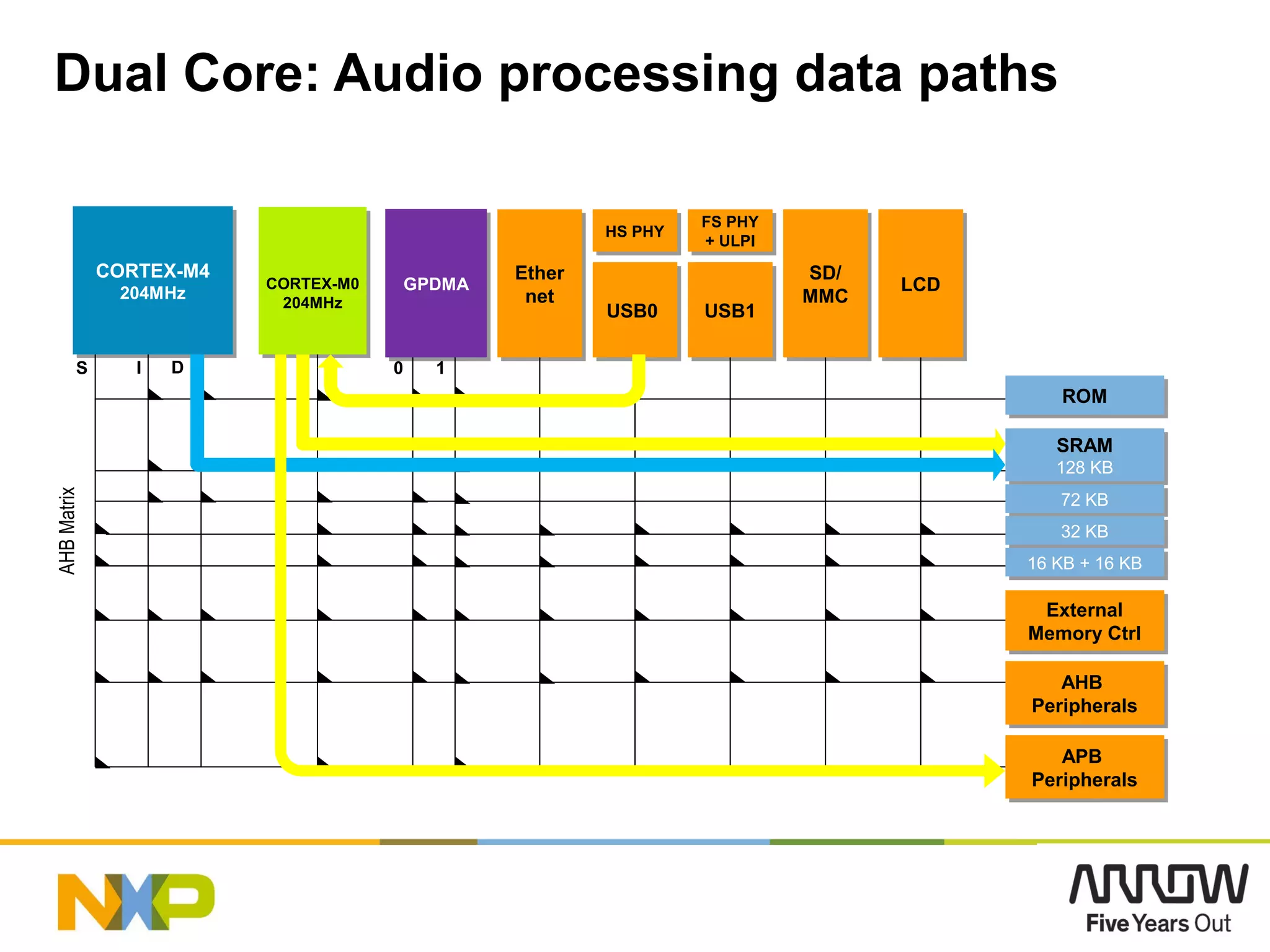

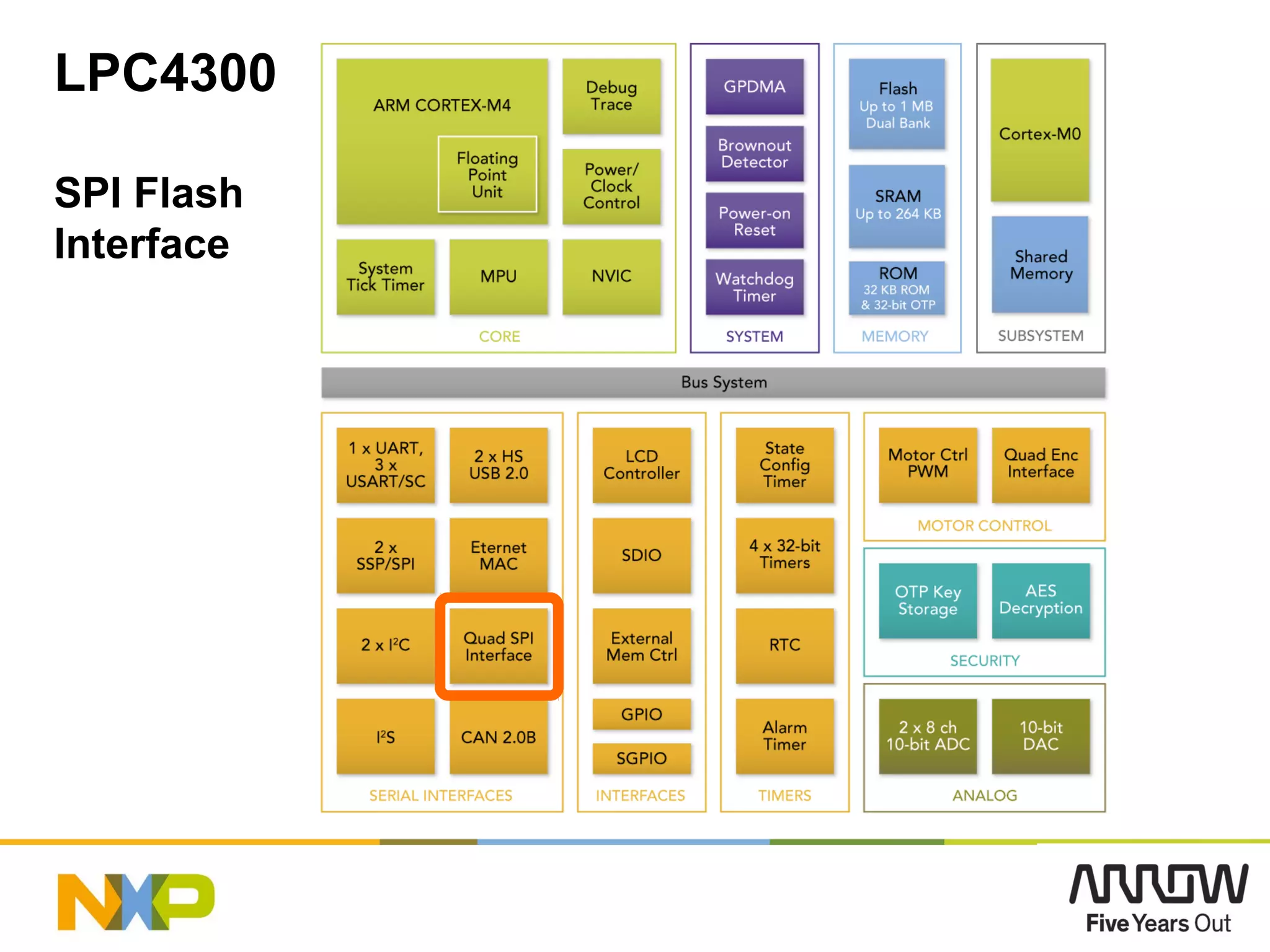

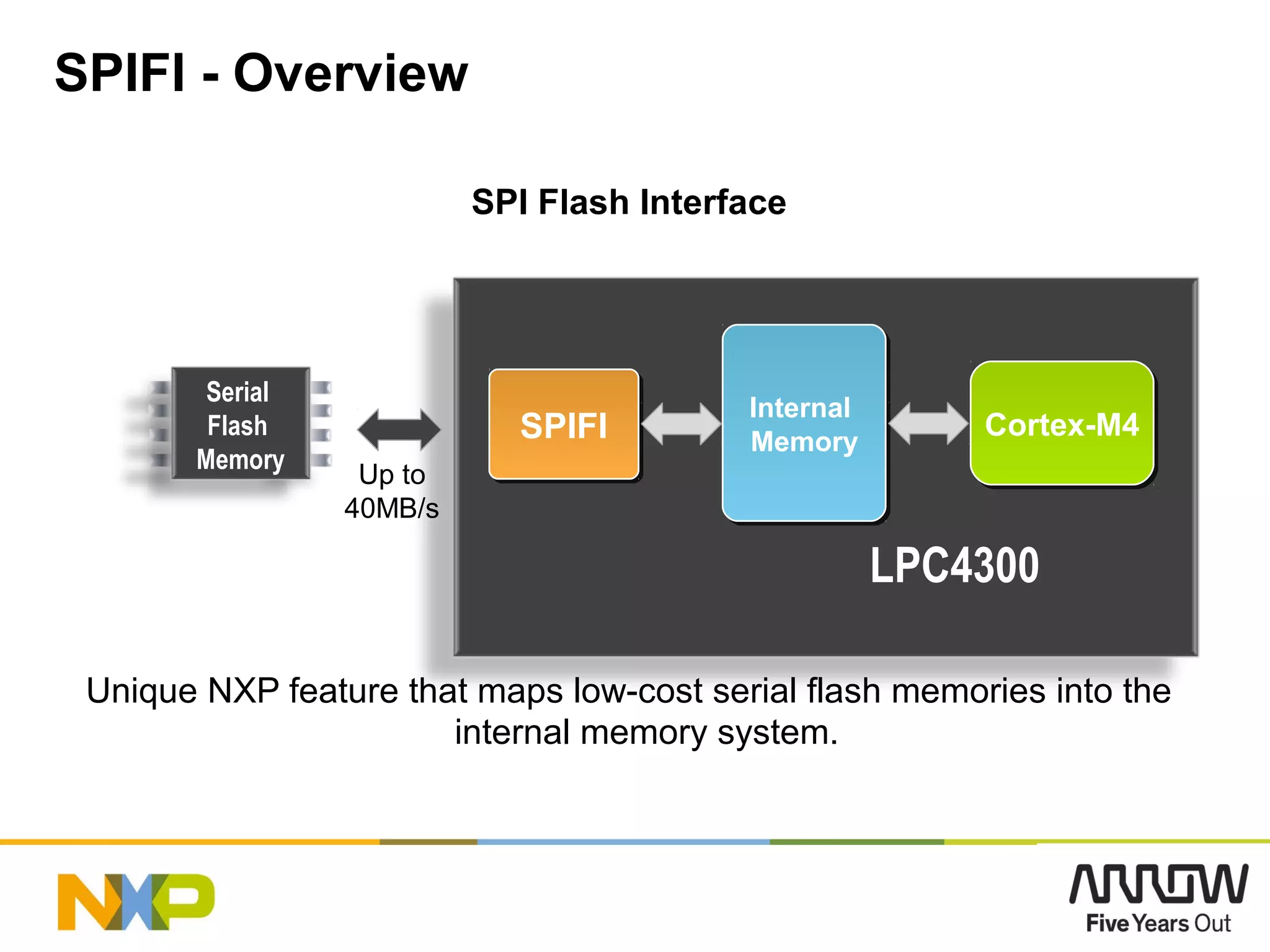

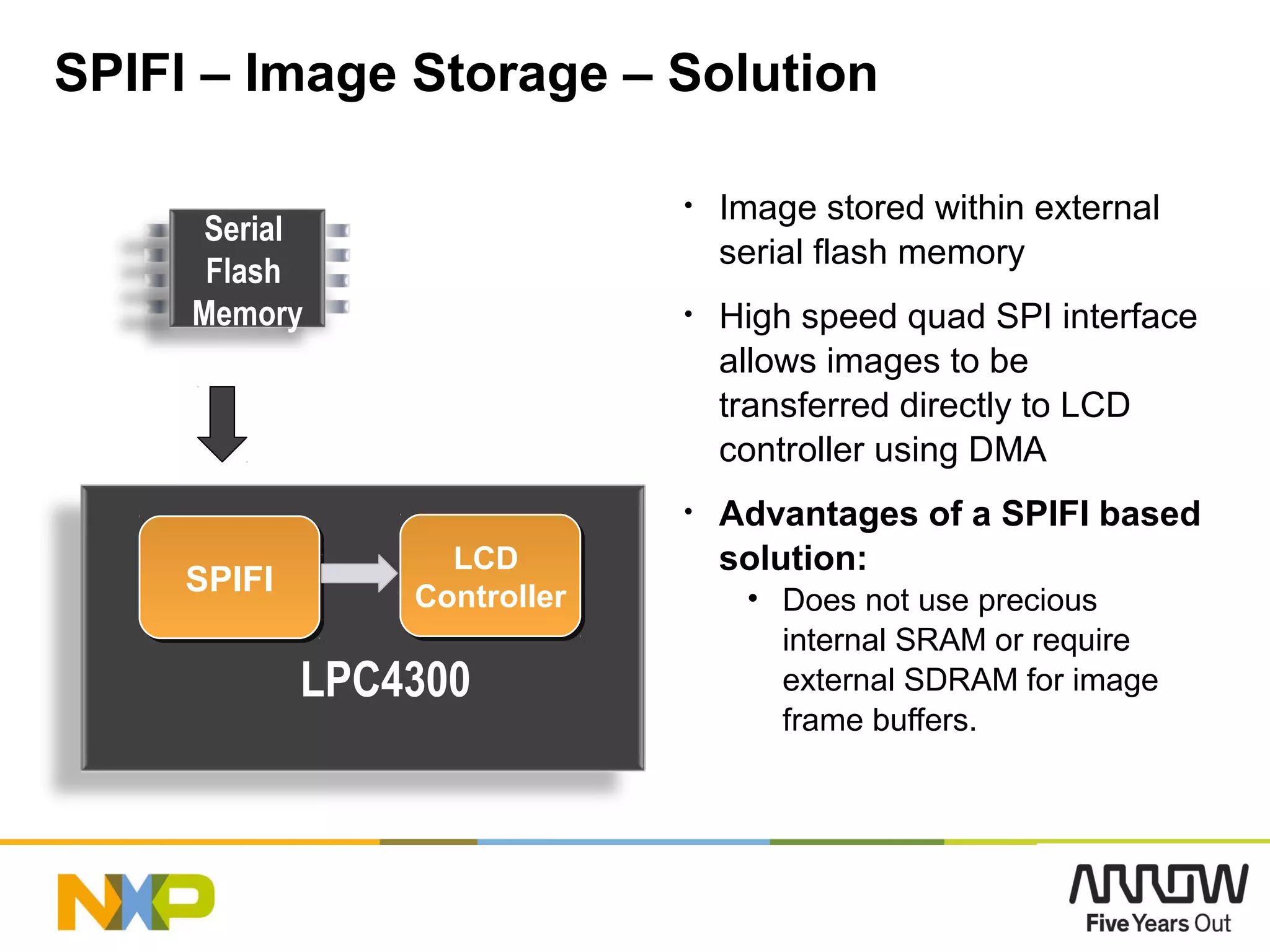

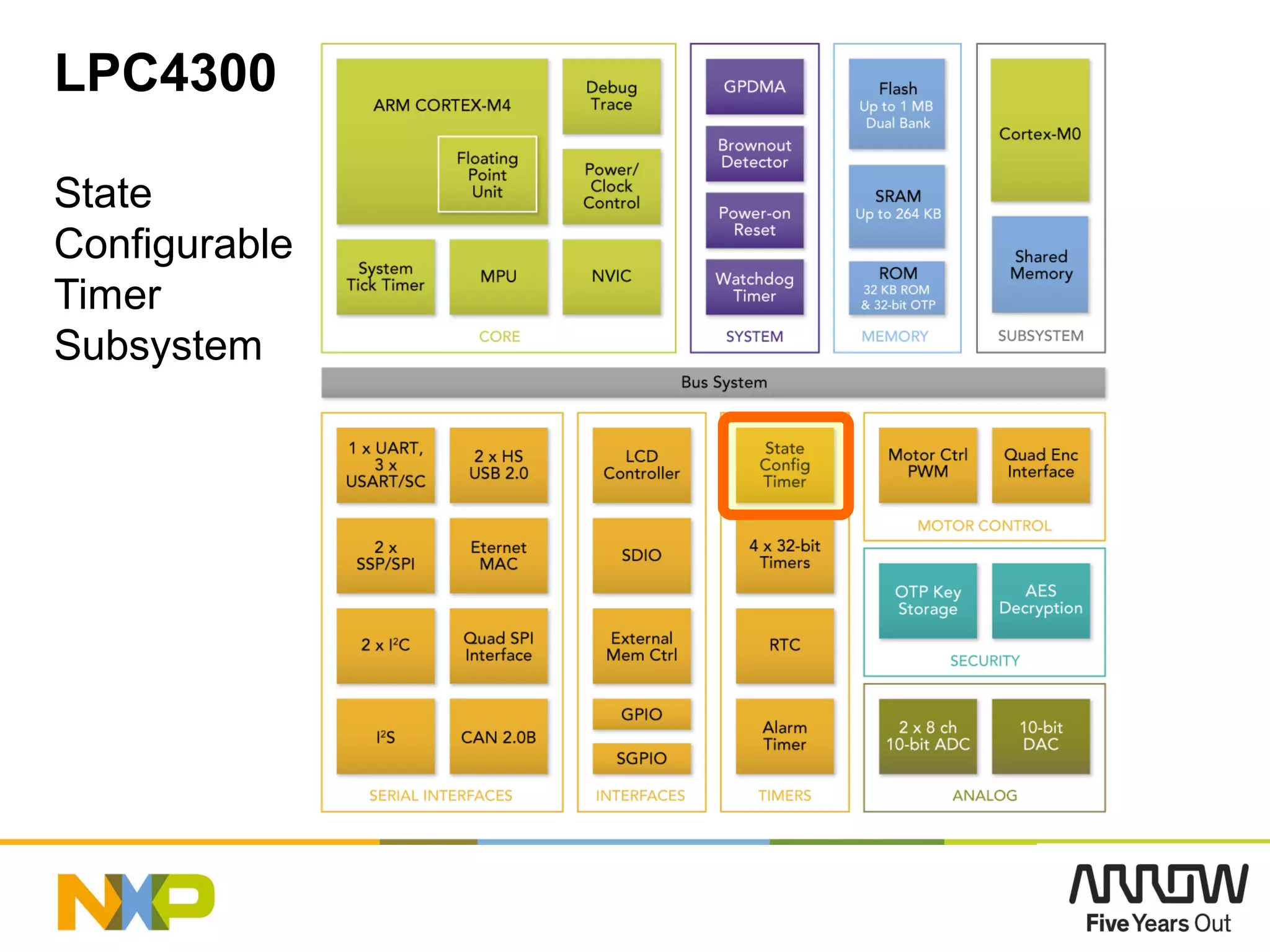

The document outlines NXP's LPC4300 series of dual-core microcontrollers, featuring ARM Cortex-M4 and Cortex-M0 processors designed for high performance and low power consumption. It highlights their flexibility, advanced peripheral offerings, and compatibility with various ARM architectures, making them suitable for a wide range of applications. Key specifications include memory options, processing speeds, and interfaces, demonstrating a comprehensive approach to addressing the evolving needs of microcontroller technology.