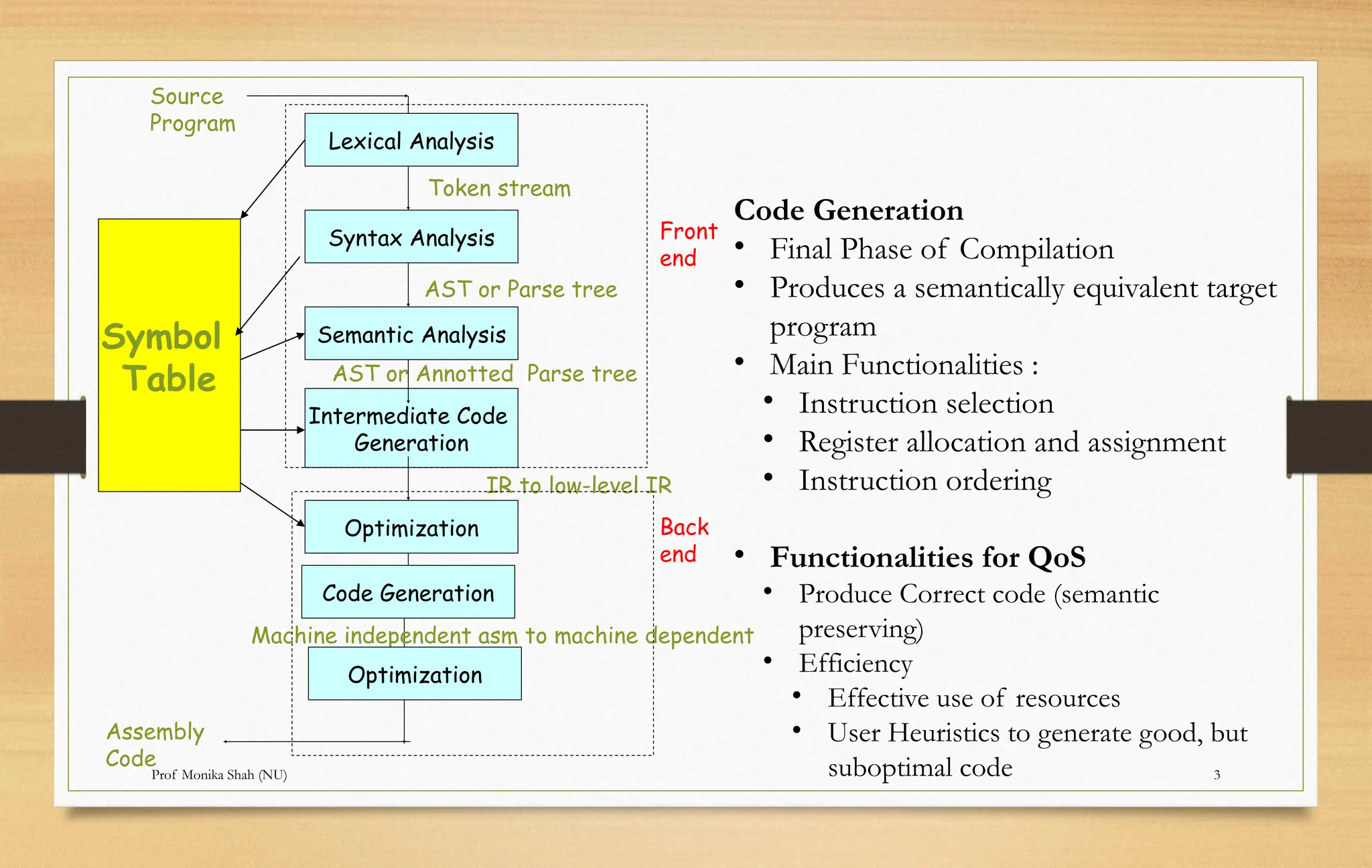

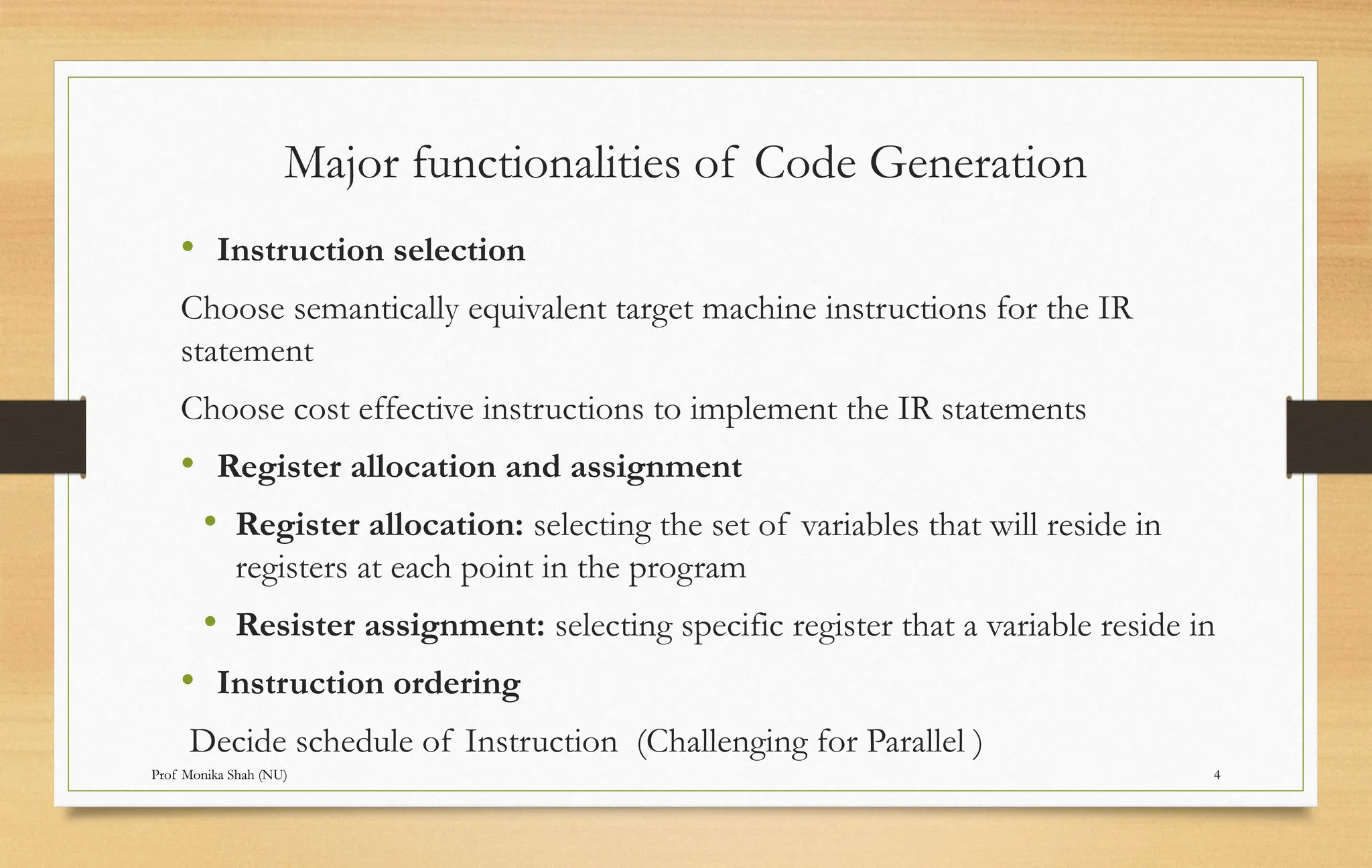

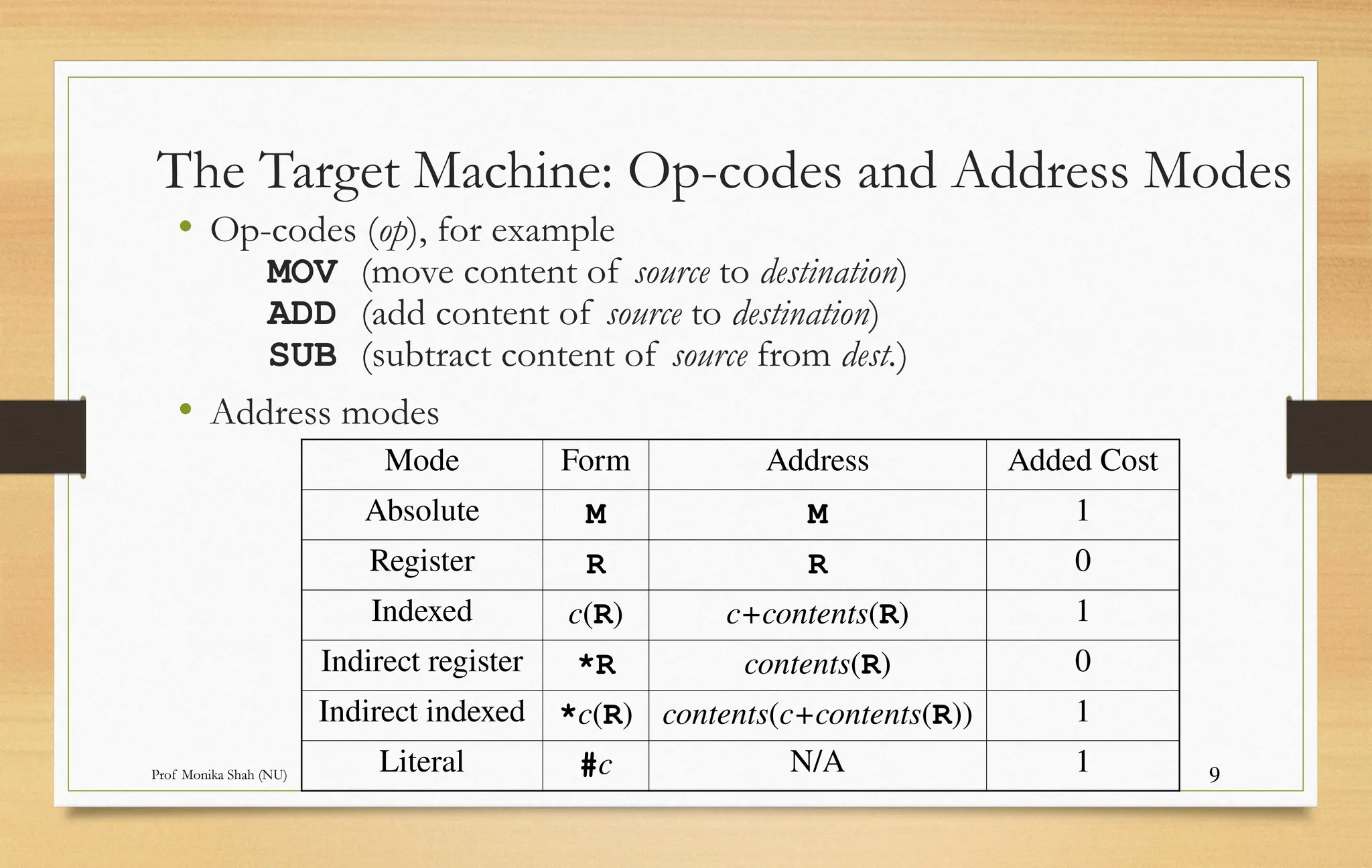

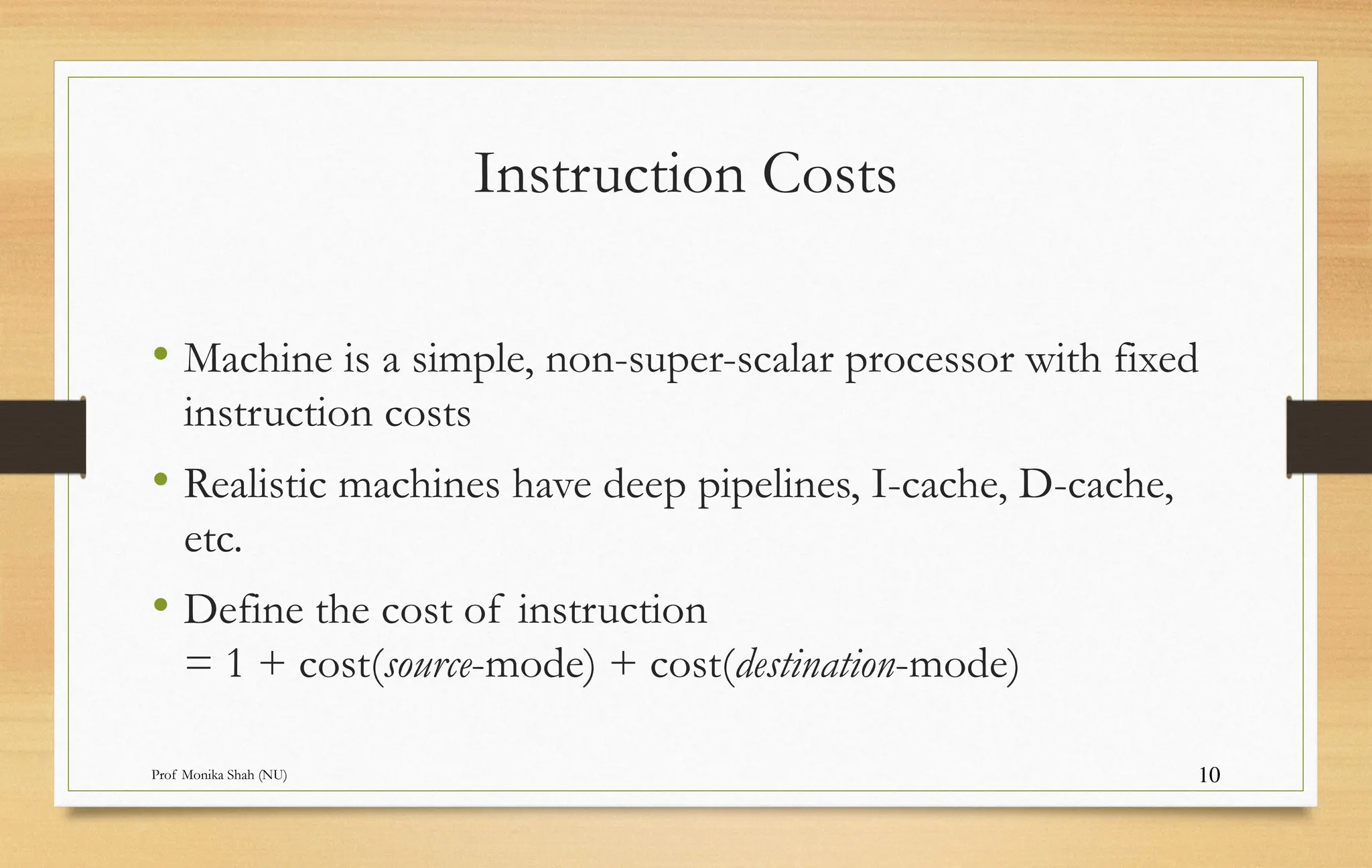

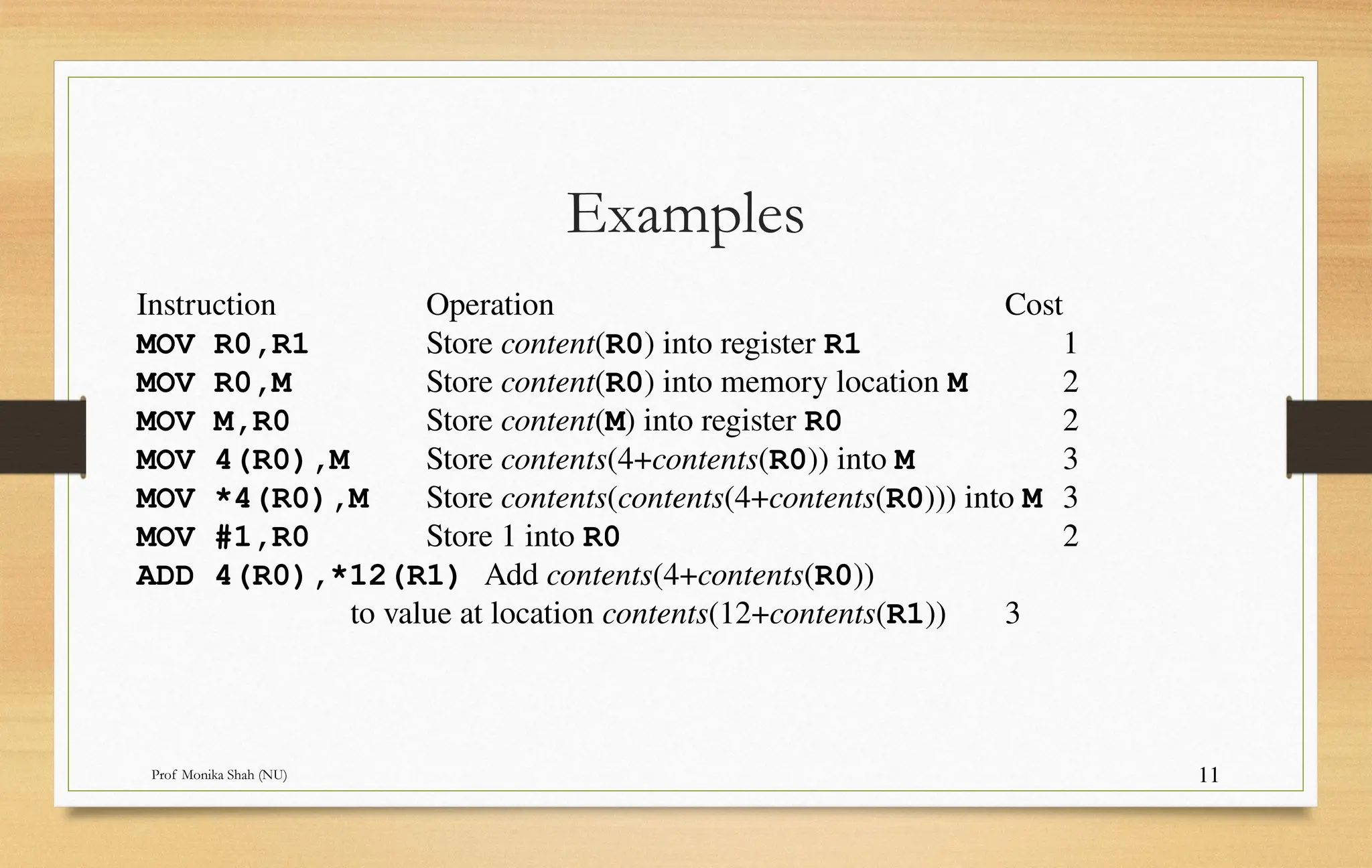

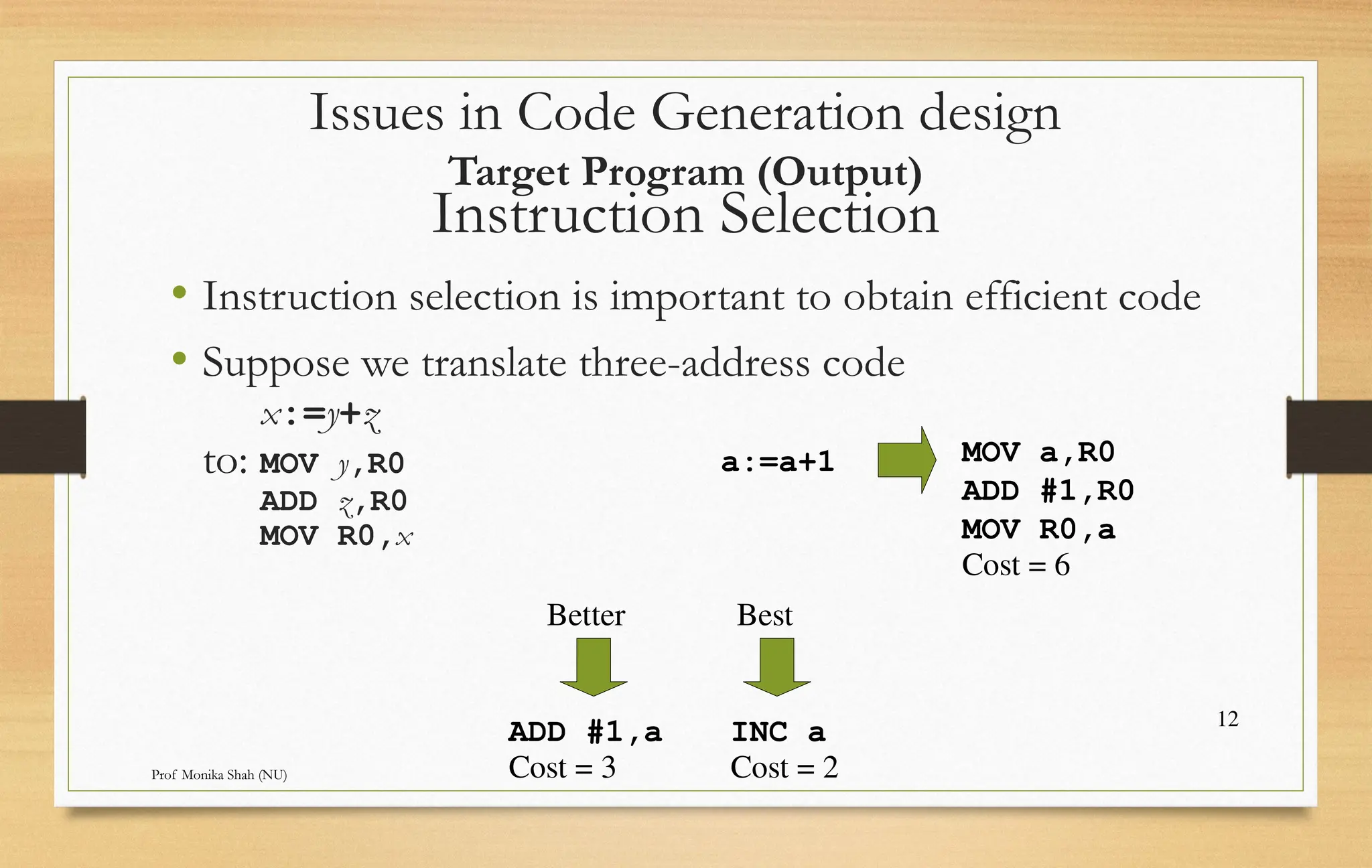

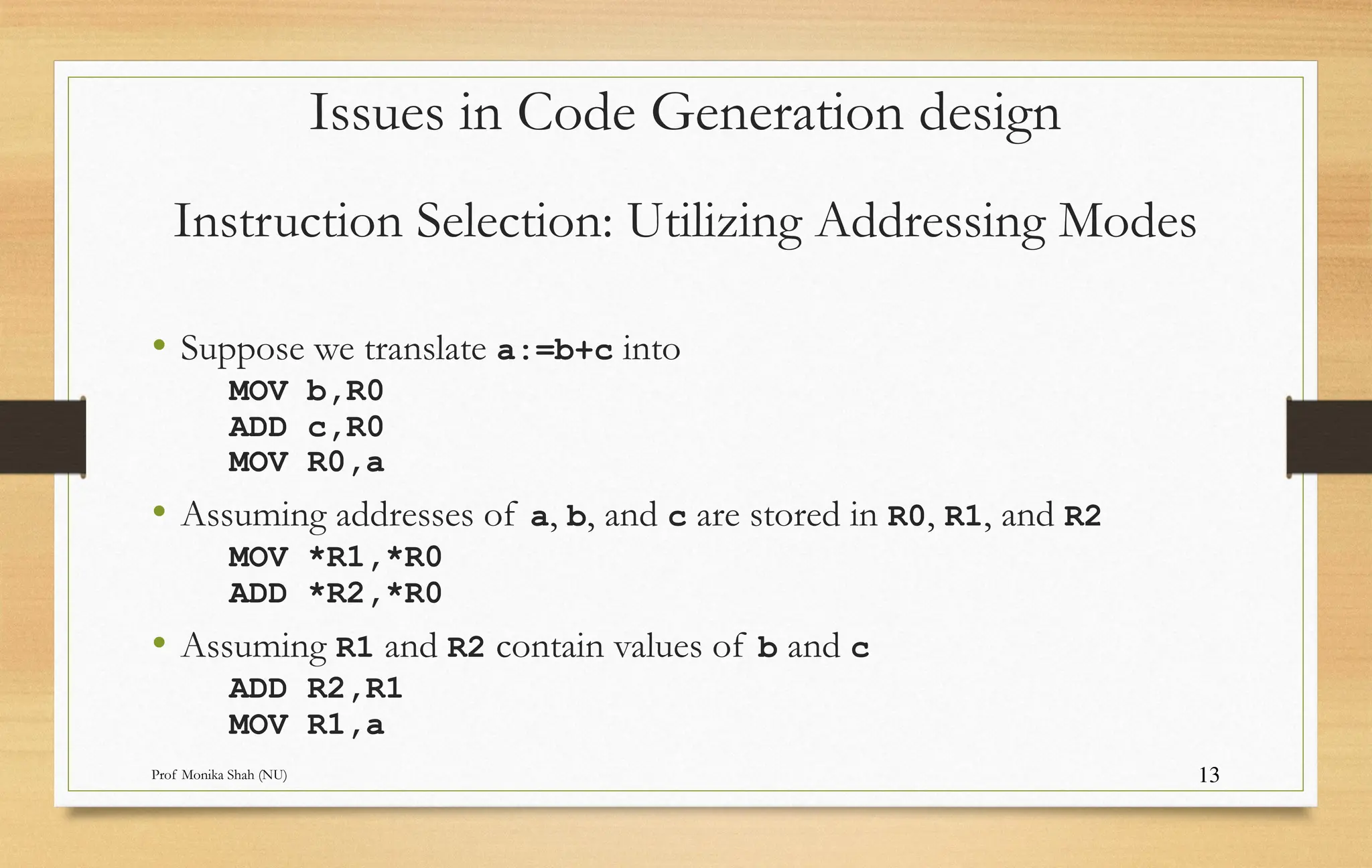

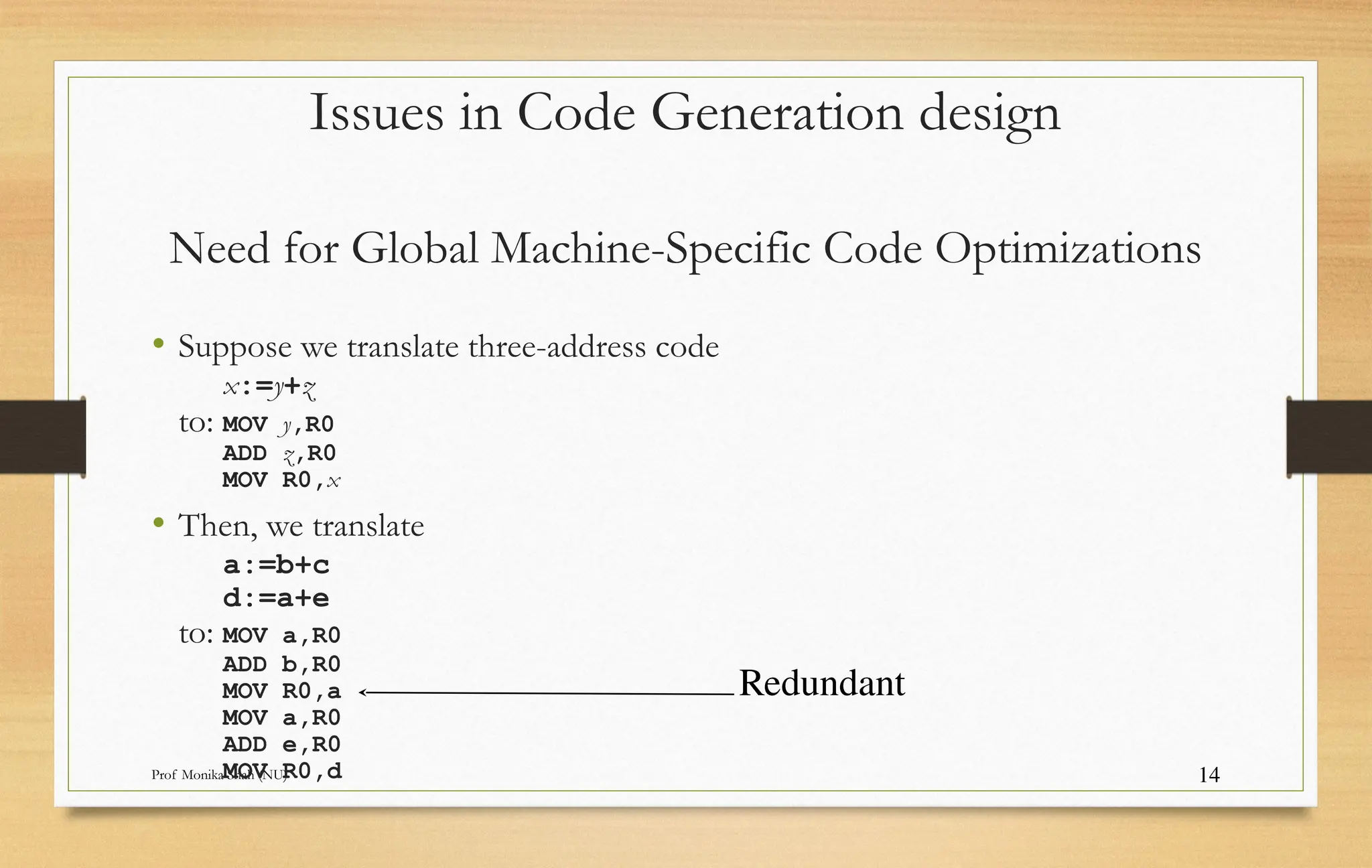

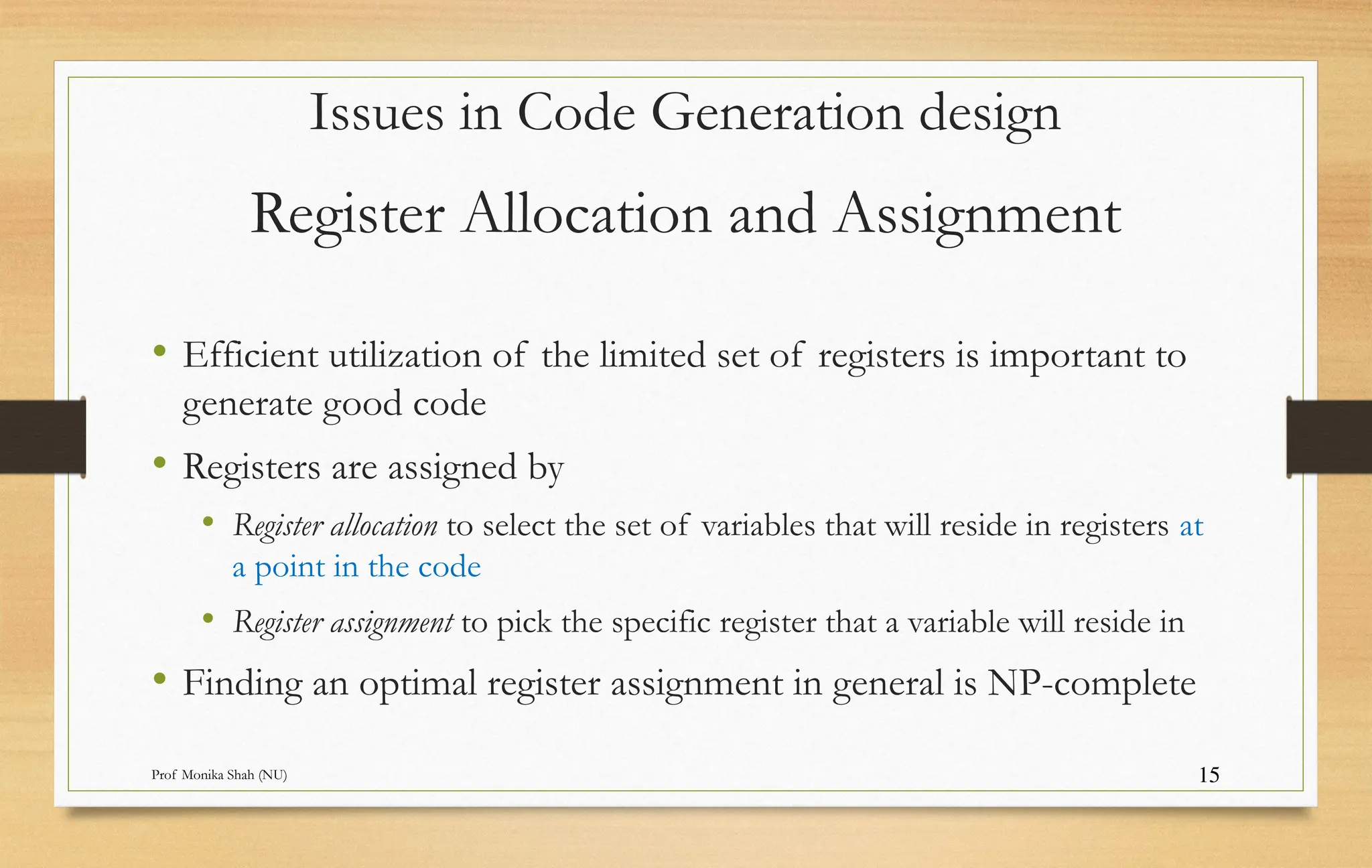

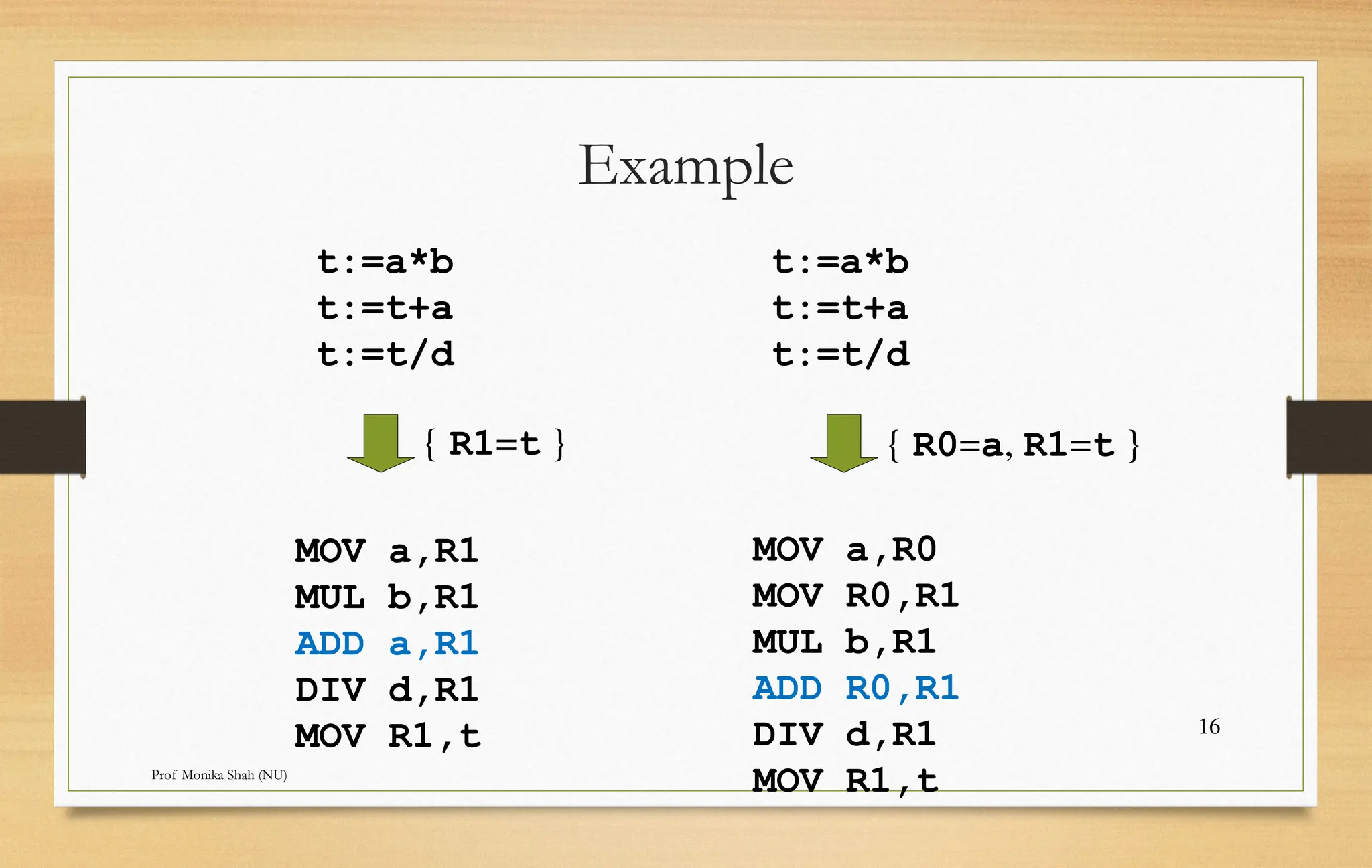

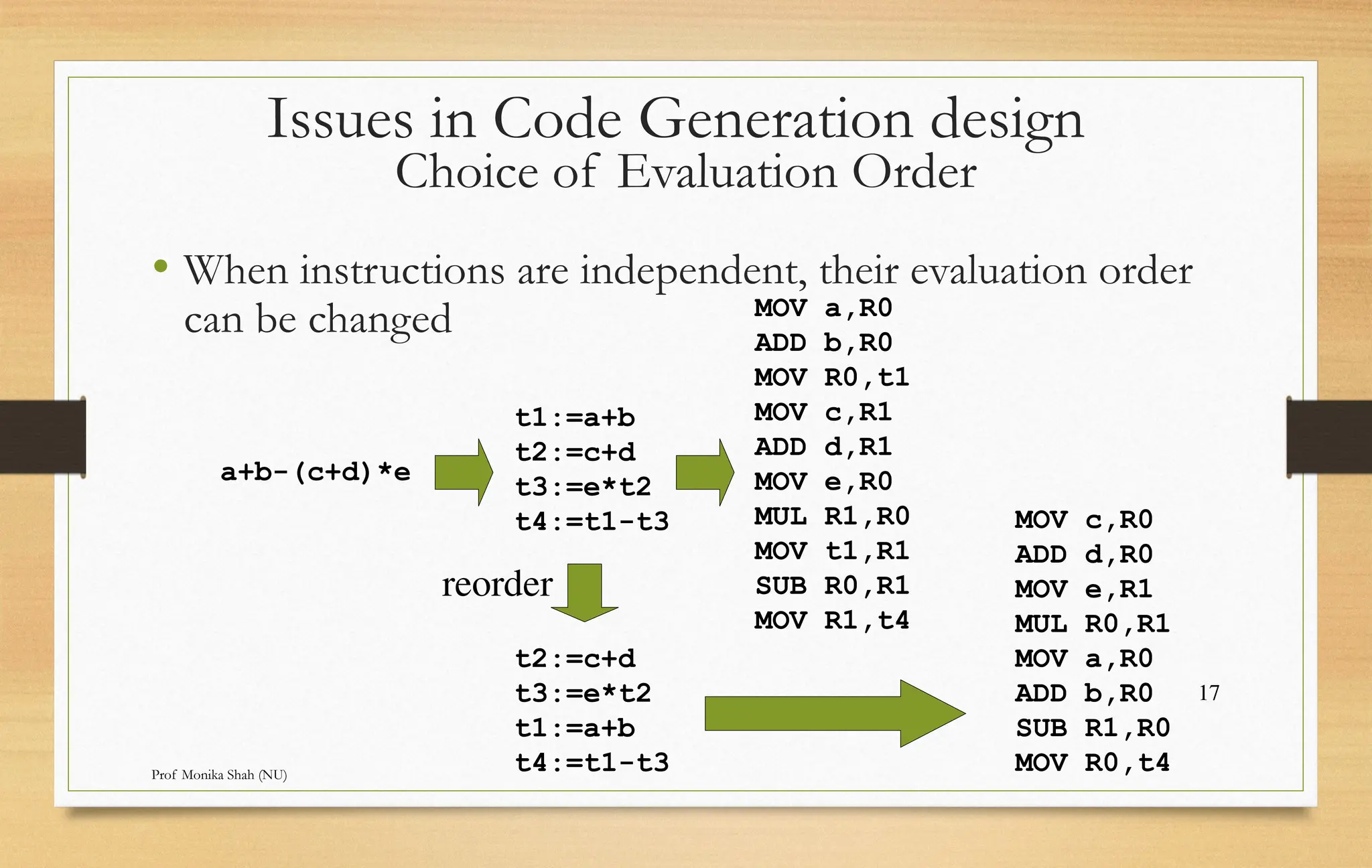

The document outlines the process of code generation in compiler construction, detailing important functionalities such as instruction selection, register allocation, and instruction ordering. It also discusses design issues, including input requirements, target program variations, and the need for efficient resource utilization. The final output emphasizes key constraints and techniques for creating correct and optimized executable code.