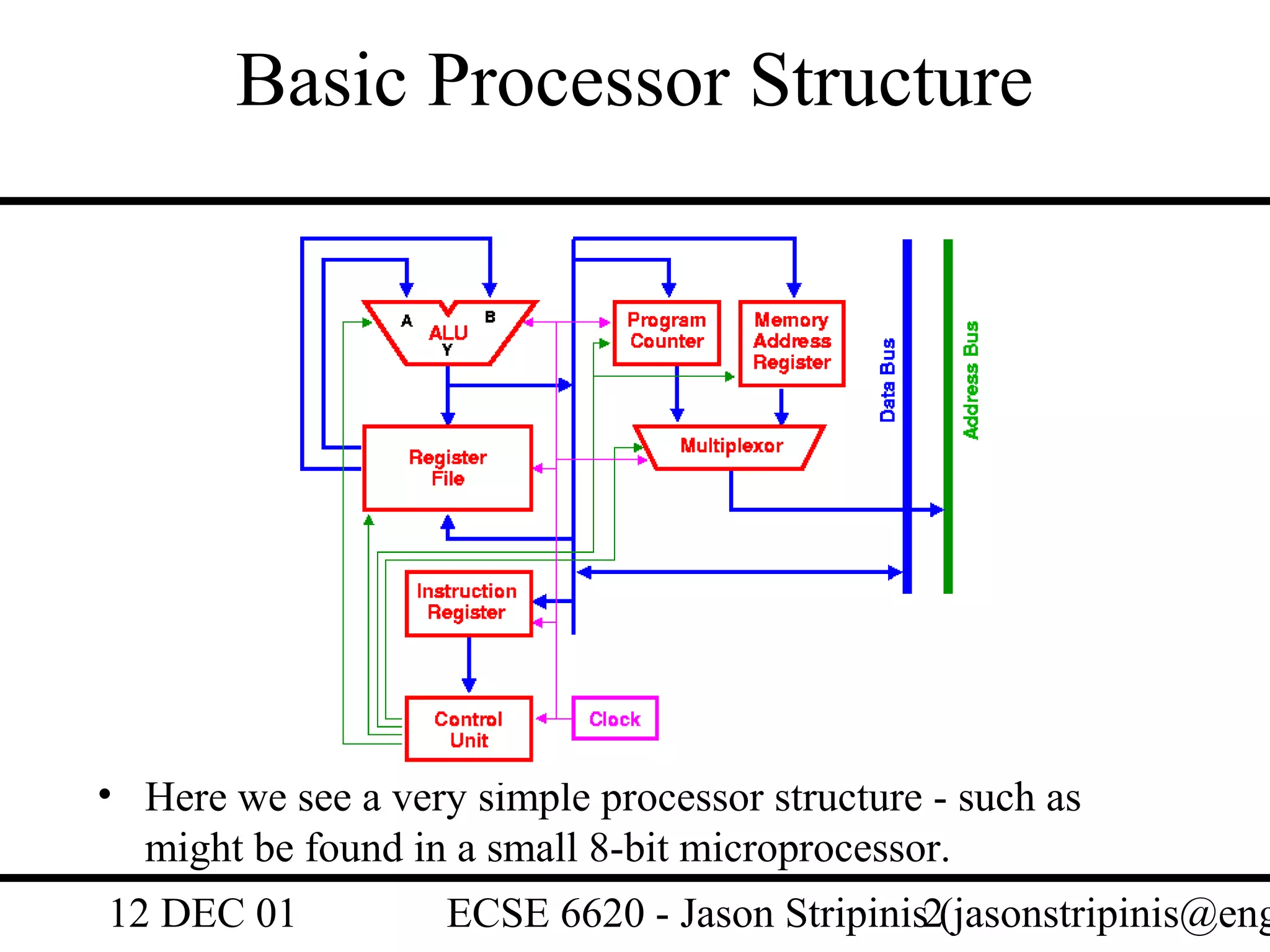

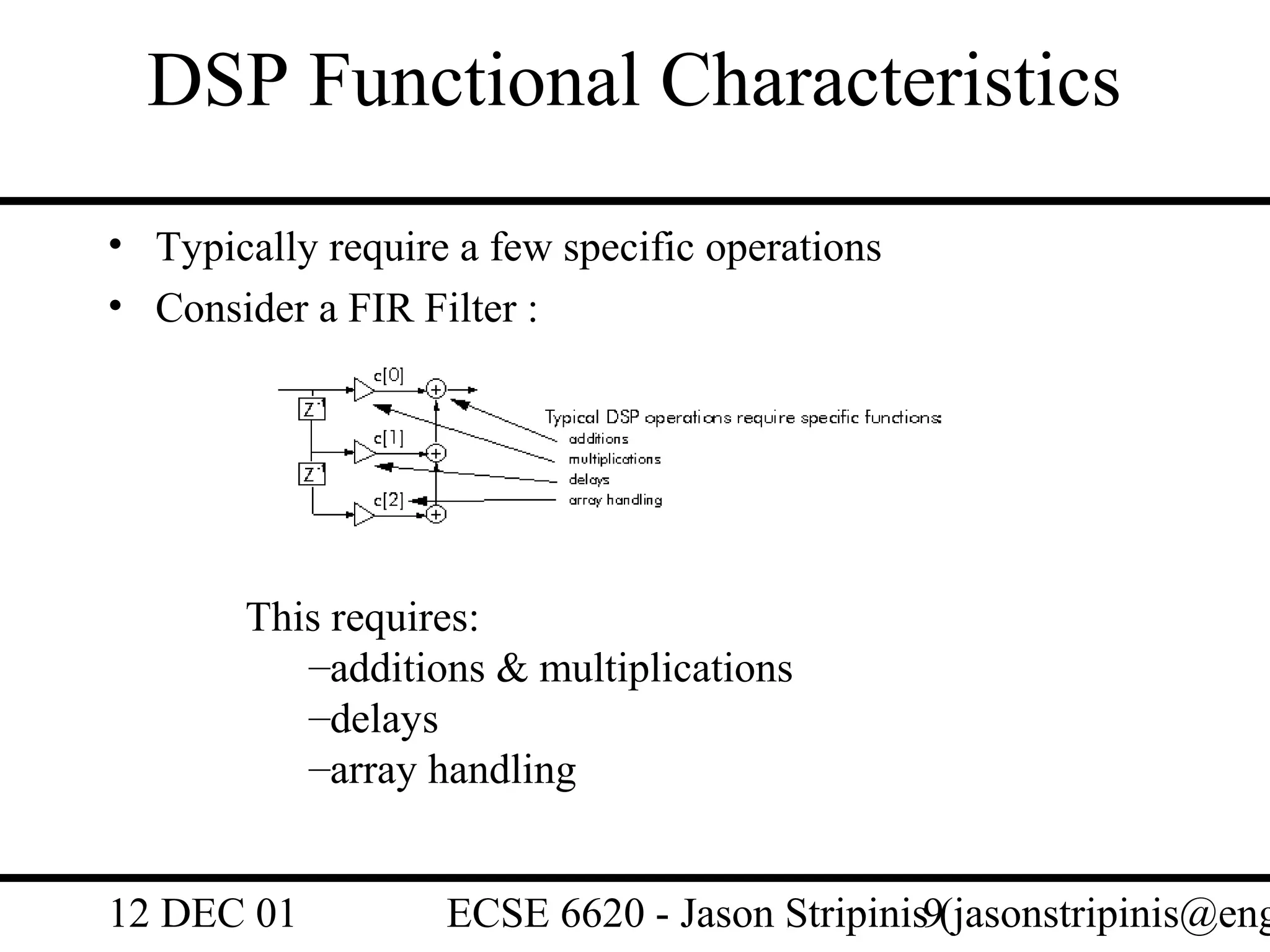

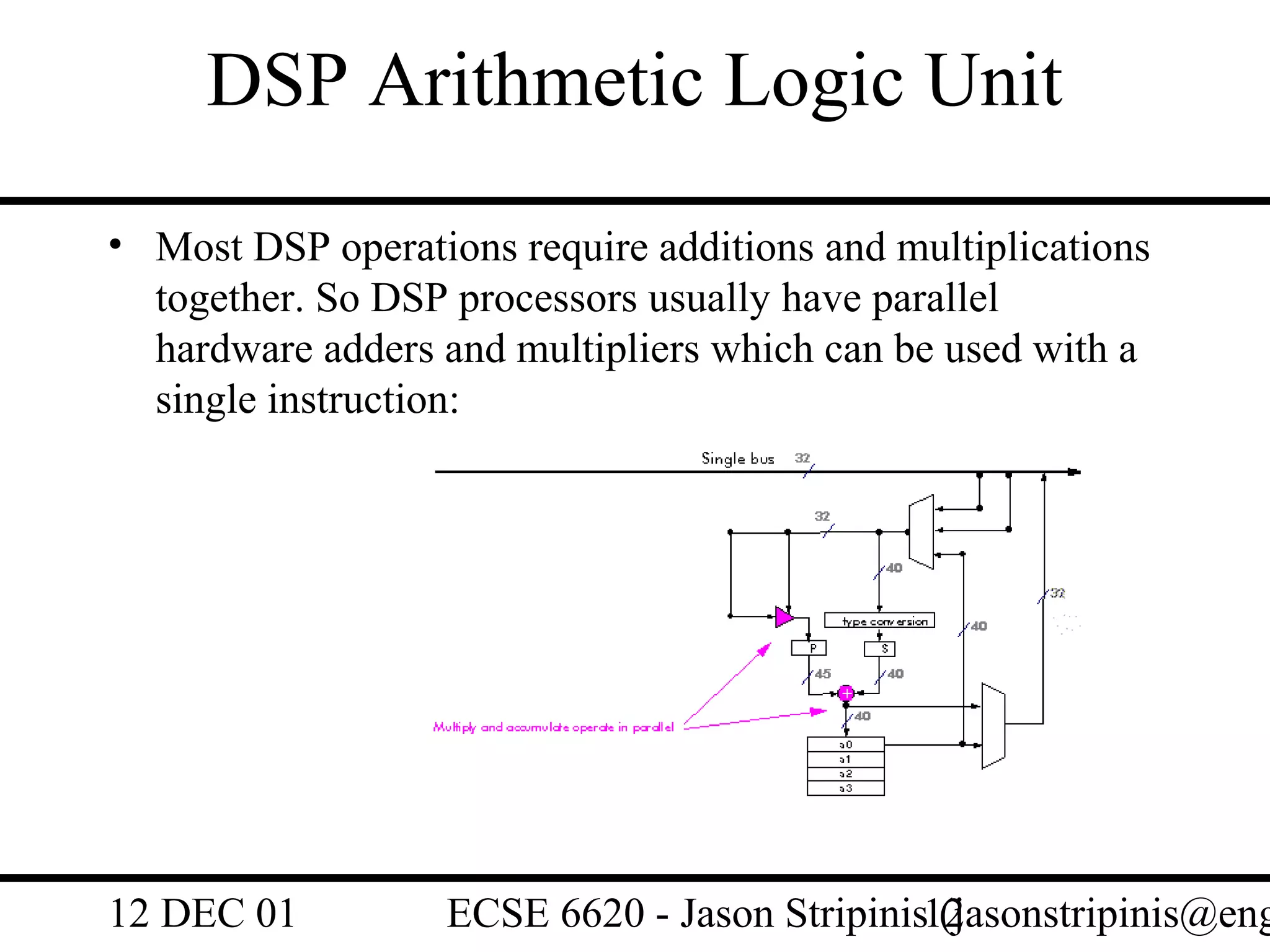

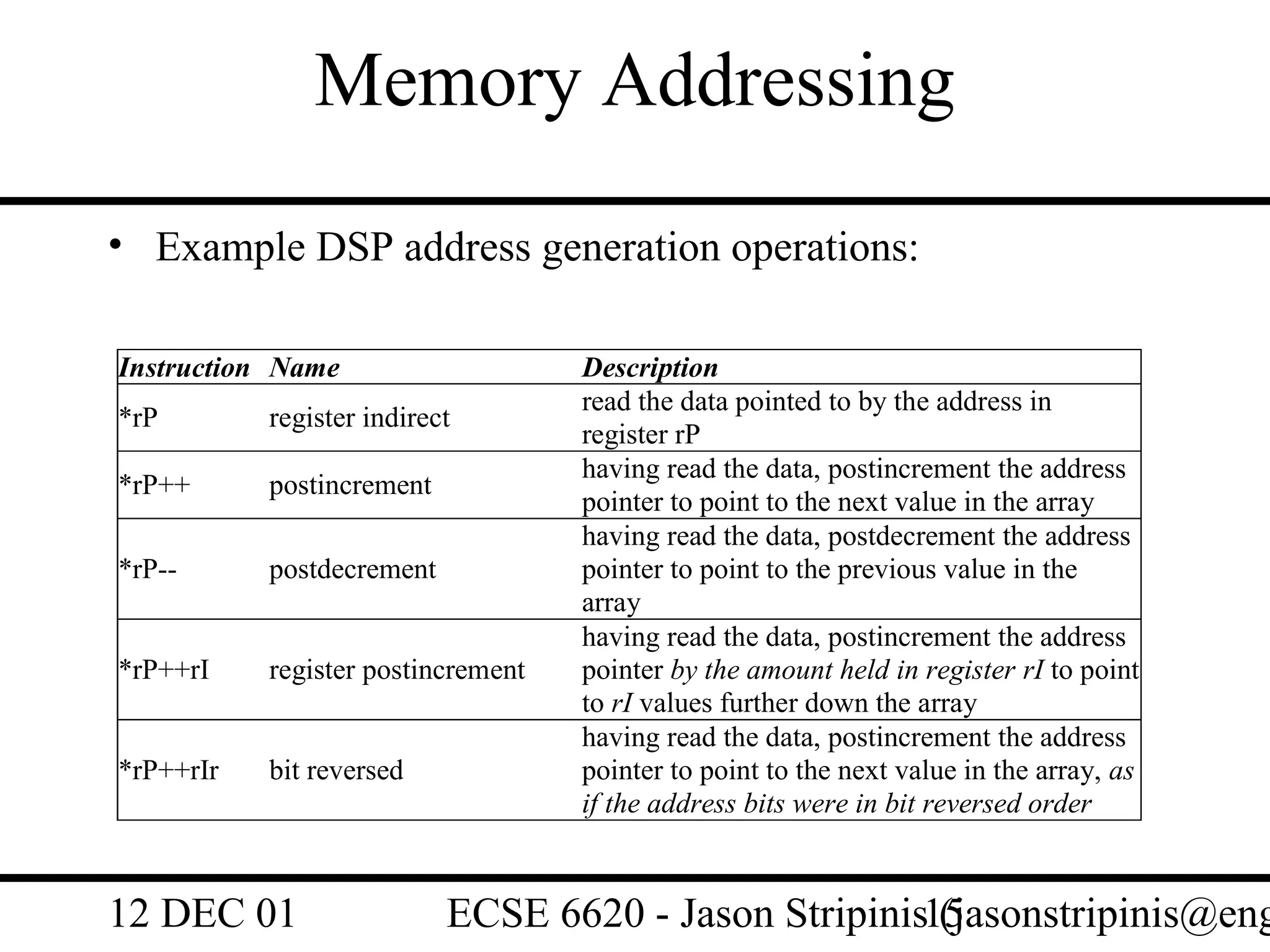

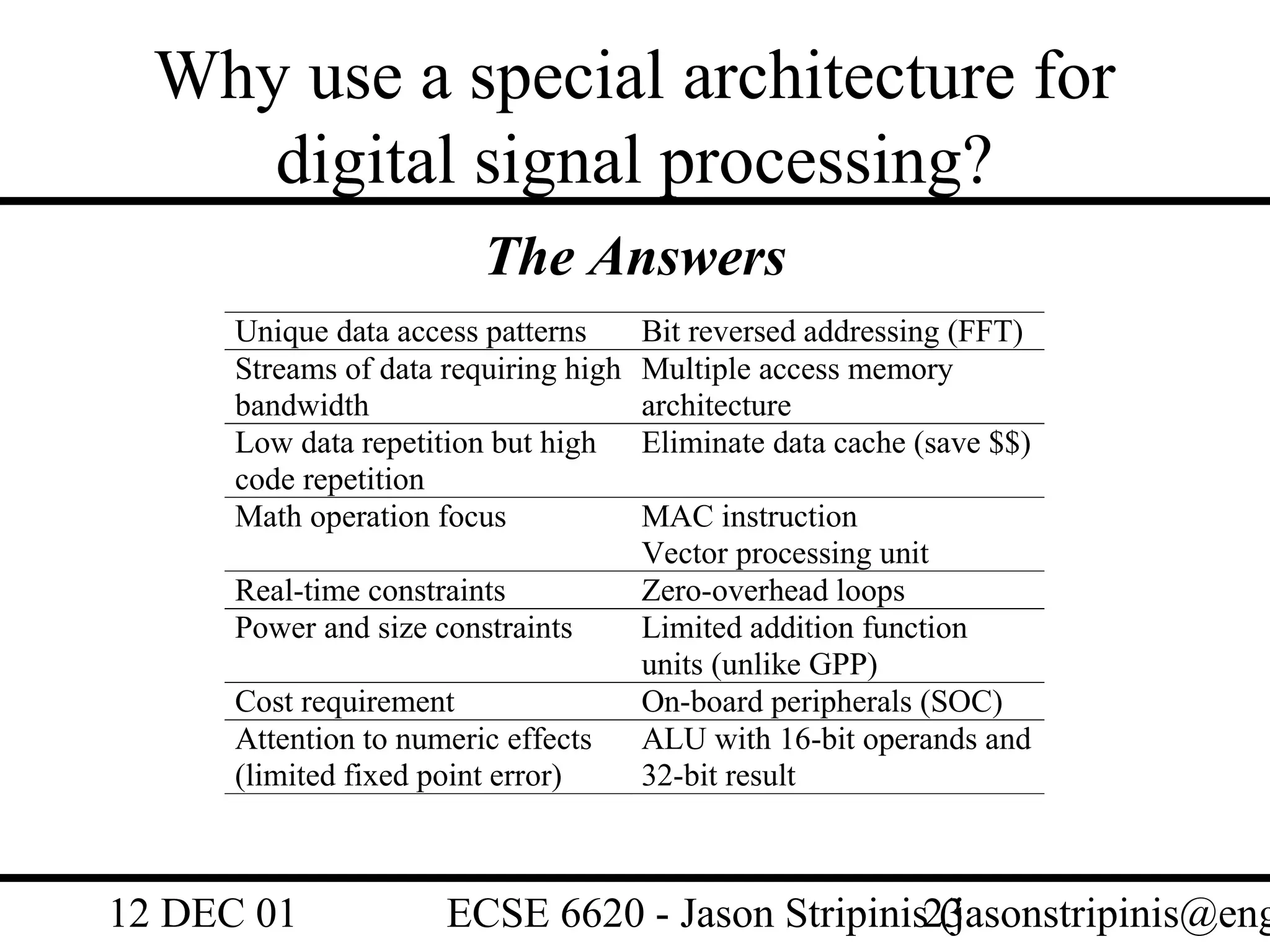

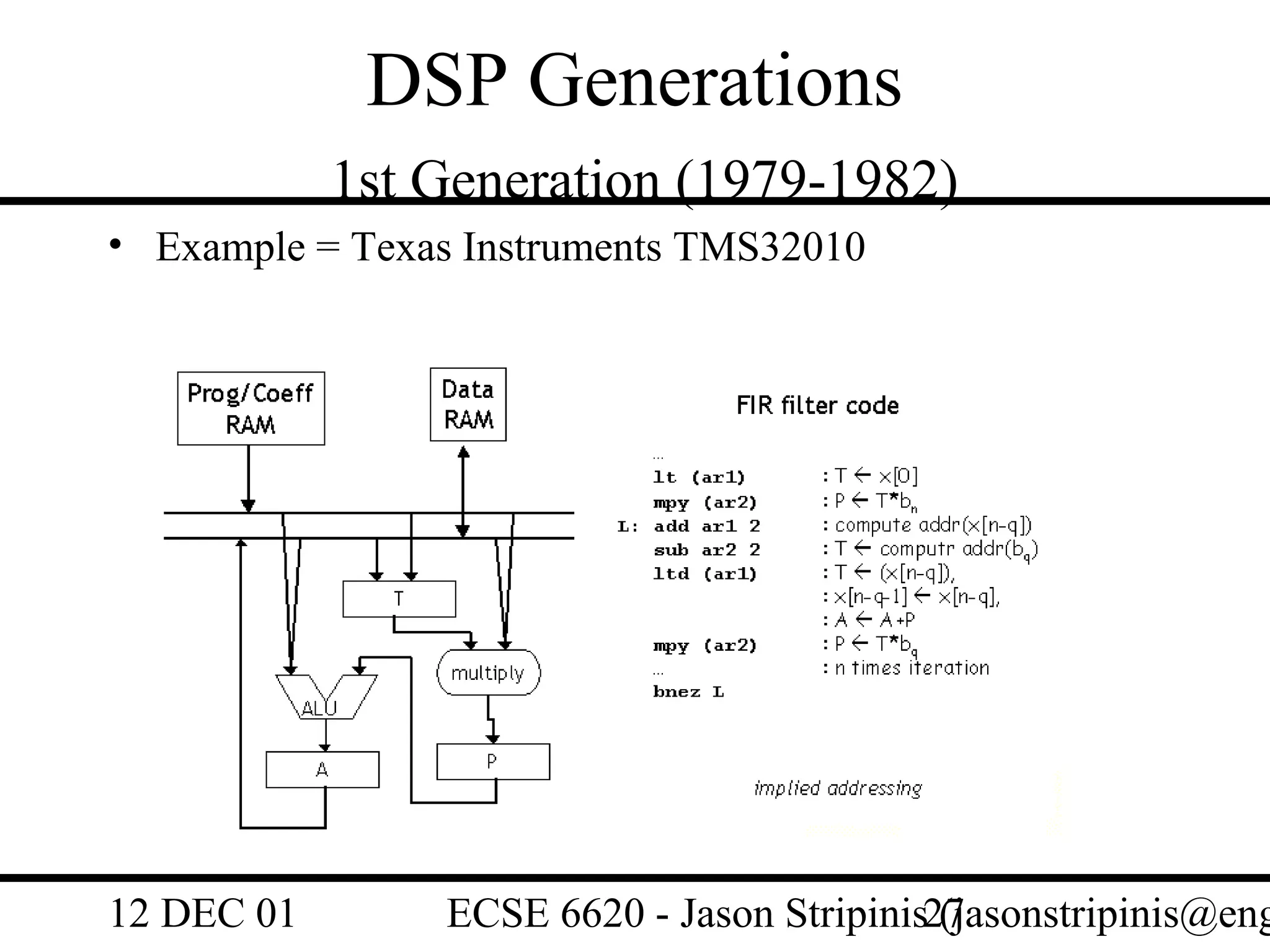

This document discusses DSP architectures and their suitability for digital signal processing. It describes the basic components of a processor and how DSP processors are optimized for common DSP operations like multiplication, addition, delays, and array handling. It explains features like parallel multiply-add units, specialized register structures, and efficient memory addressing modes. Finally, it covers different memory architectures for DSPs, including the Harvard architecture and modified von Neumann architecture, which allow multiple simultaneous memory accesses needed for DSP algorithms.