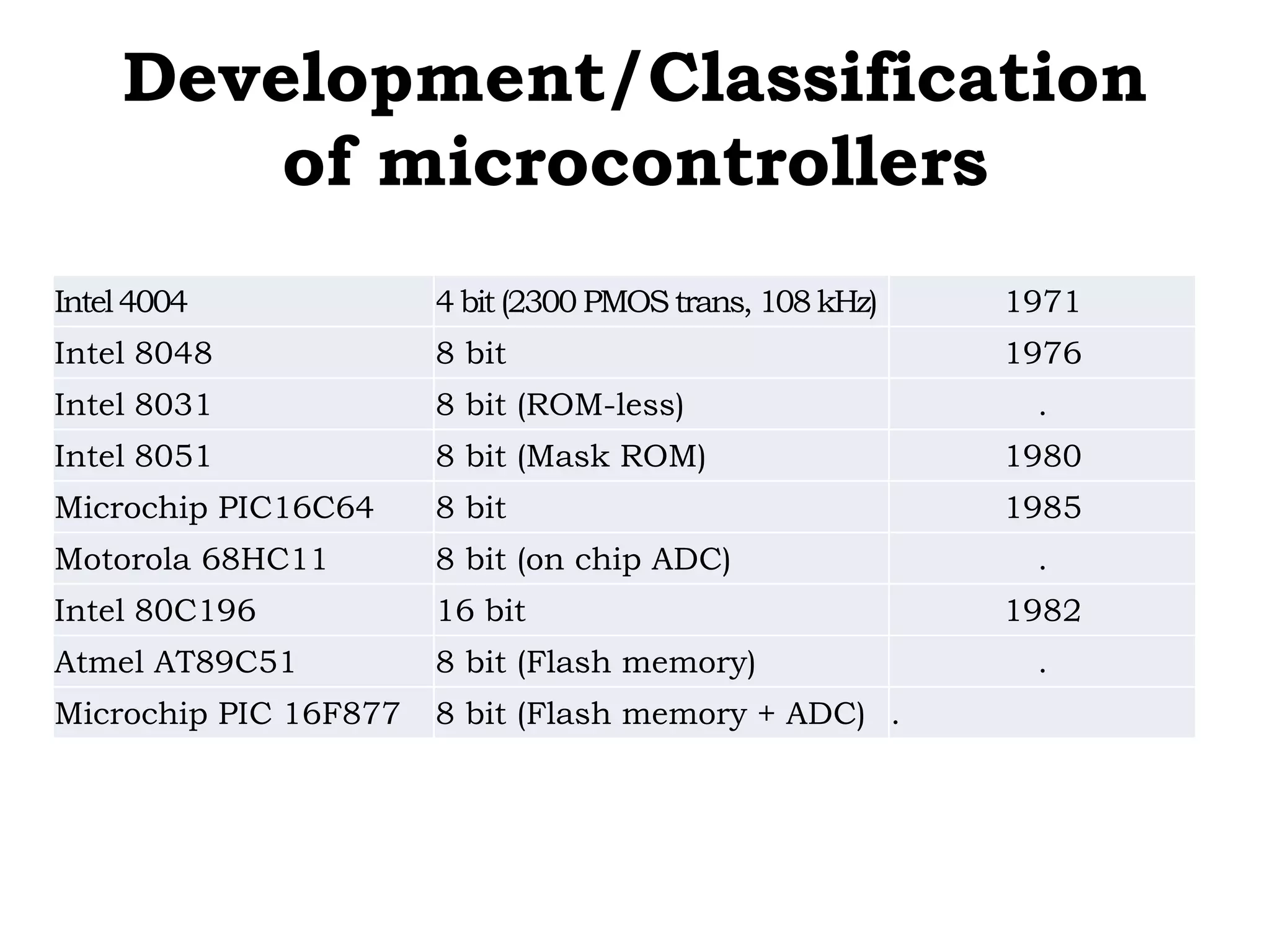

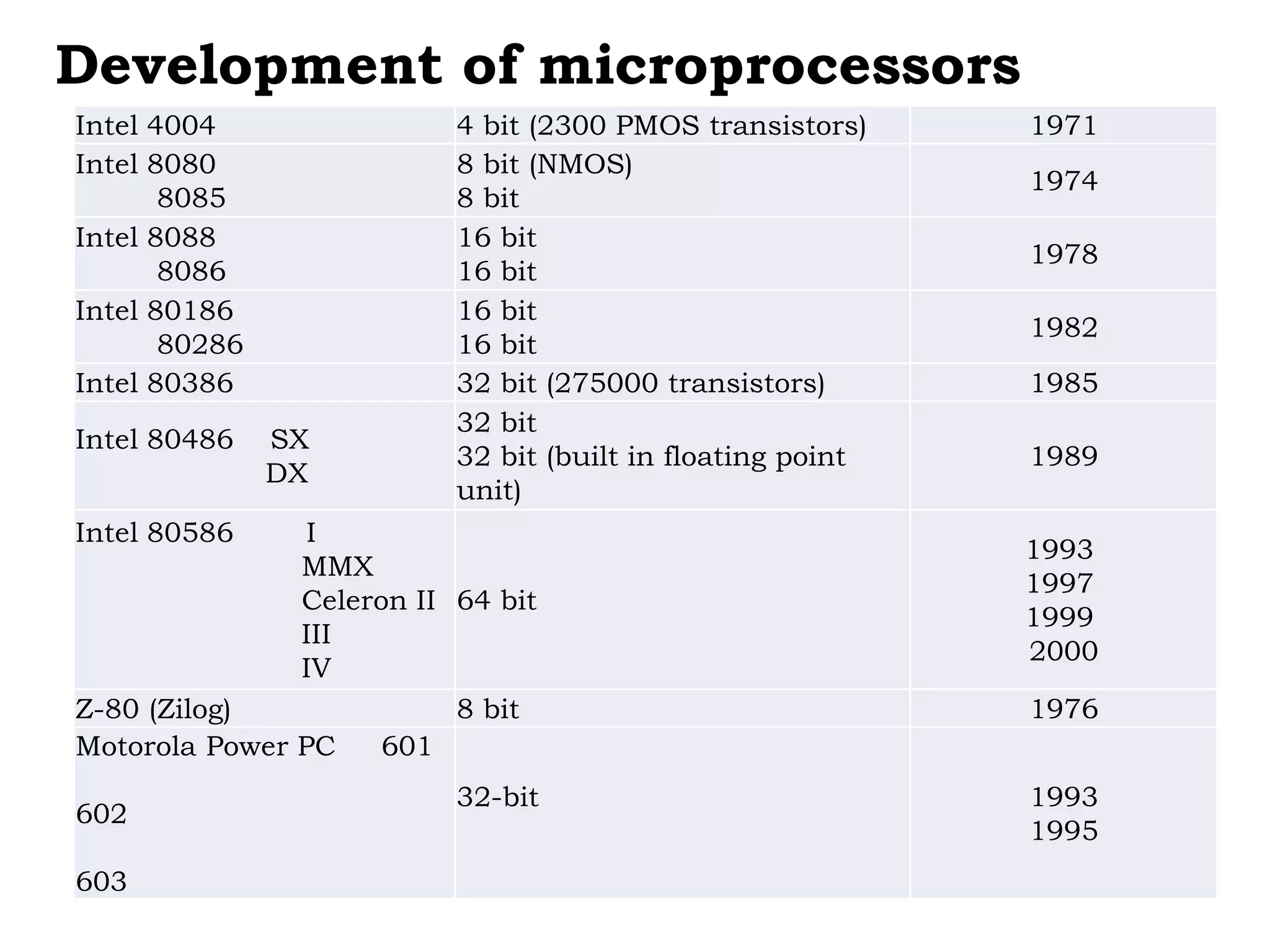

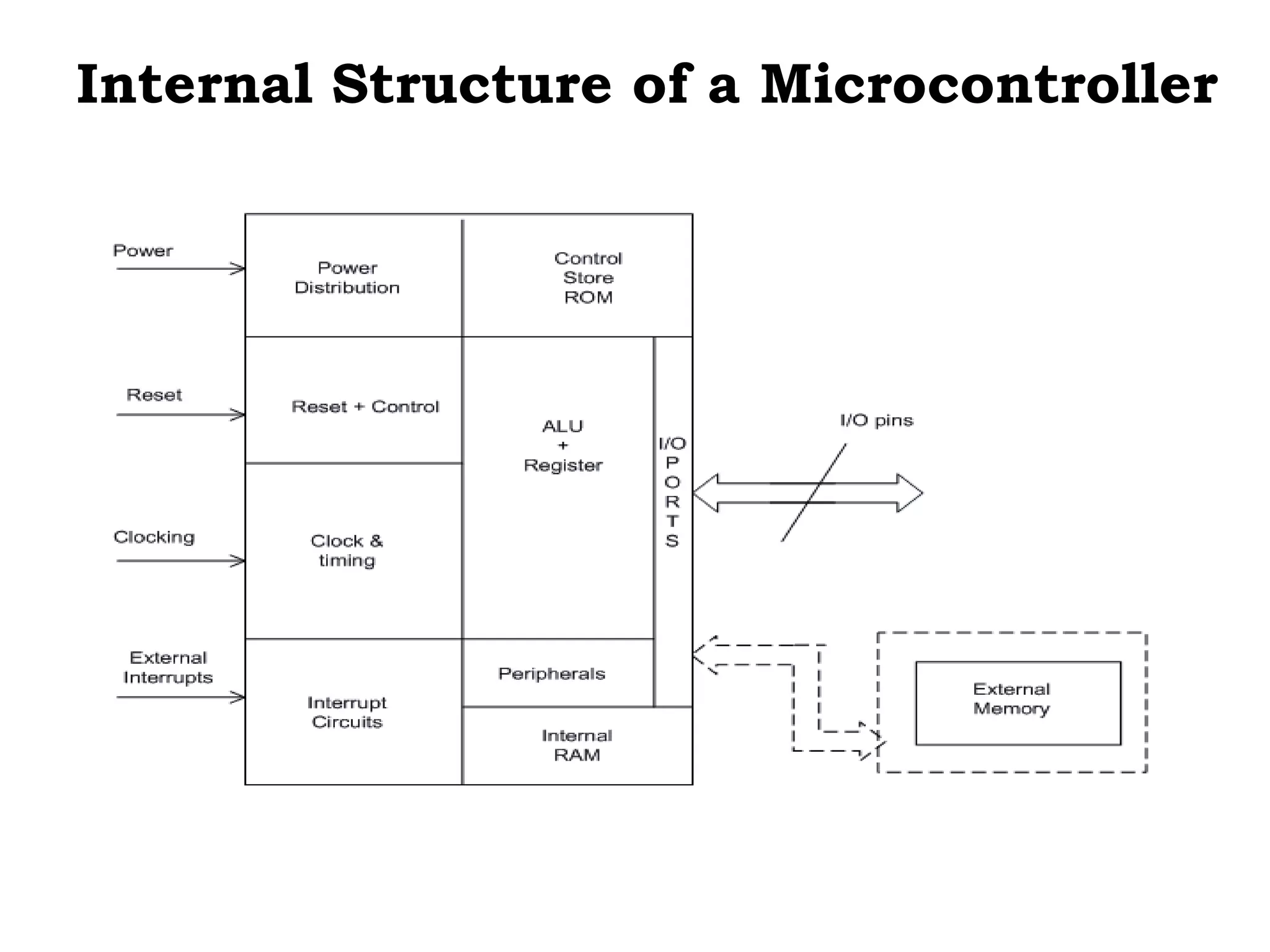

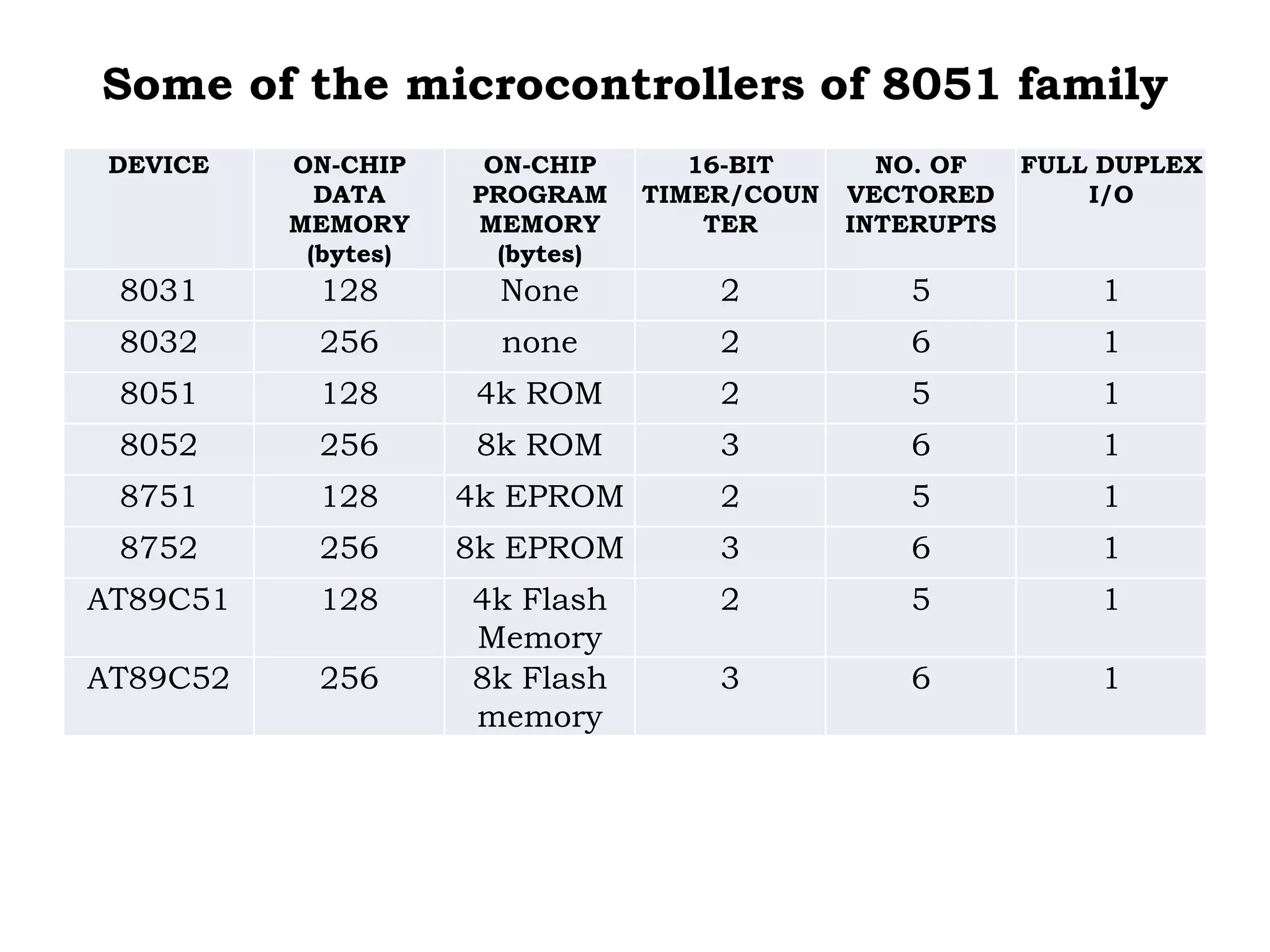

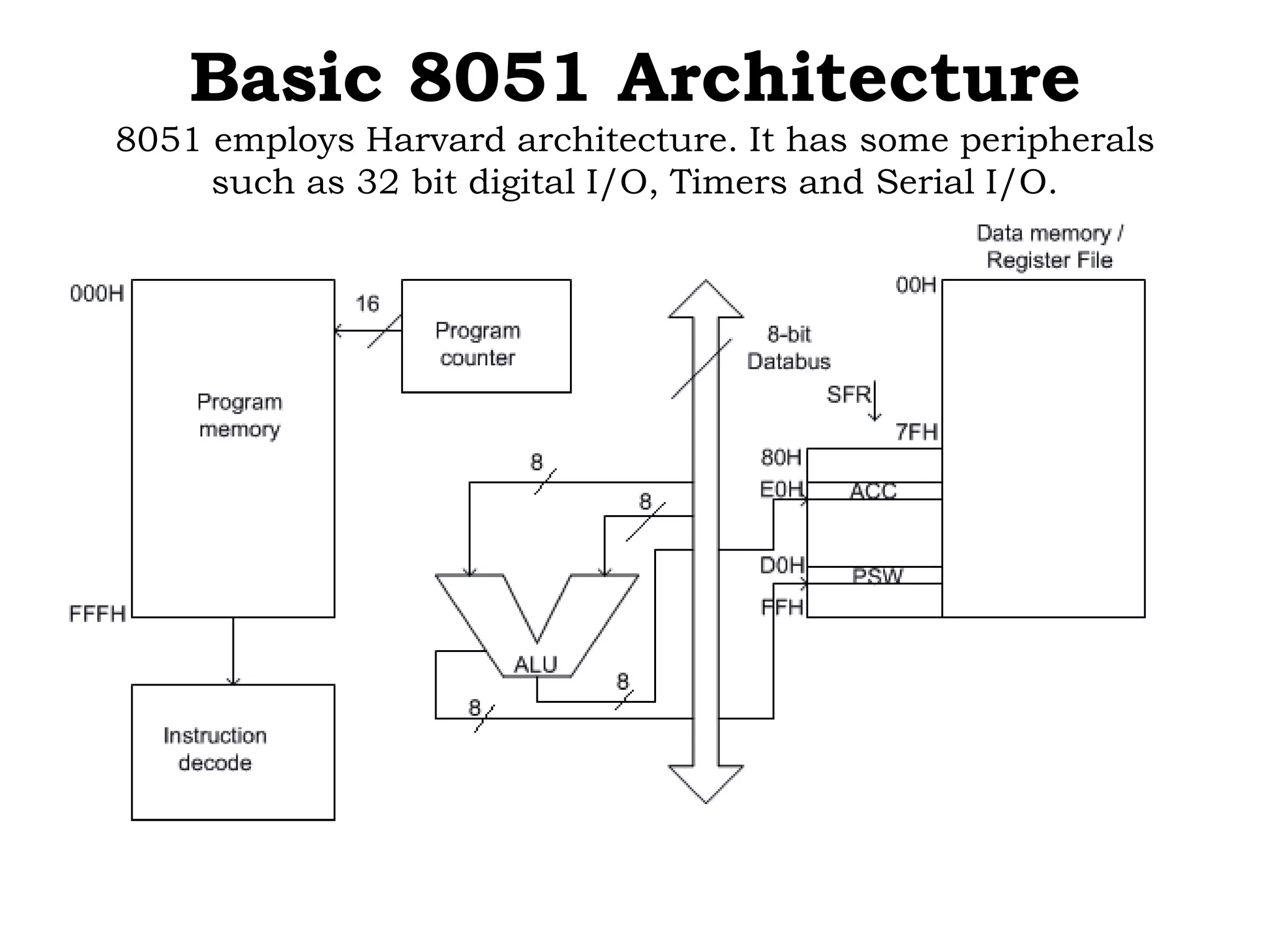

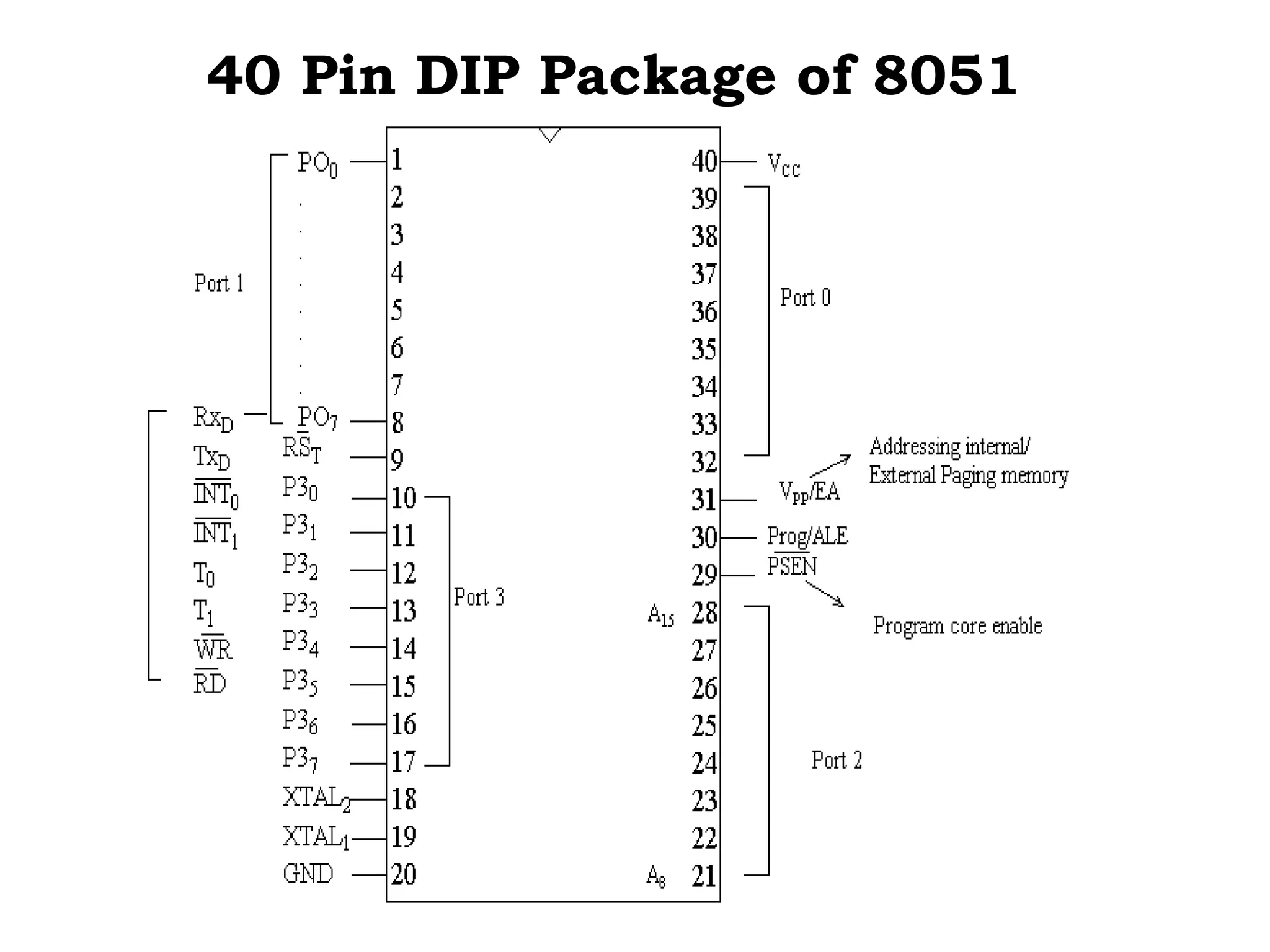

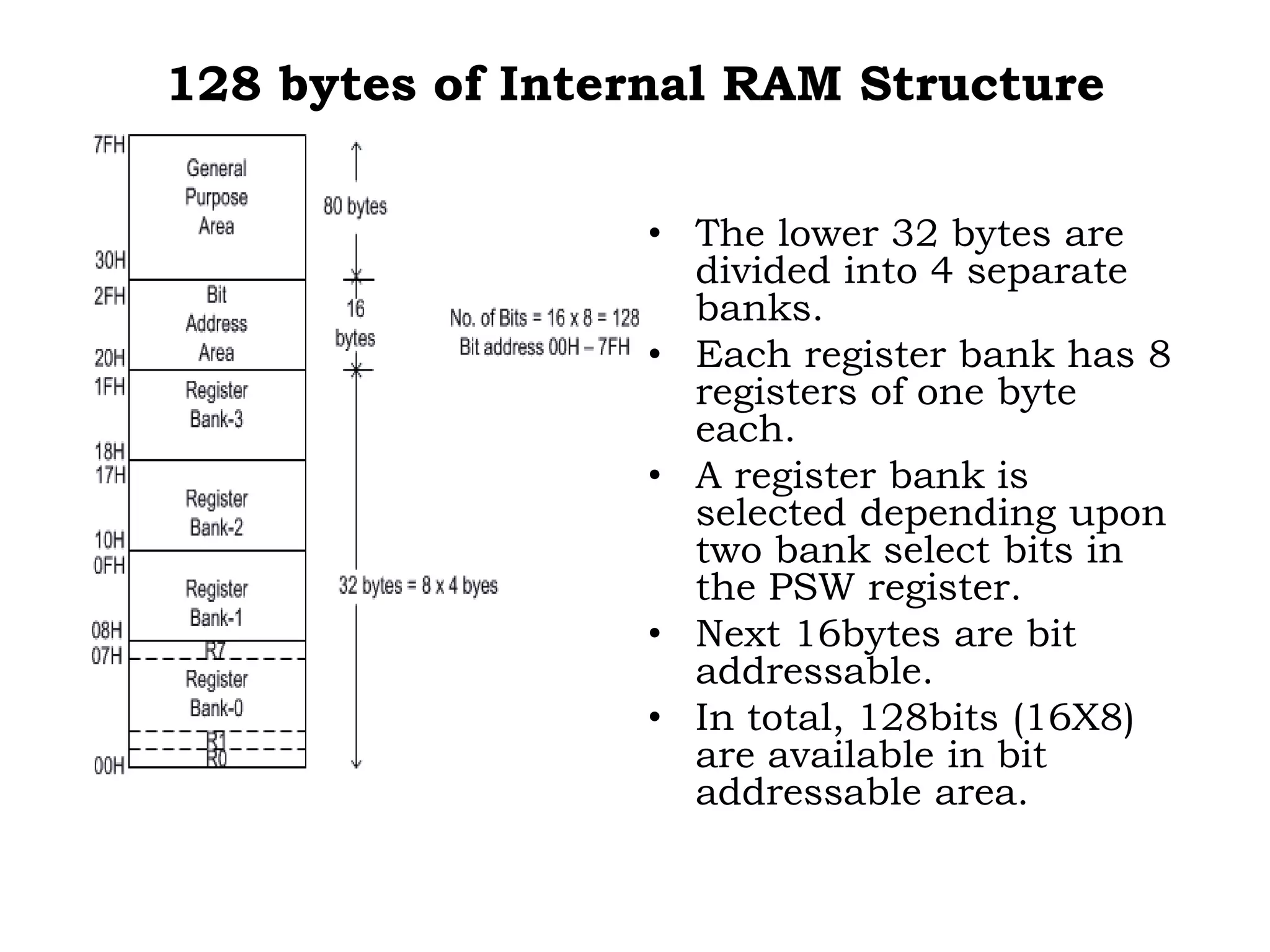

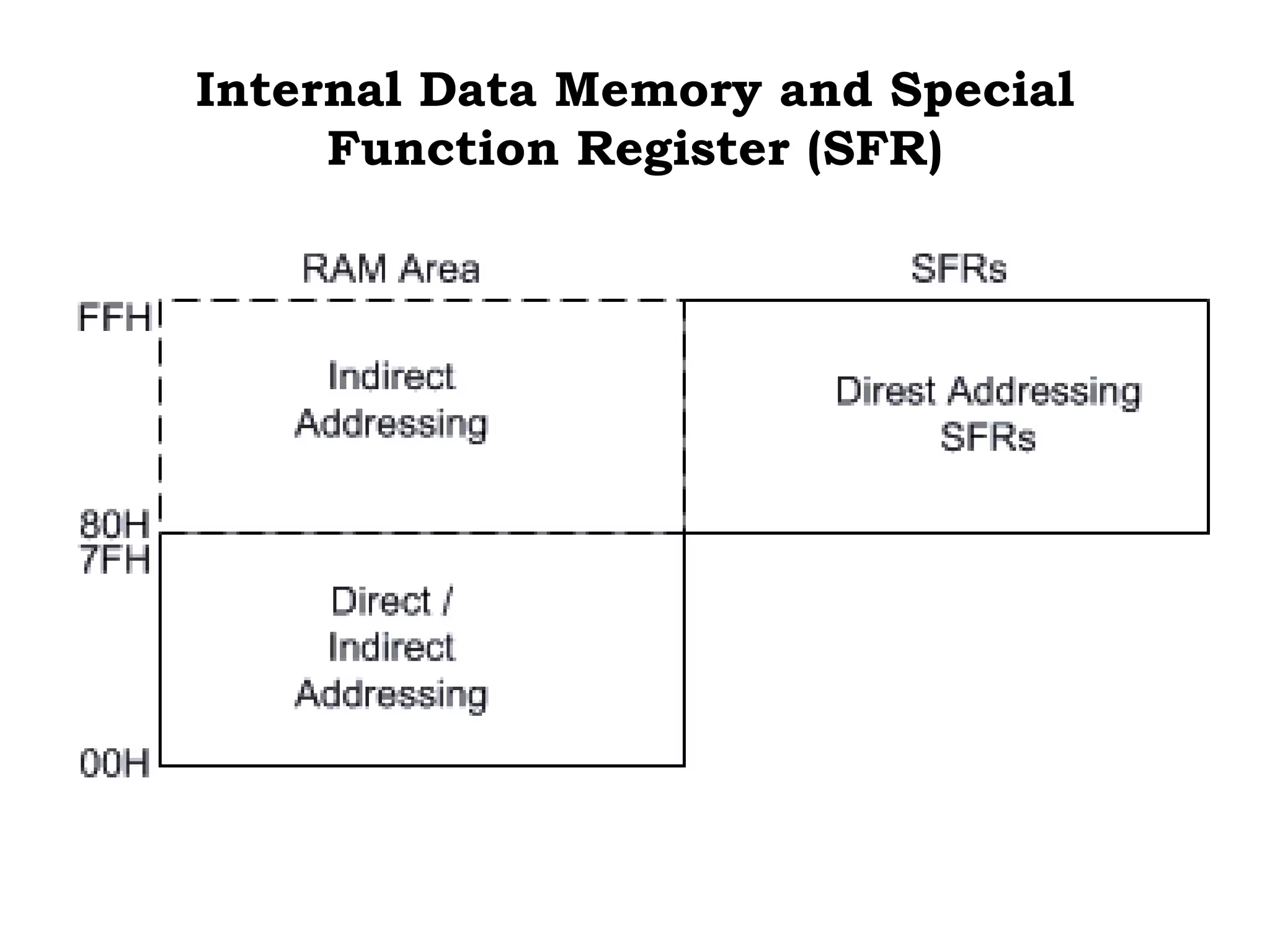

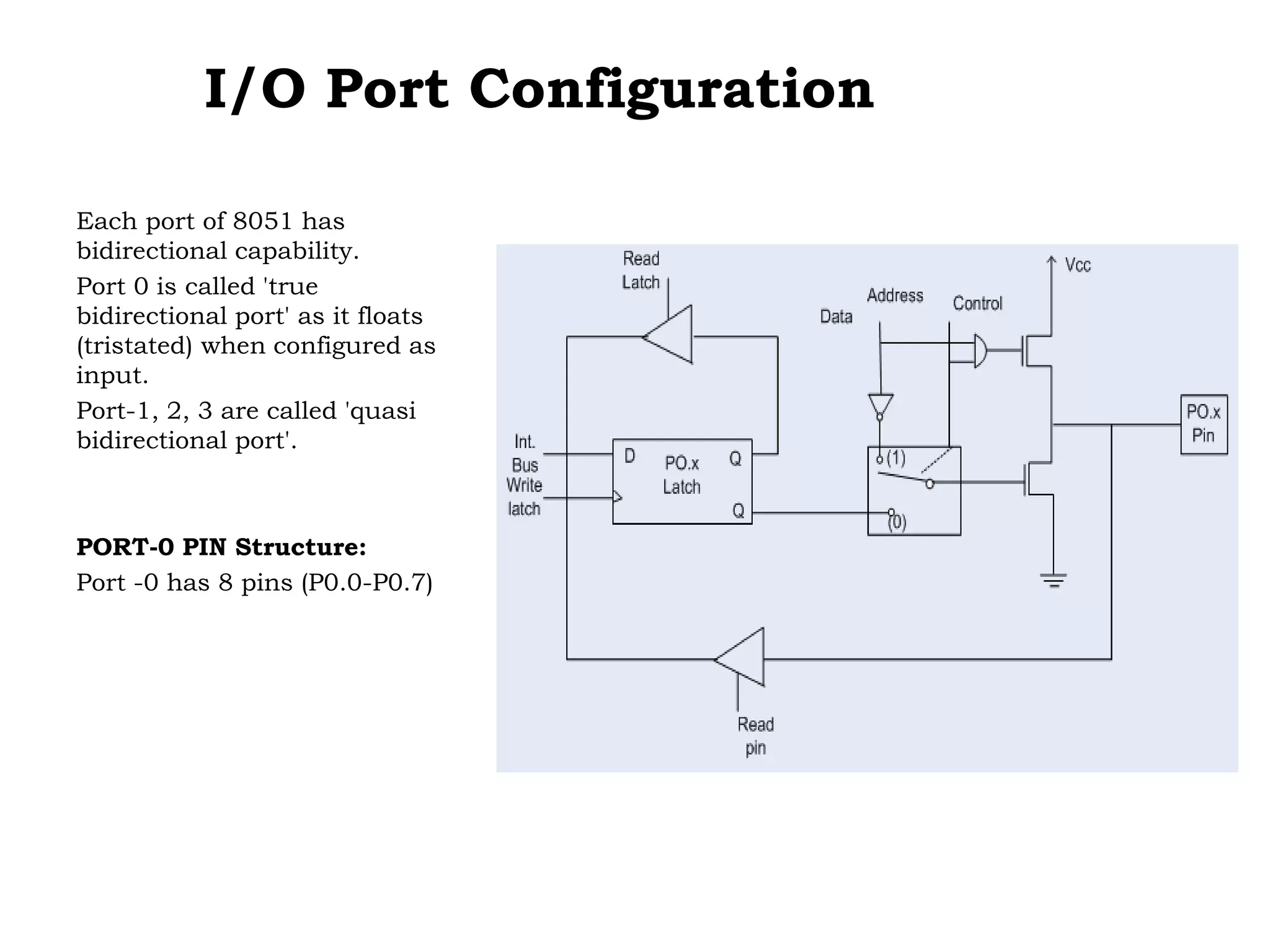

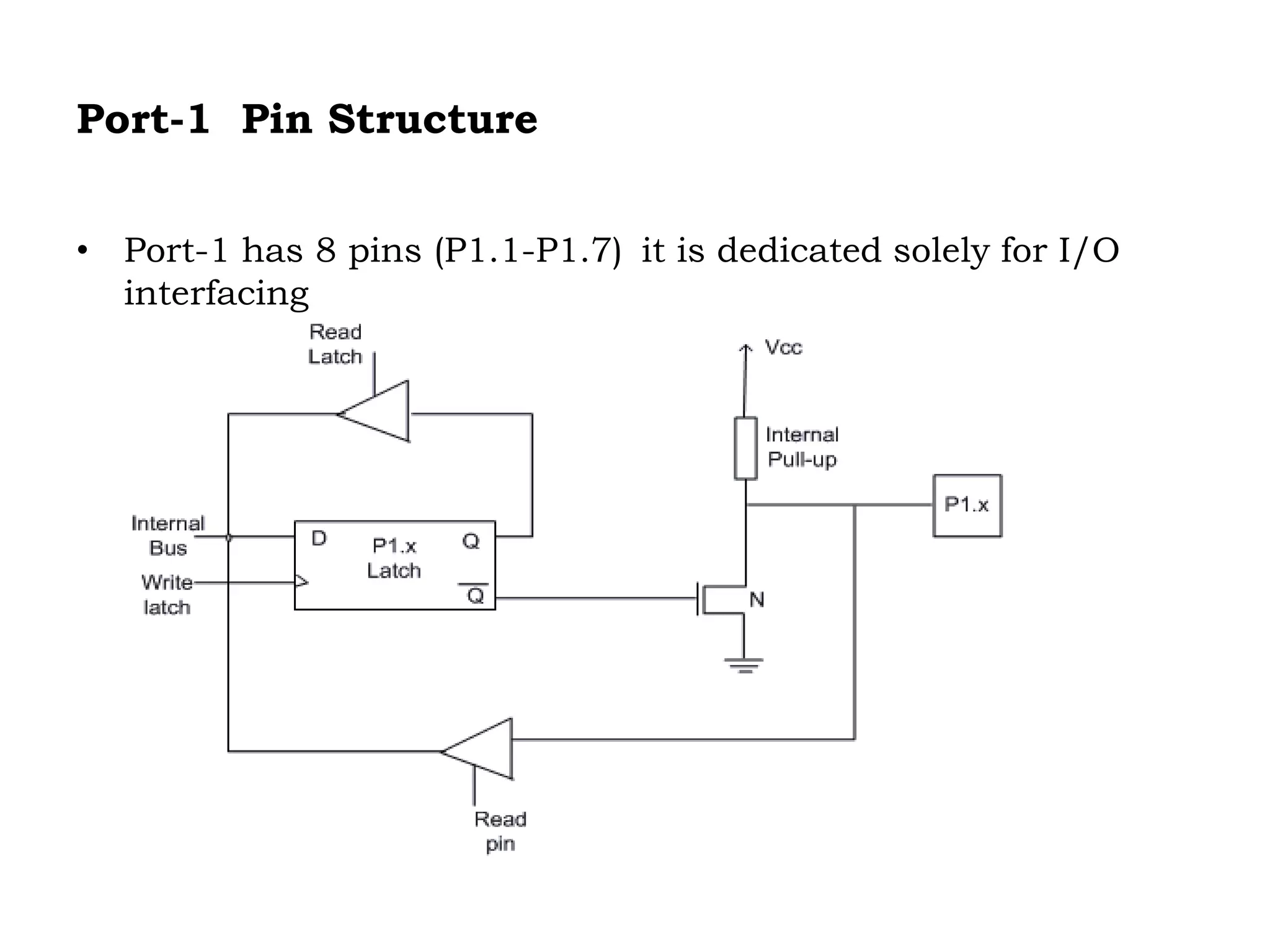

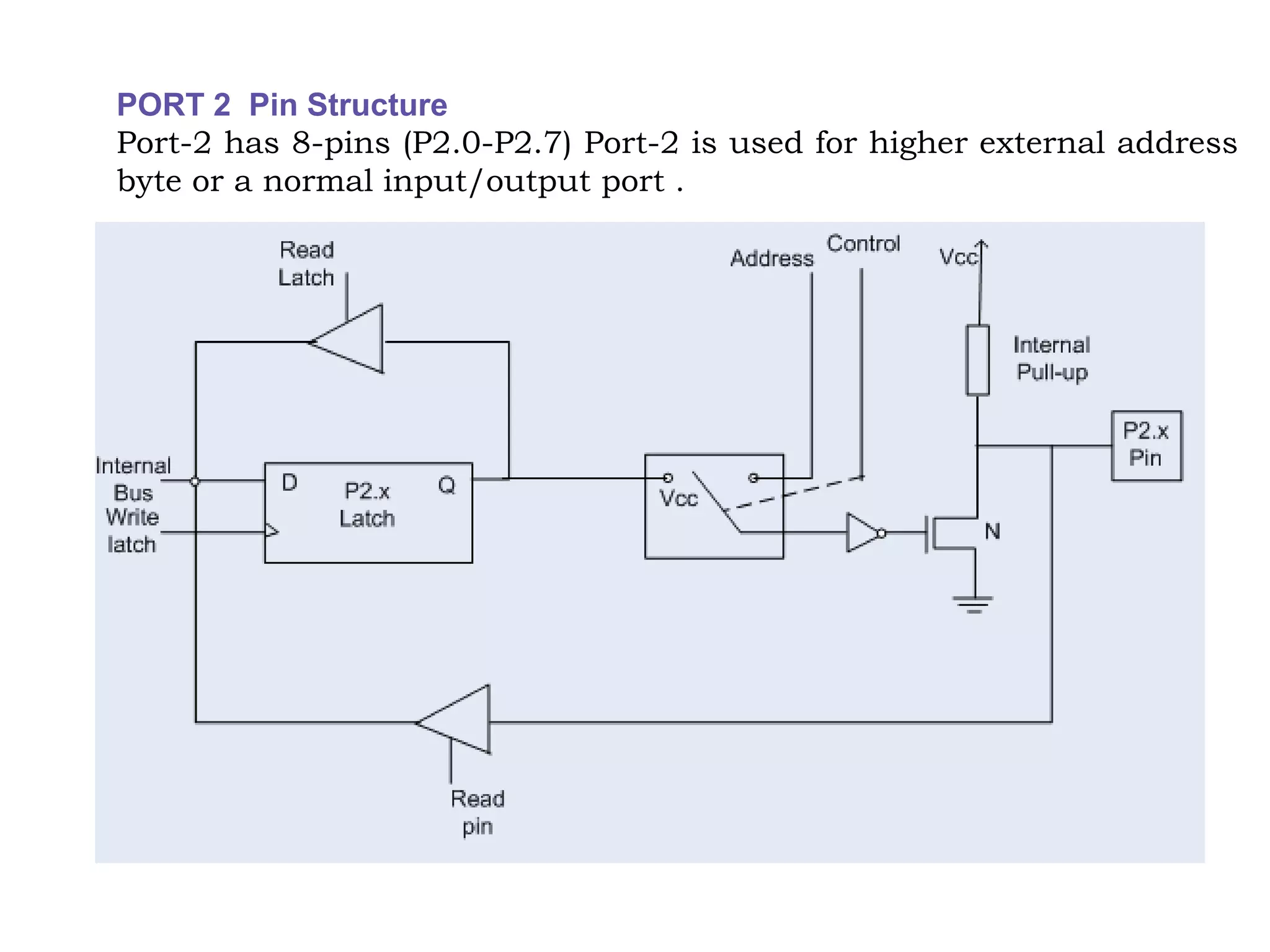

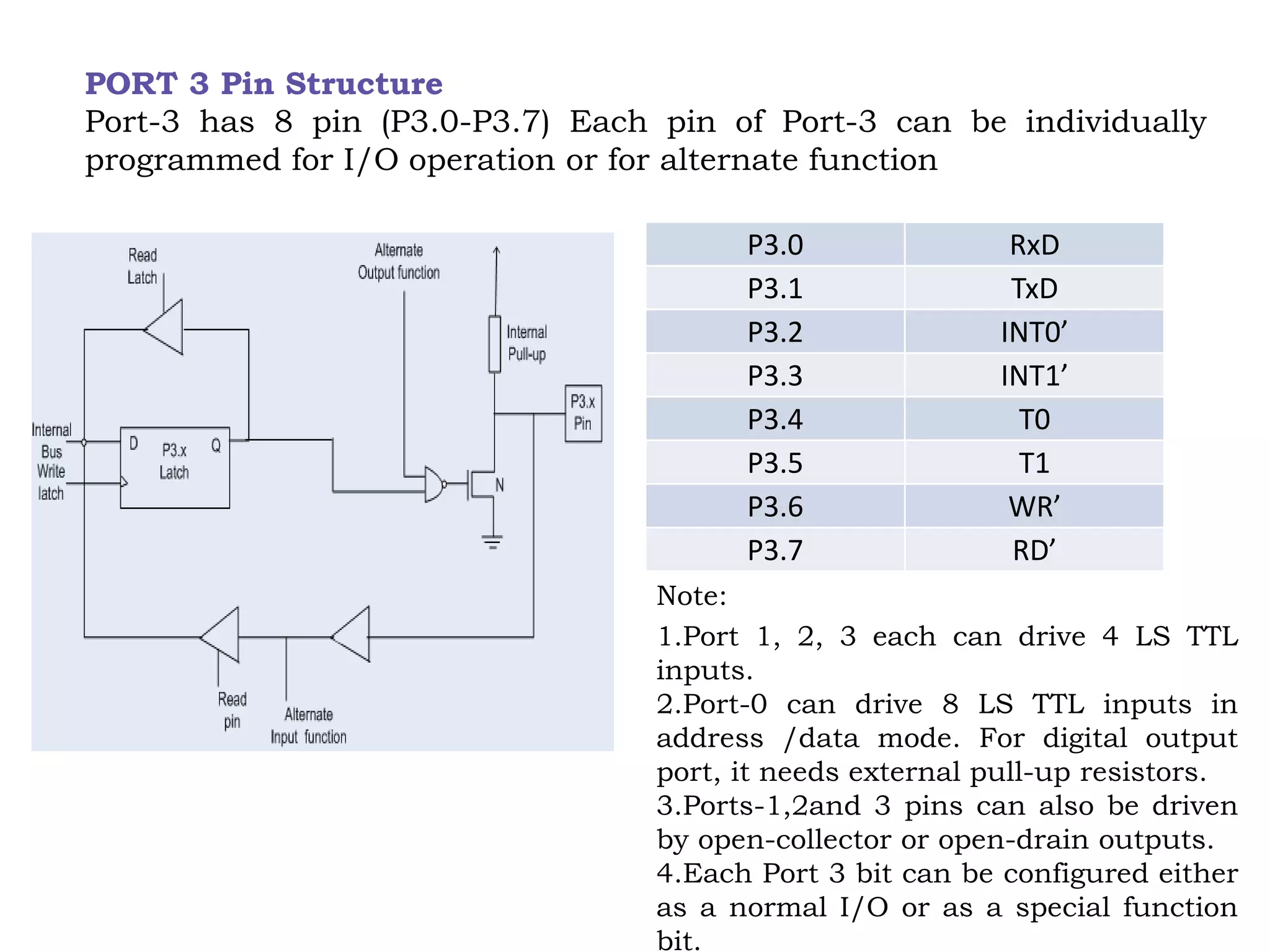

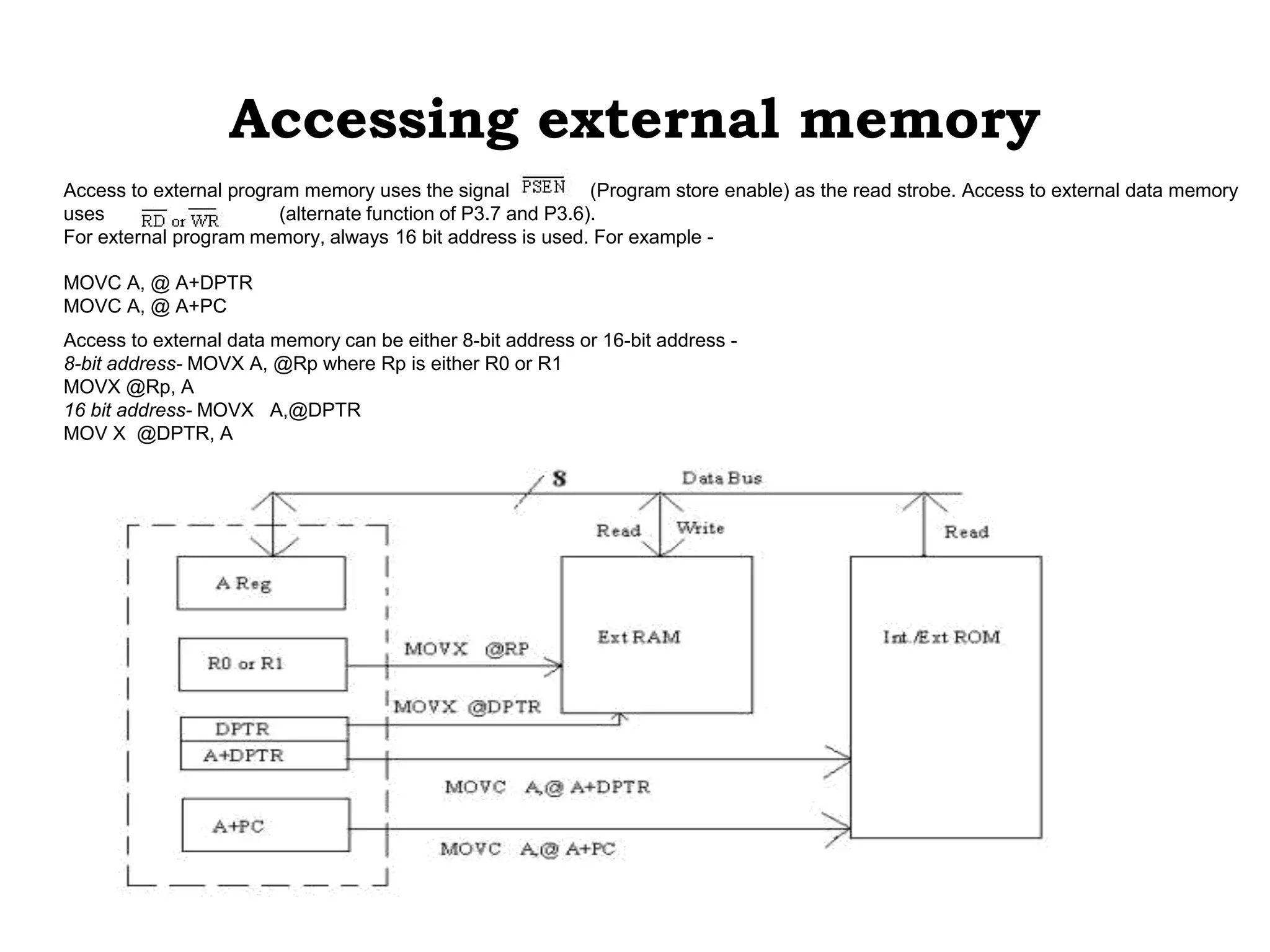

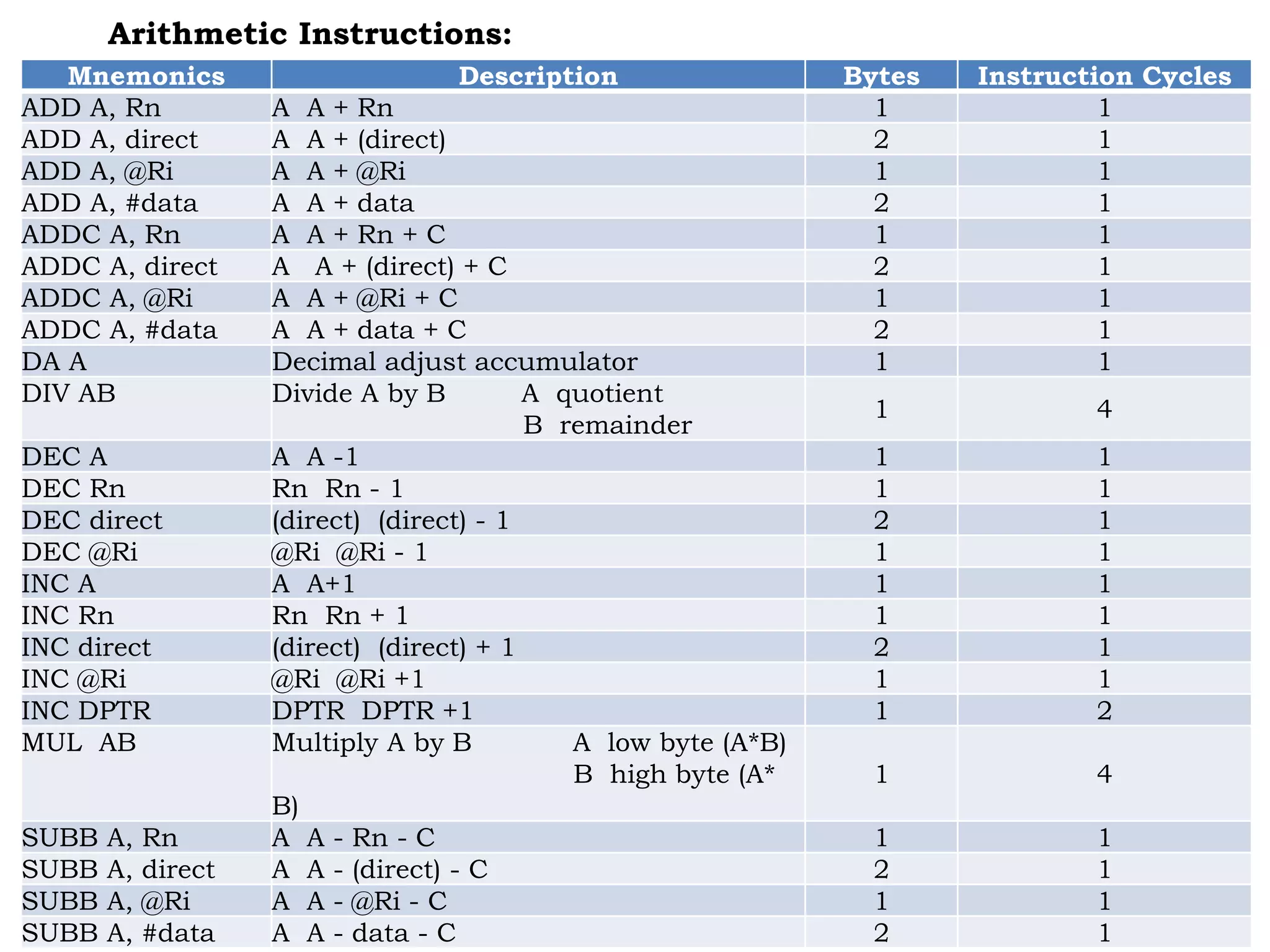

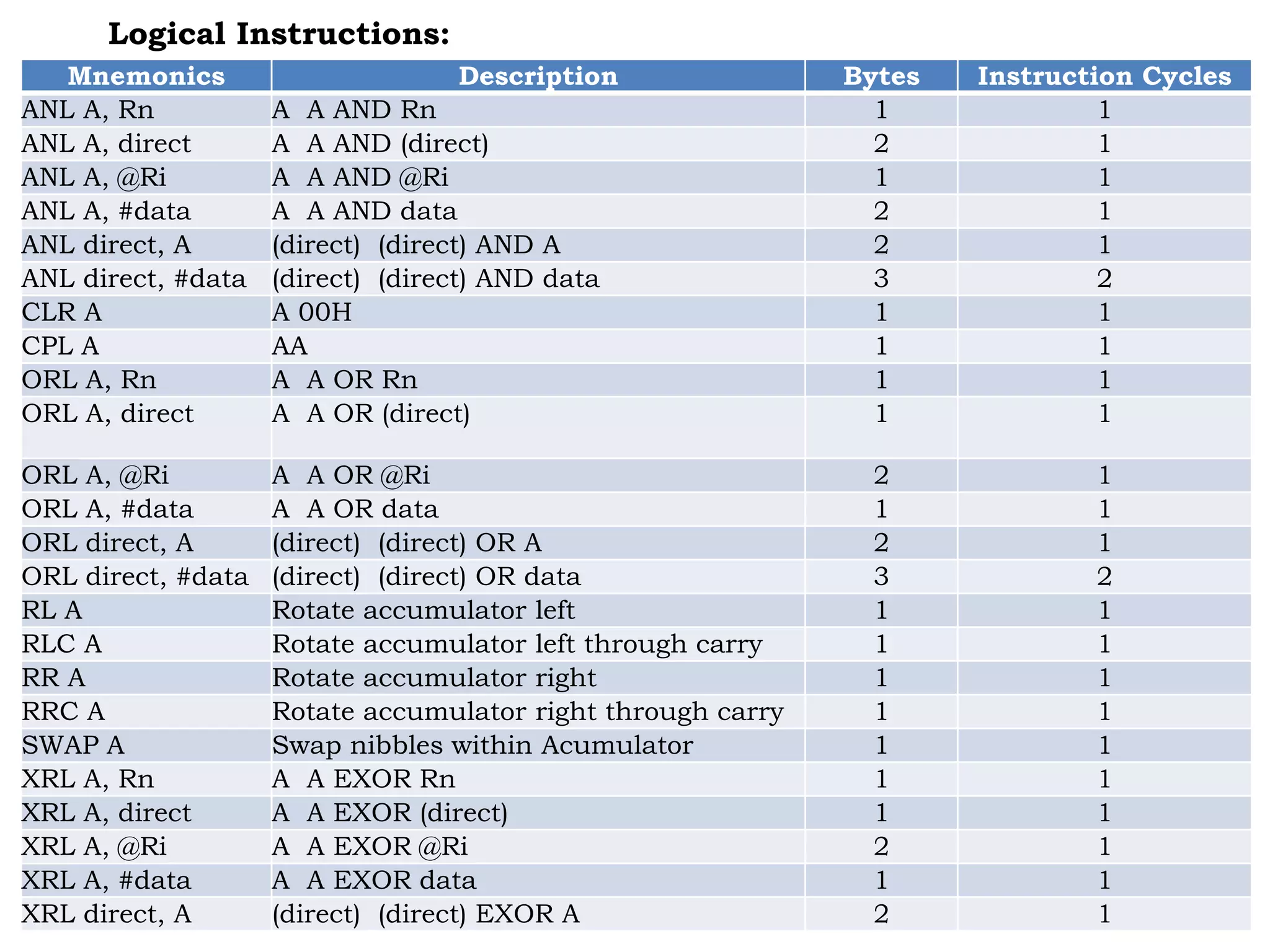

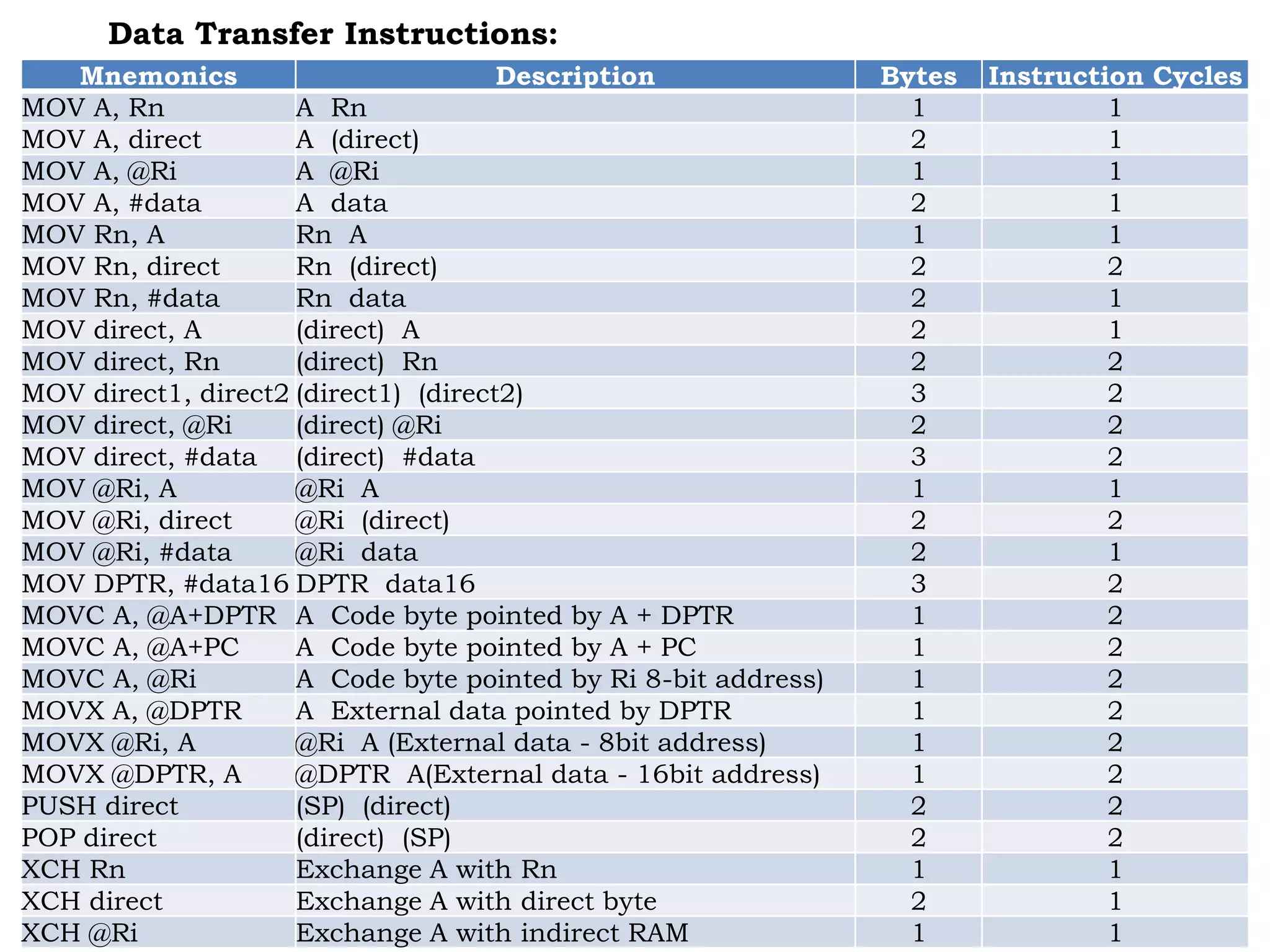

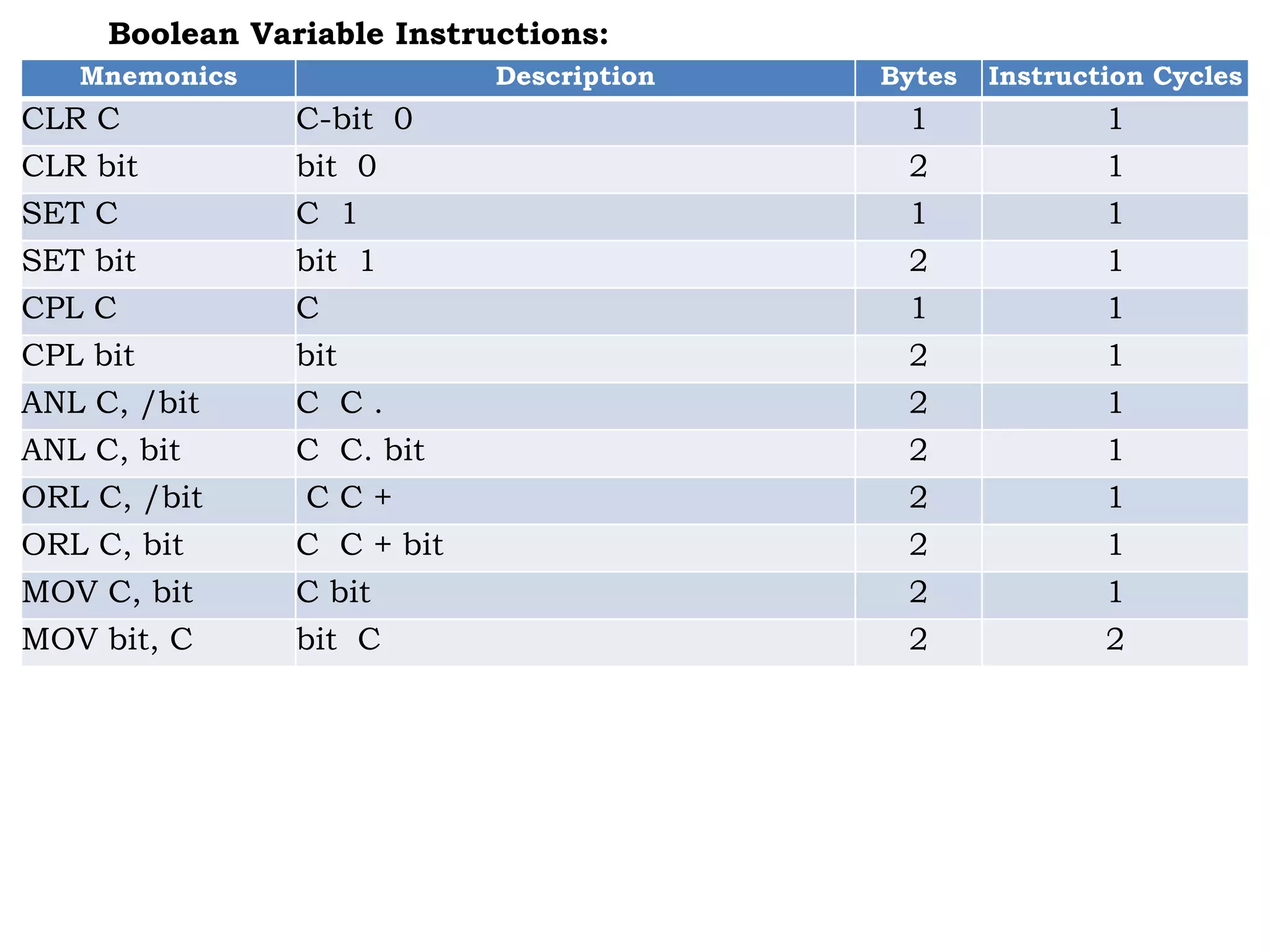

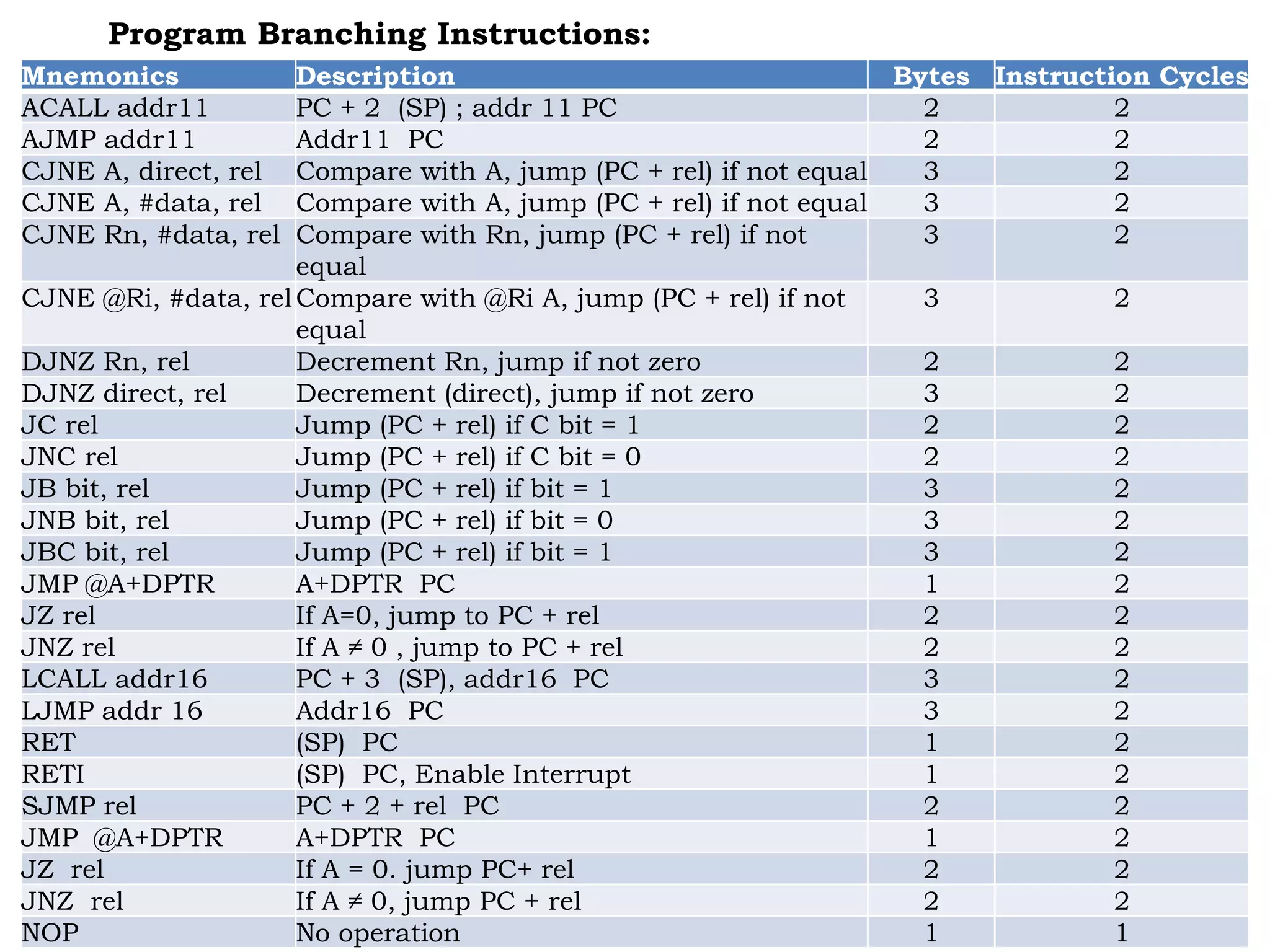

The document provides information about microcontrollers and the 8051 microcontroller family. It defines a microcontroller as a programmable digital processor with on-chip memory and peripherals. It then compares microcontrollers to microprocessors, noting that microcontrollers have on-chip memory and peripherals while microprocessors require external memory. The document proceeds to discuss the development and classification of microcontrollers like the Intel 4004 and 8051. It provides details on the architecture, memory structure, instructions, and I/O ports of the 8051 microcontroller.