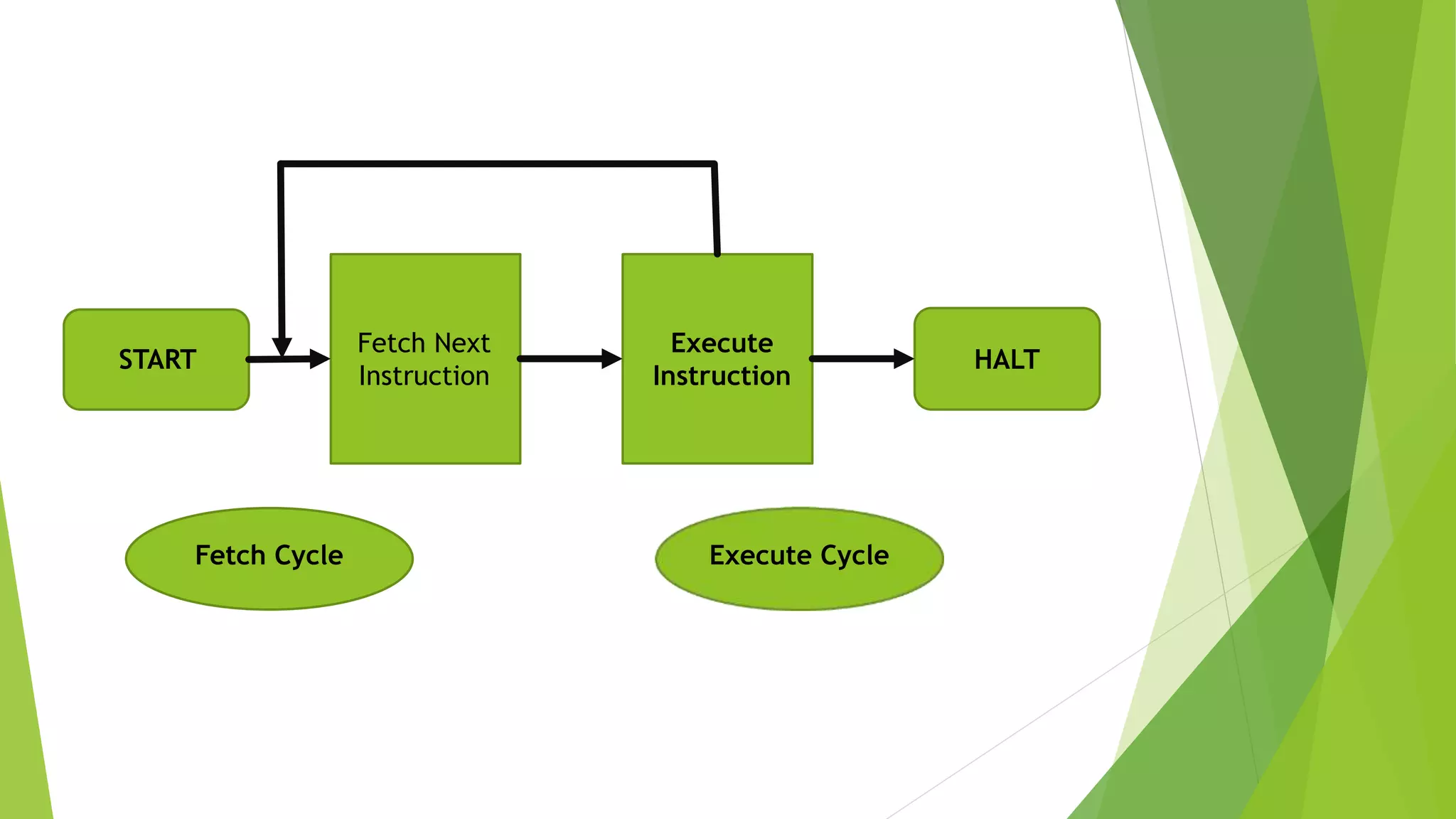

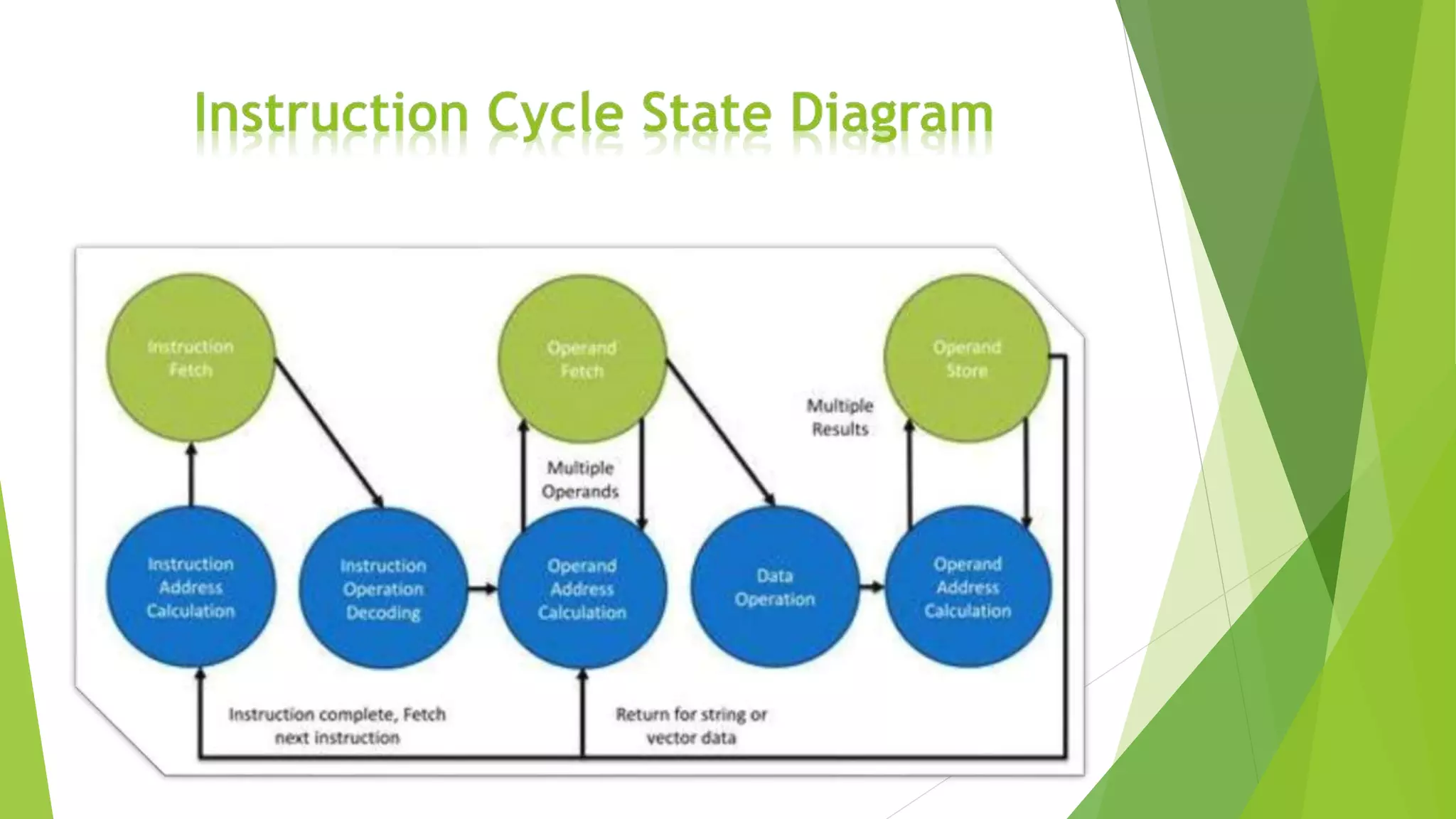

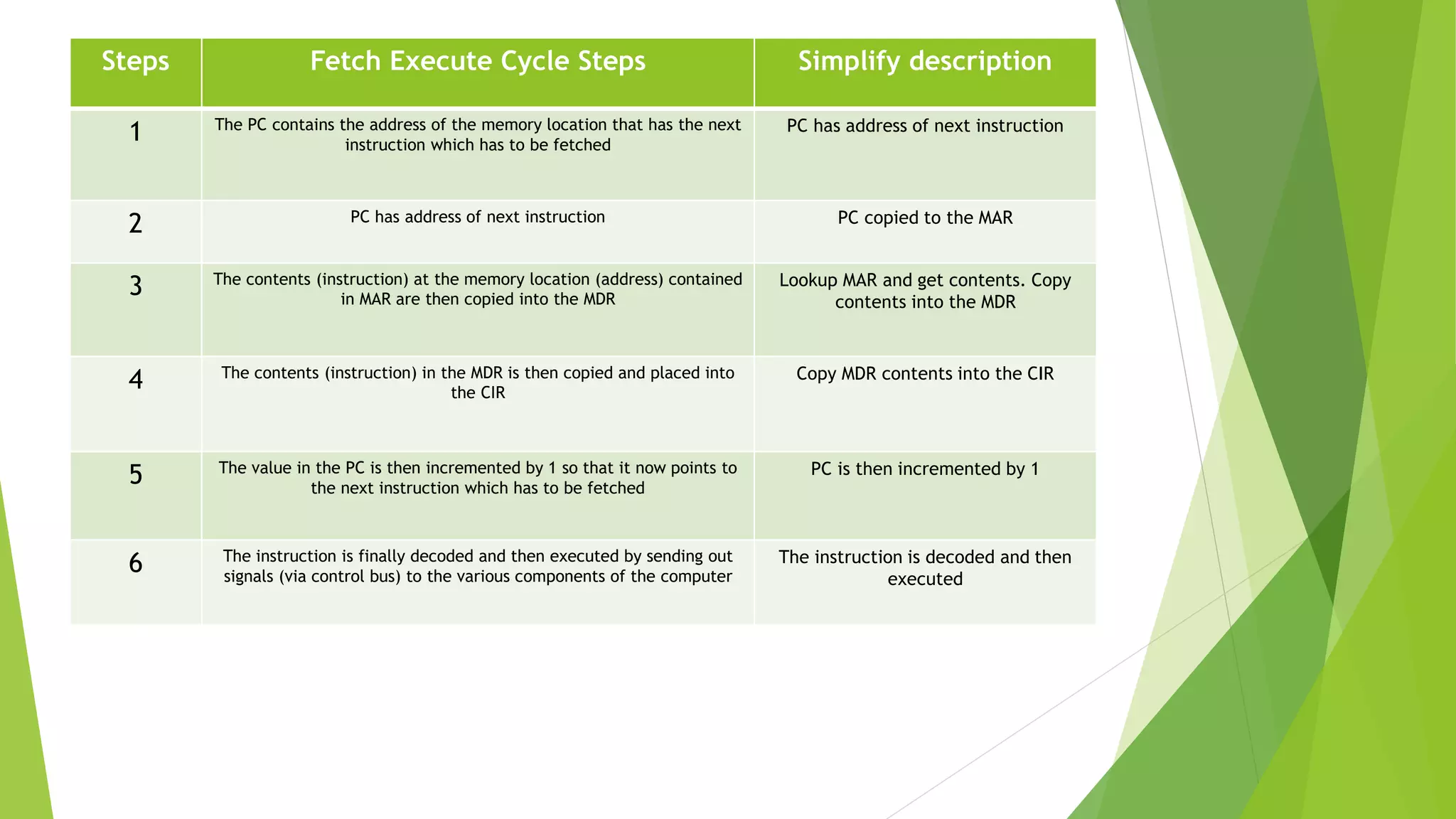

The instruction cycle consists of three main stages:

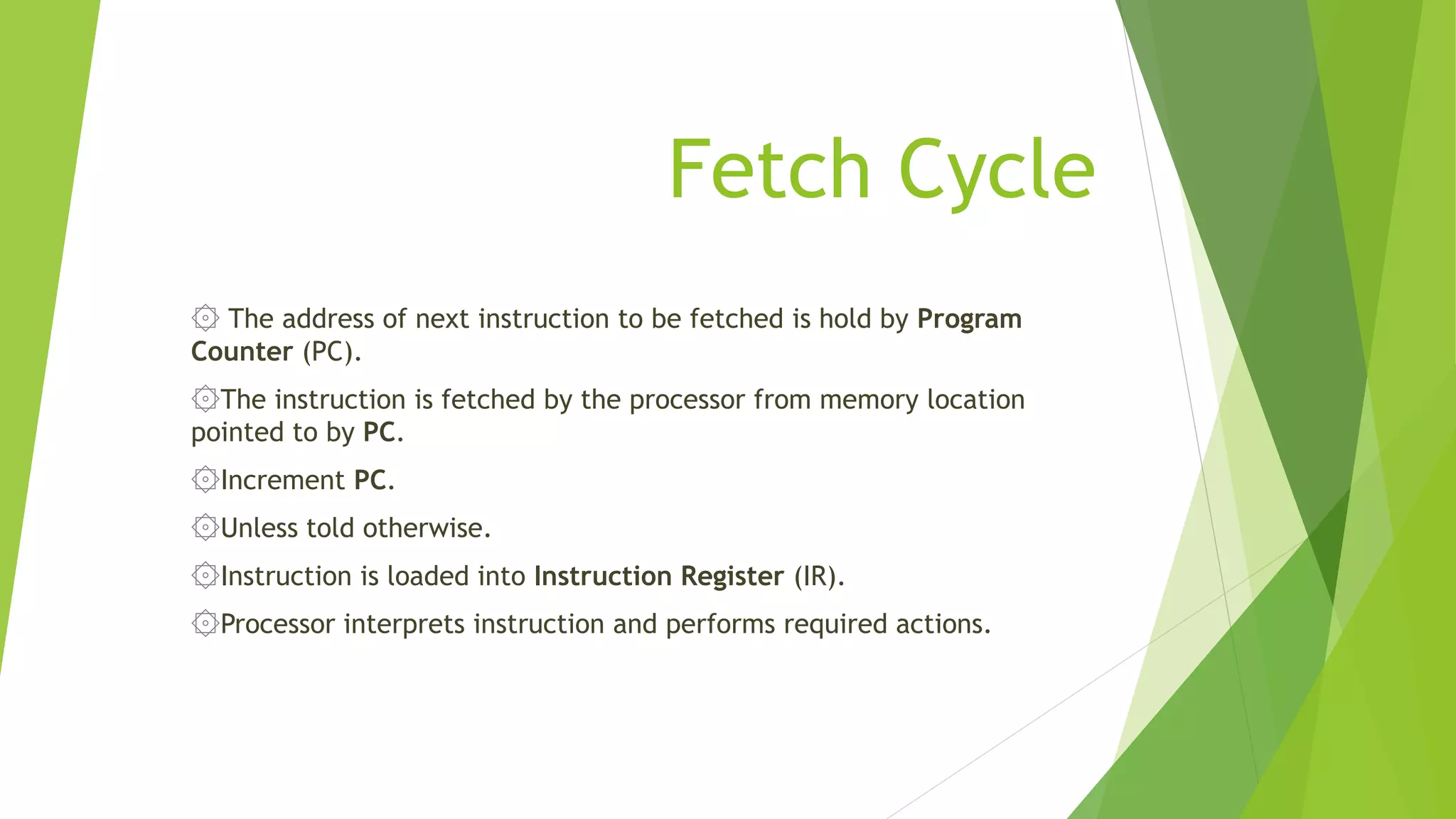

1. The fetch stage where the instruction is fetched from the memory address stored in the program counter and placed in the instruction register. The program counter is then incremented.

2. The decode stage where the instruction is interpreted by the decoder.

3. The execute stage where the control unit passes signals to perform the required operations, and the result is stored in memory or sent to an output device. The program counter may then be updated to fetch the next instruction, beginning the cycle again.