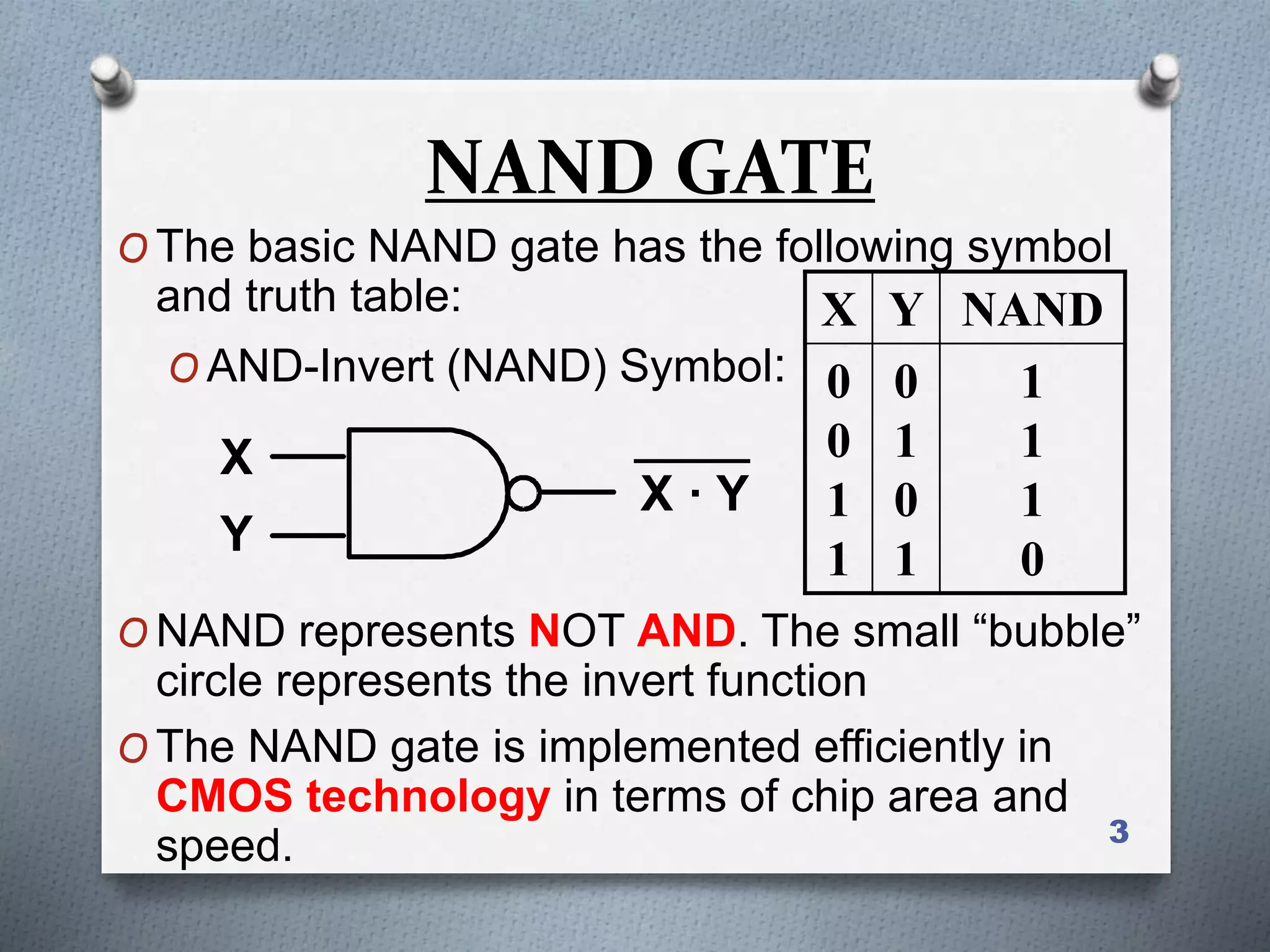

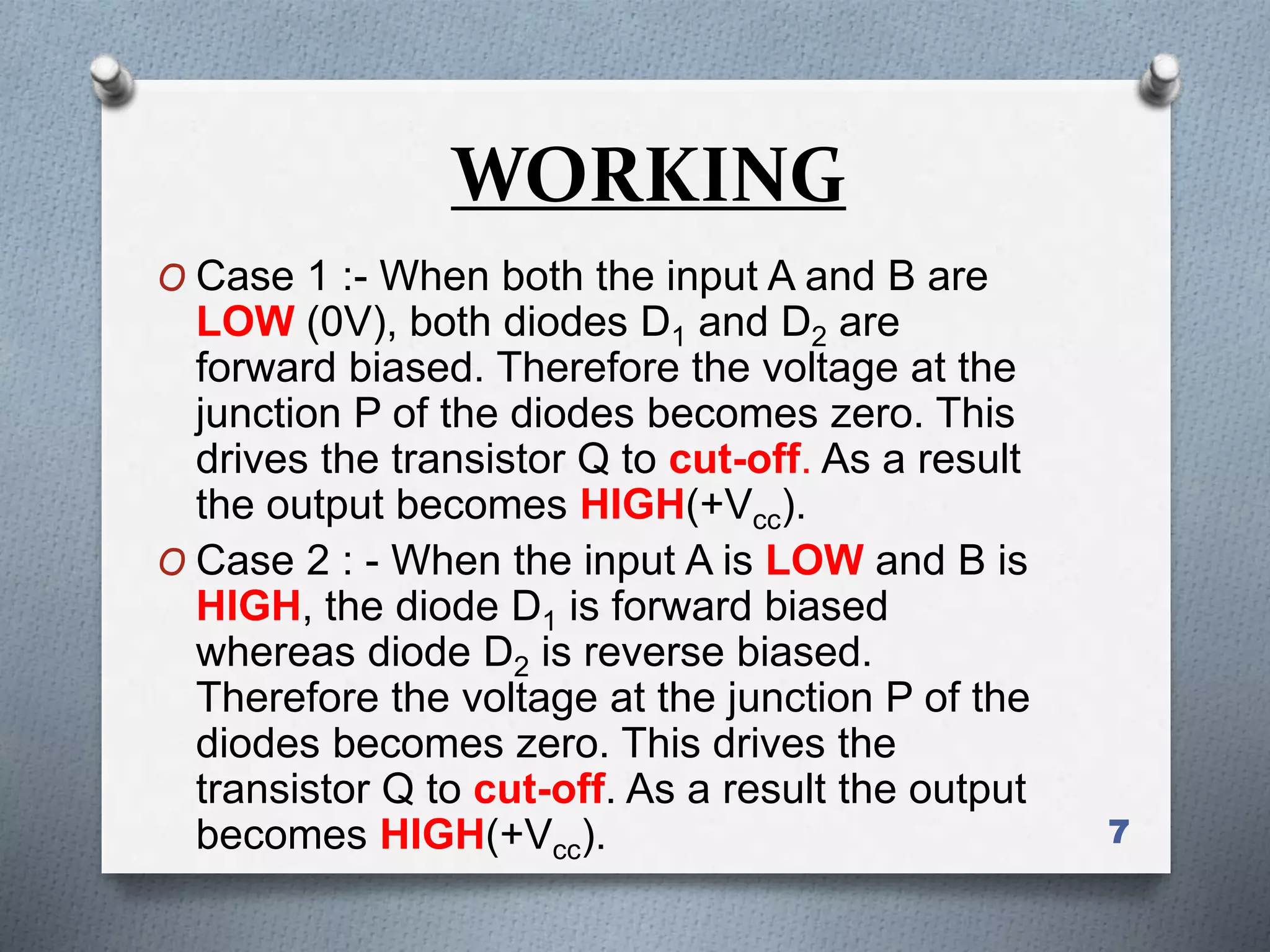

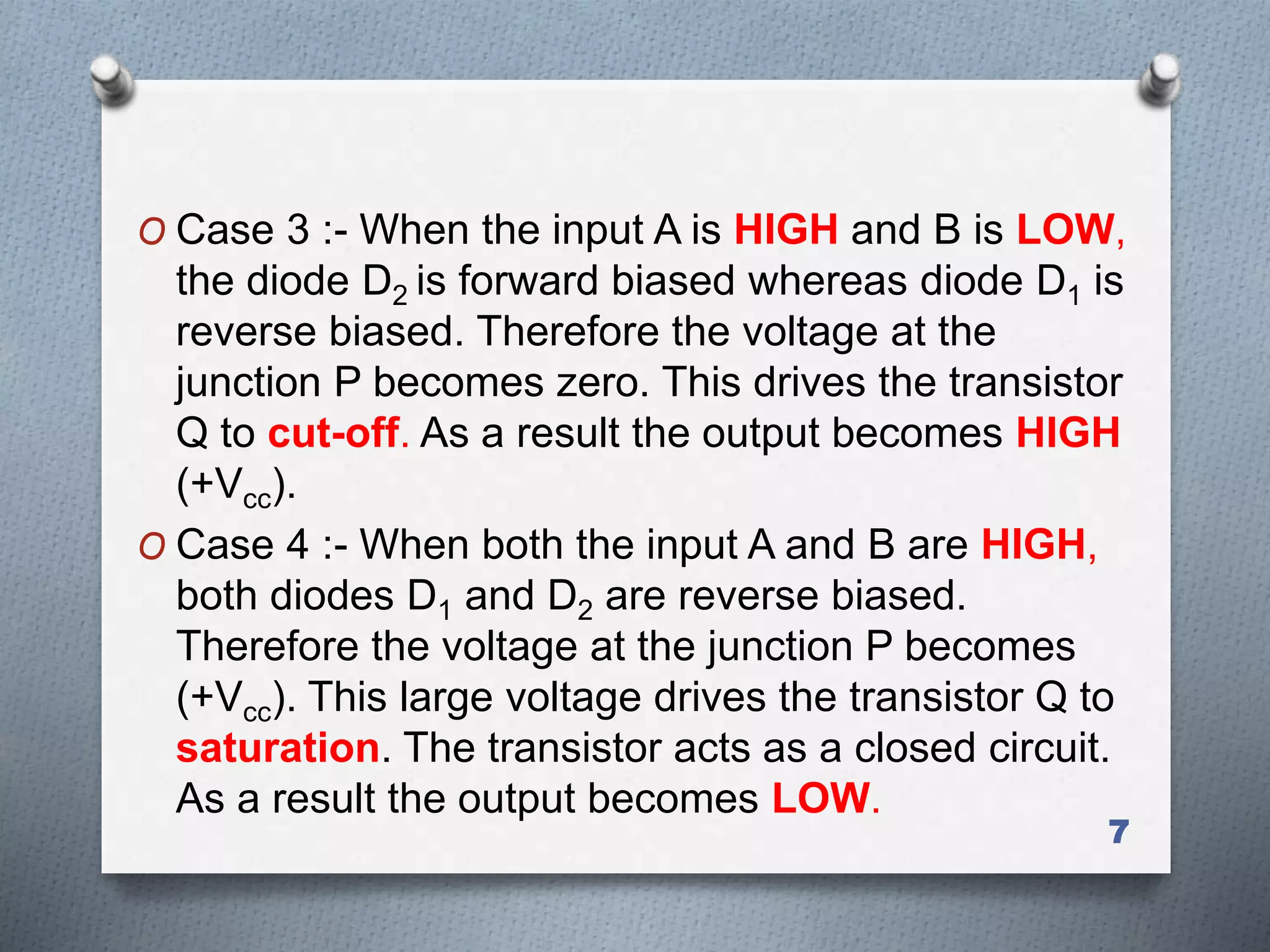

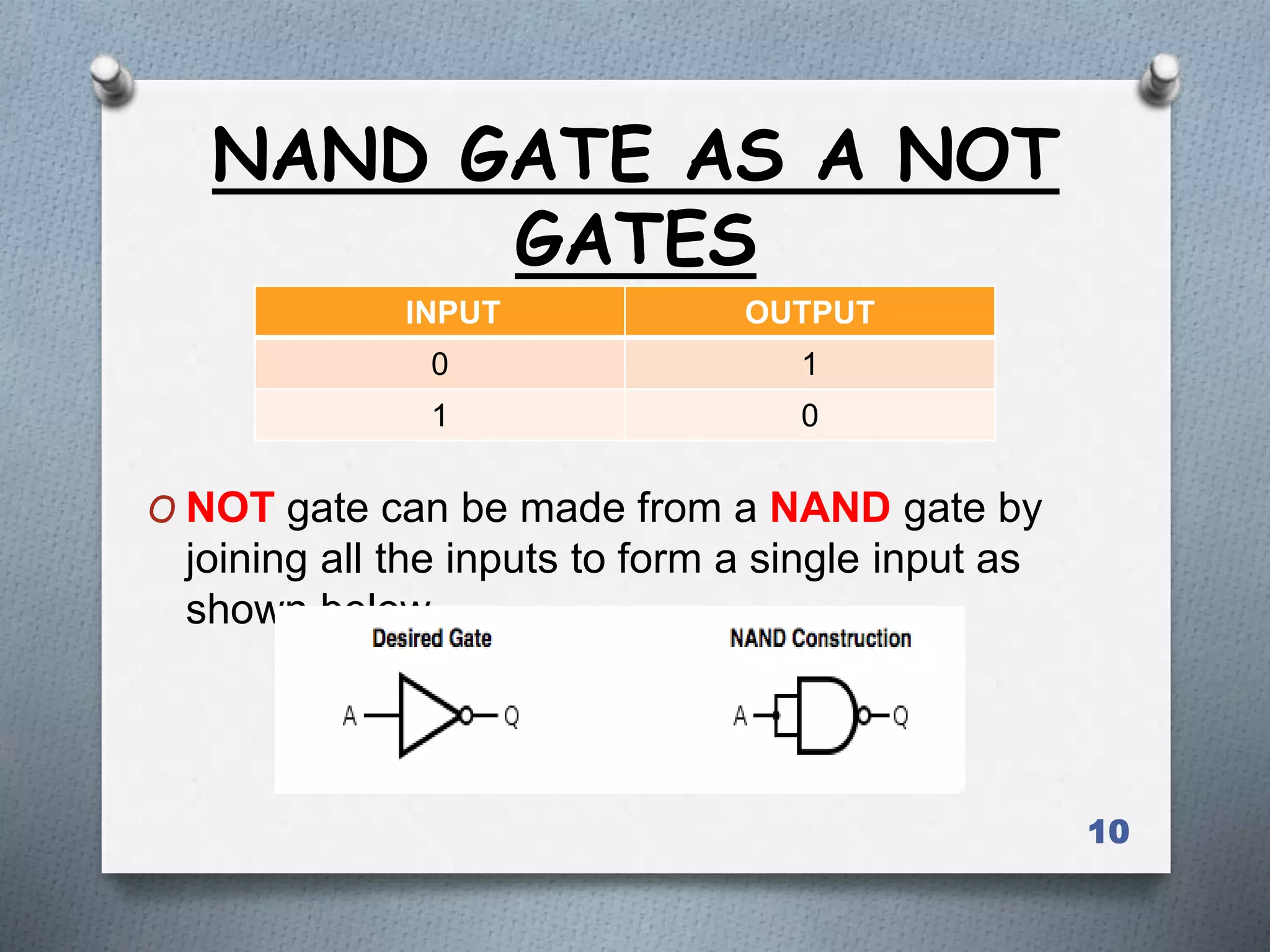

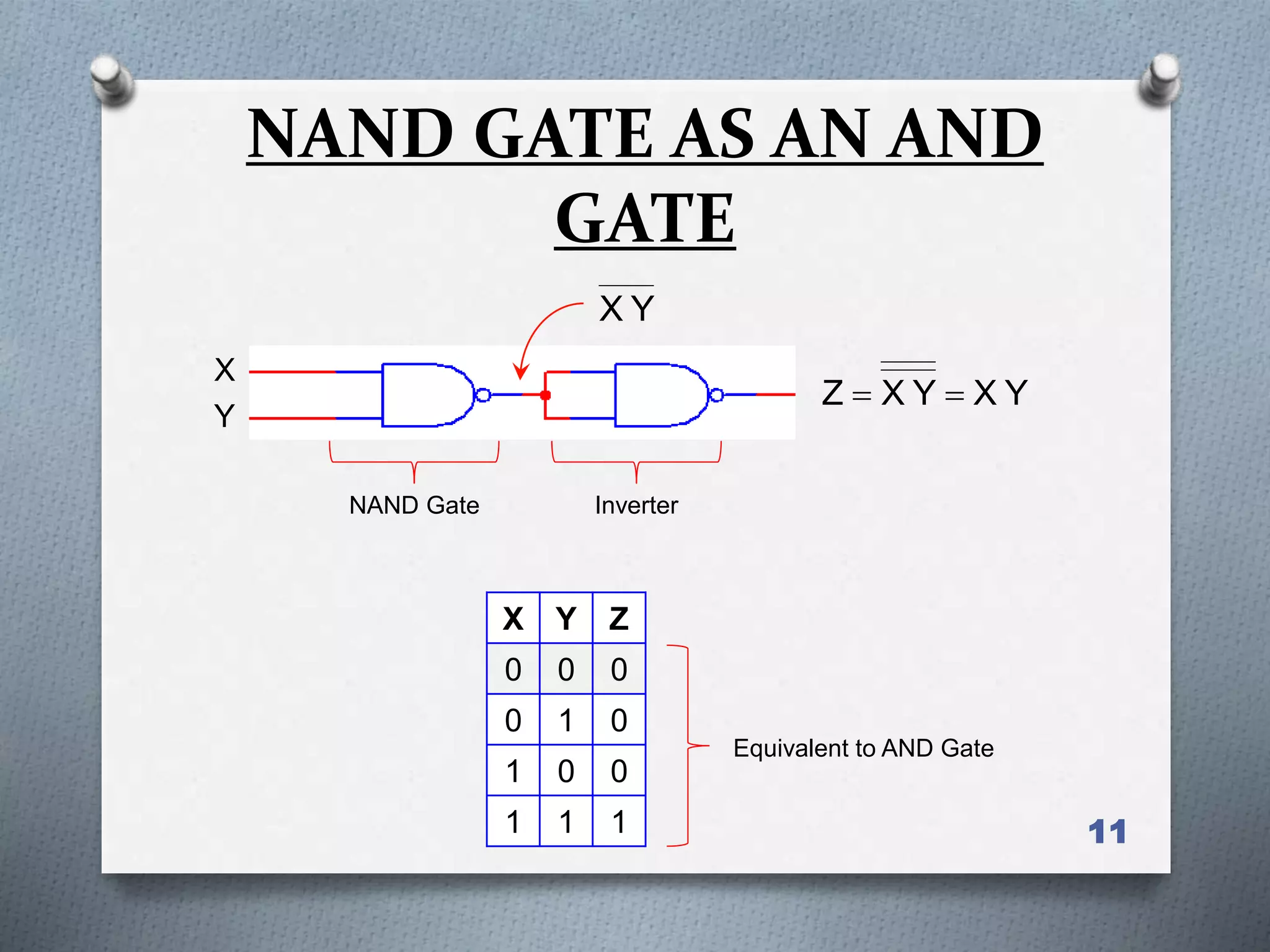

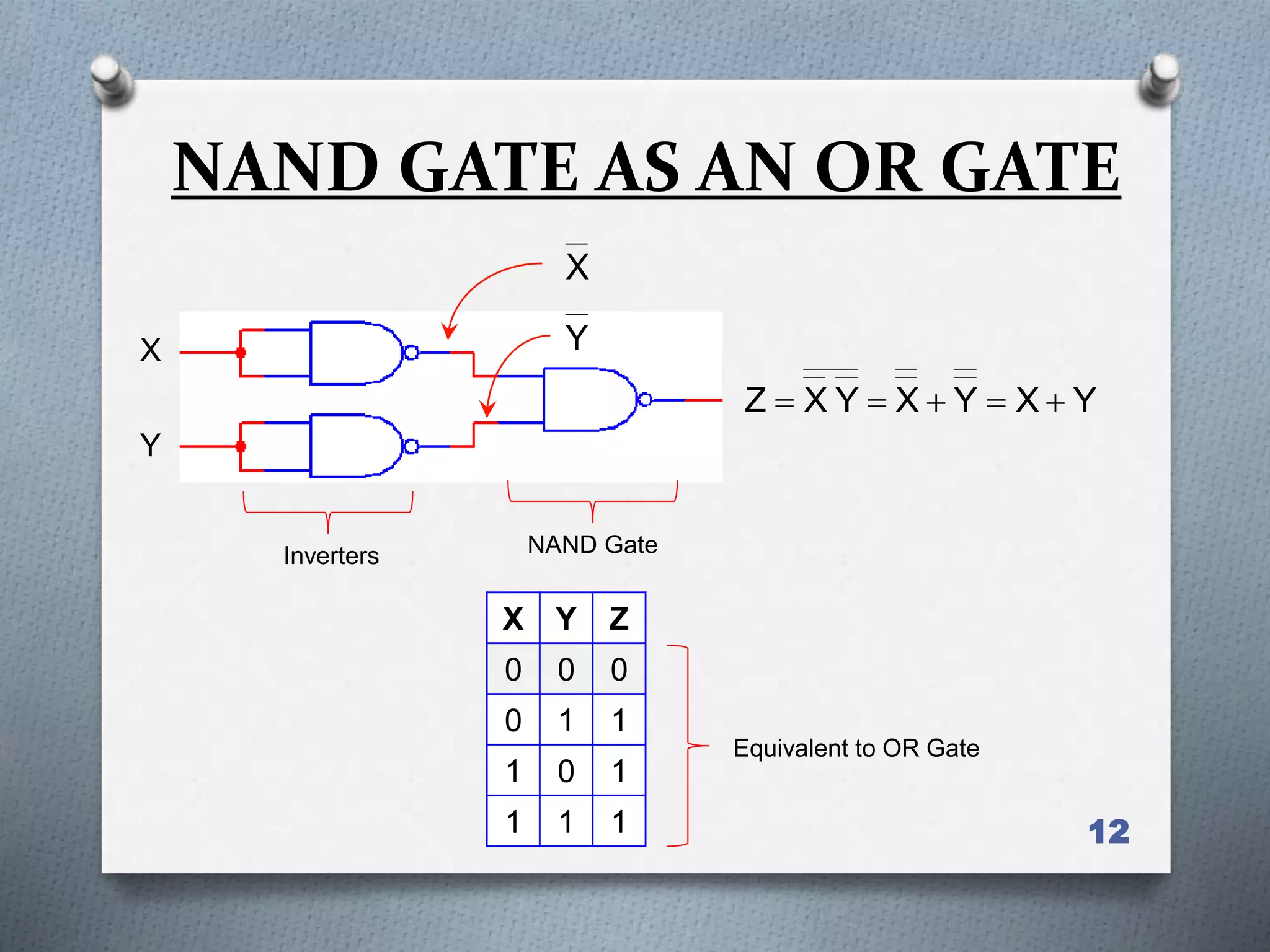

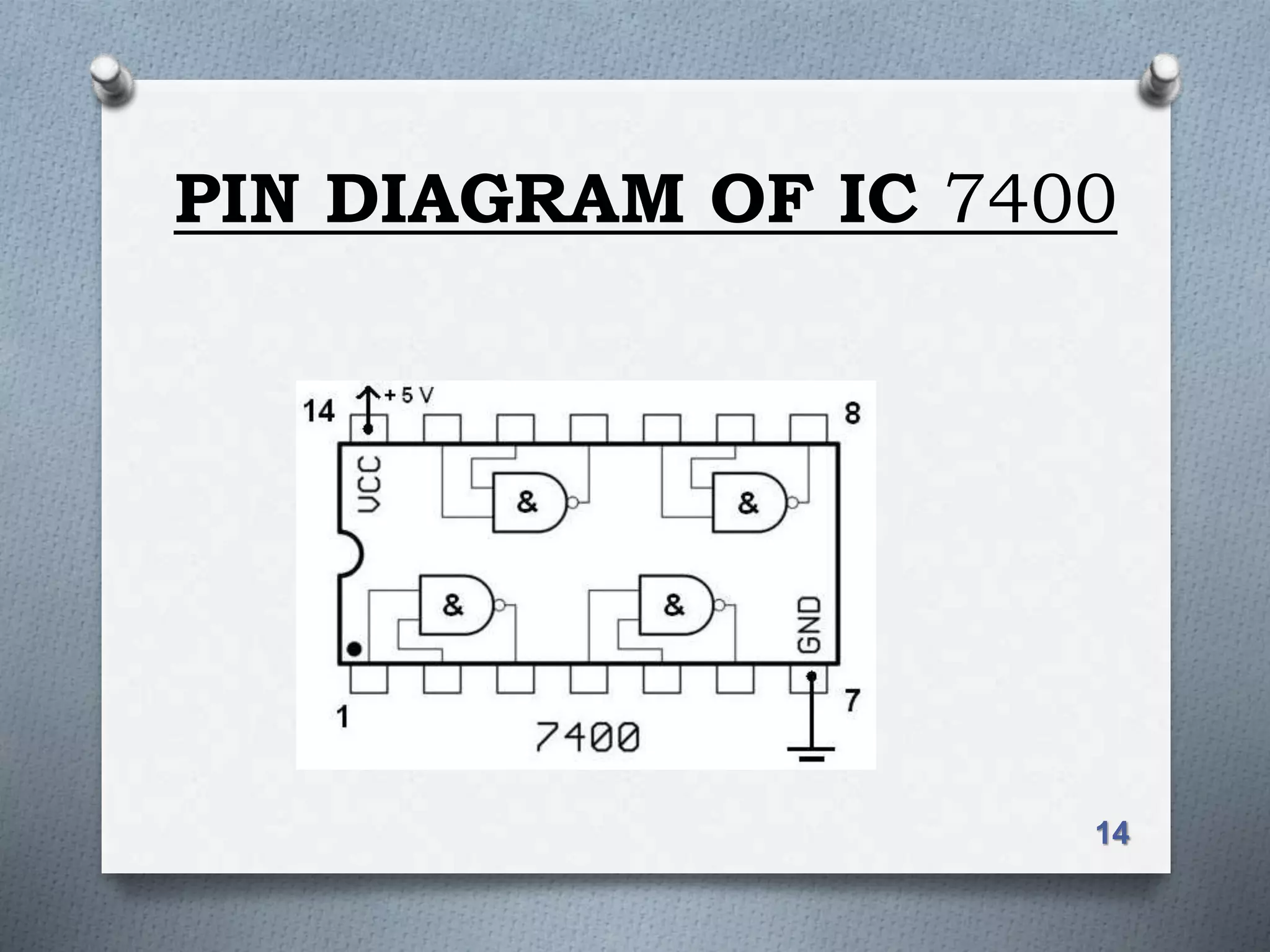

This document describes the NAND gate, a digital logic gate that implements the NAND logical operation. It has two or more inputs but only one output. The output is HIGH only if at least one of the inputs is LOW, and is LOW only when all inputs are HIGH. NAND gates can be used to implement any Boolean function, and are commonly used to build circuits because they are simple and fast. The document explains how NAND gates can function as NOT, AND, and OR gates and illustrates their pin diagrams and truth tables.