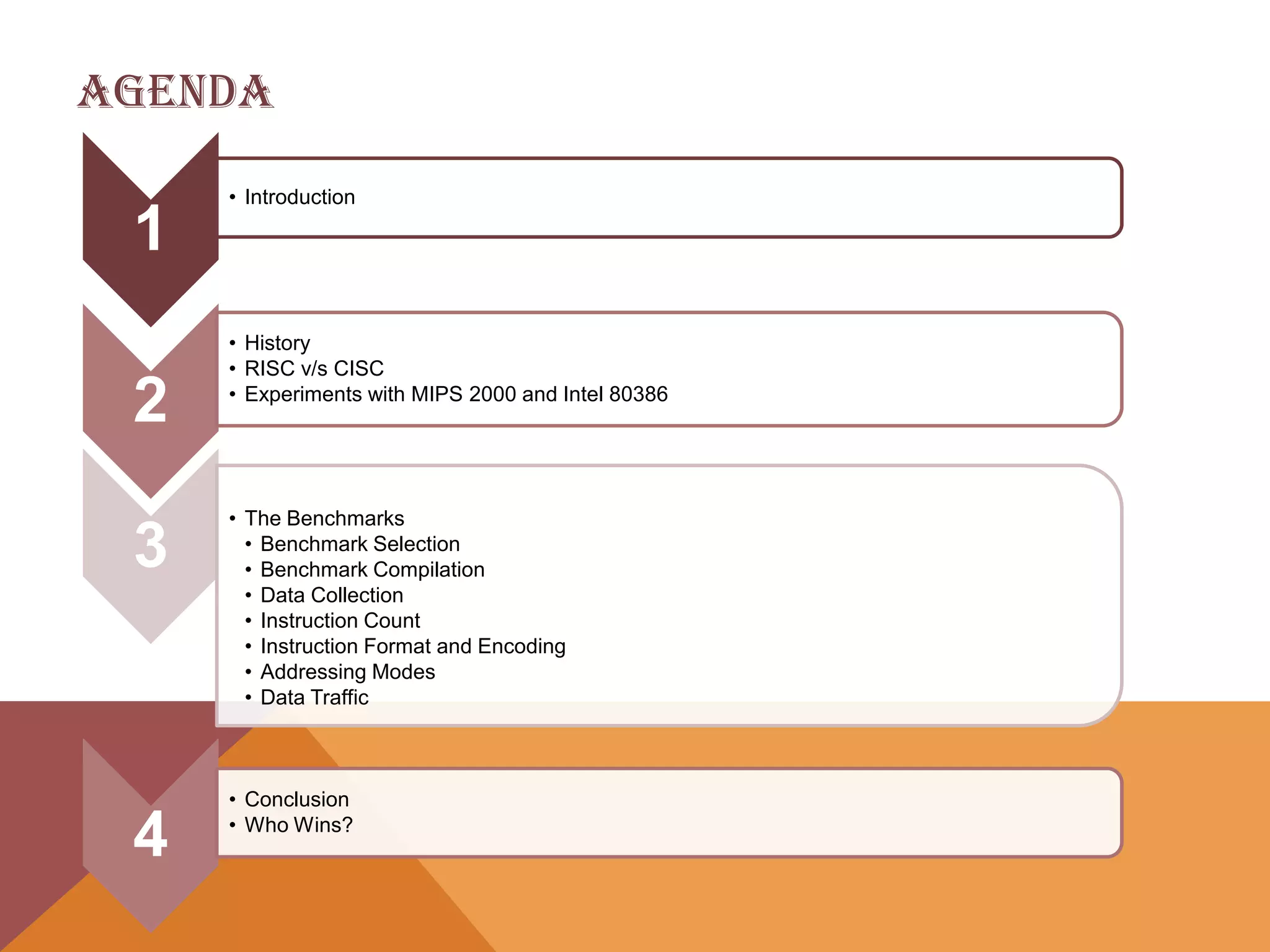

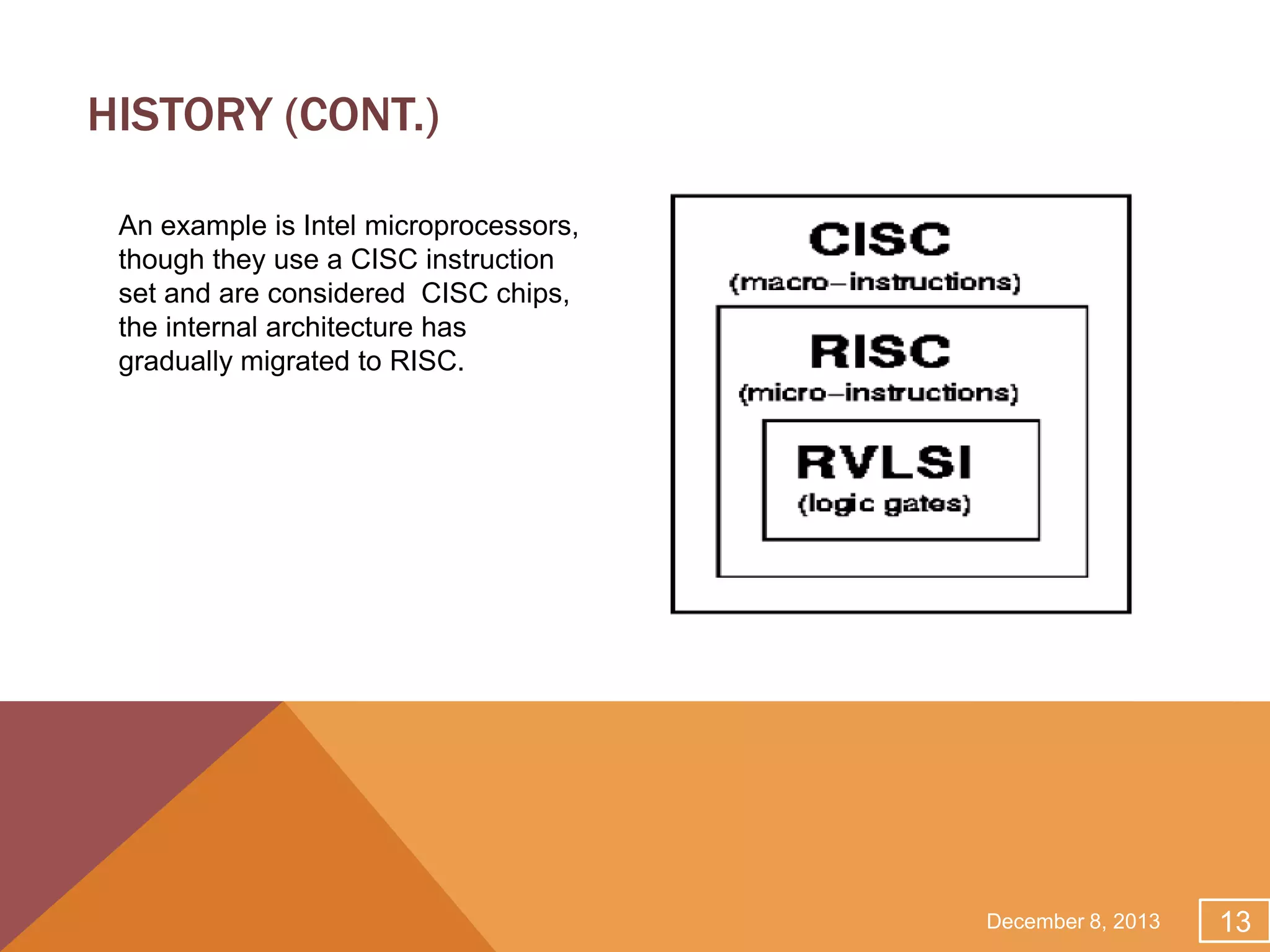

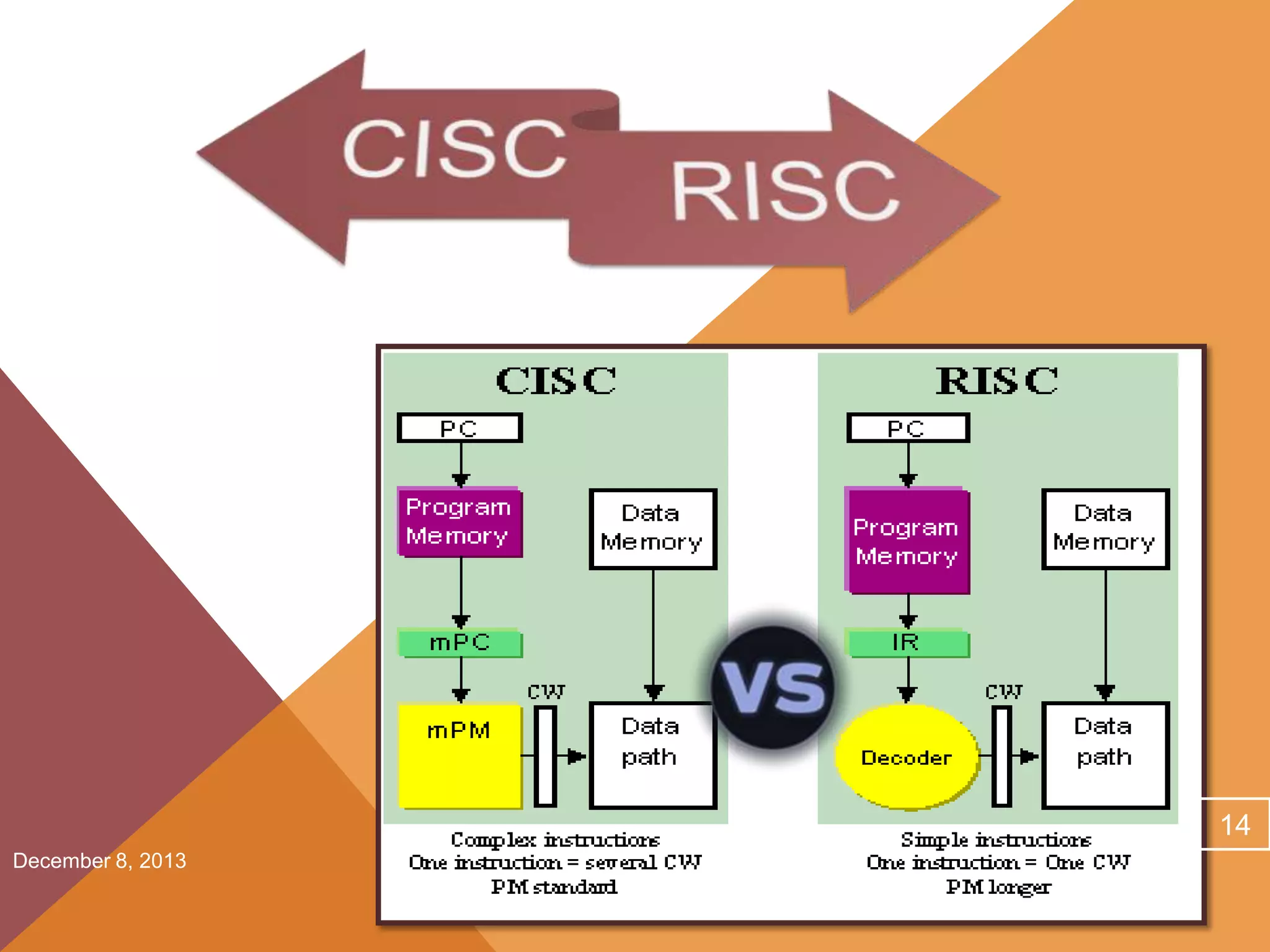

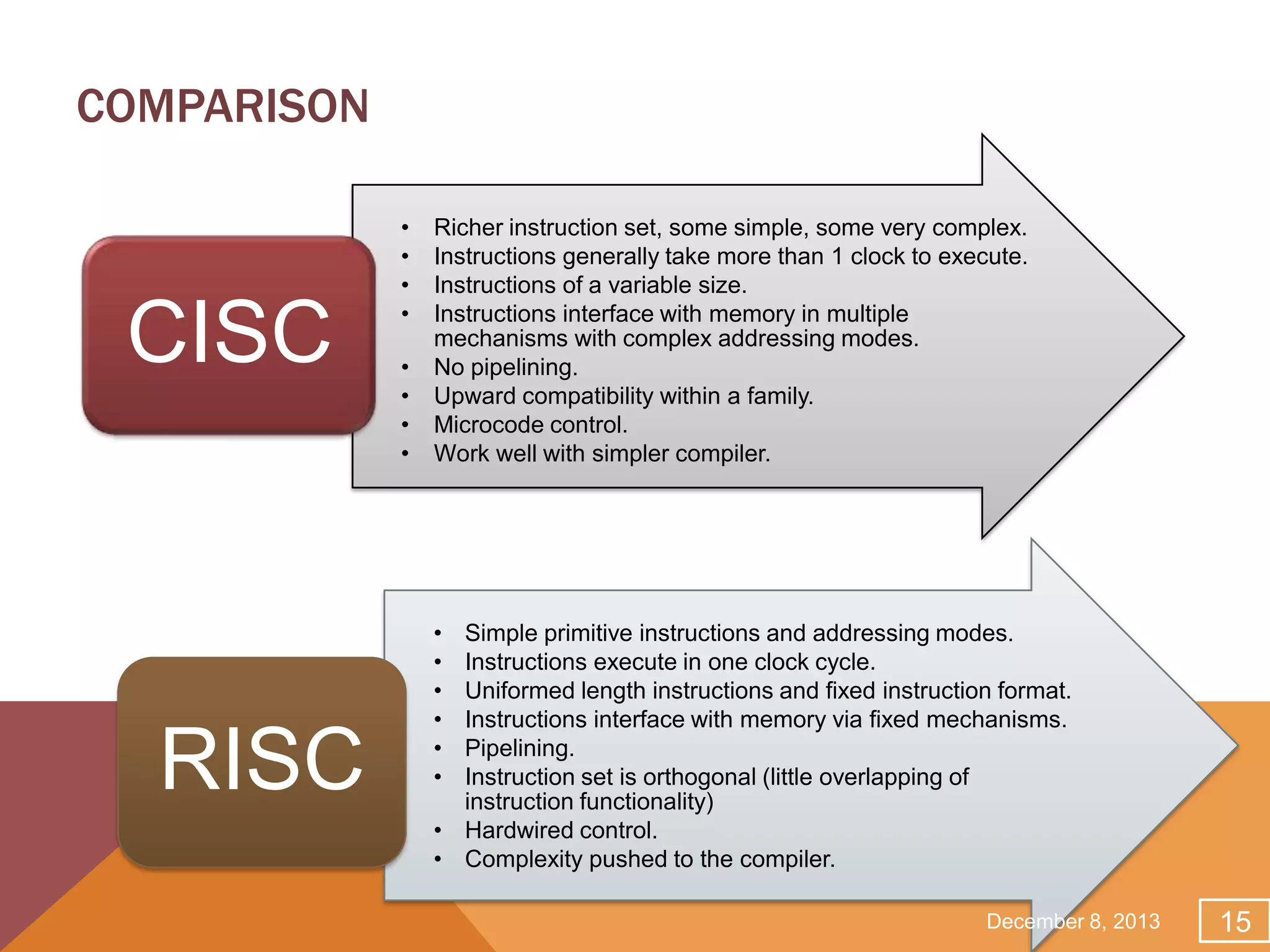

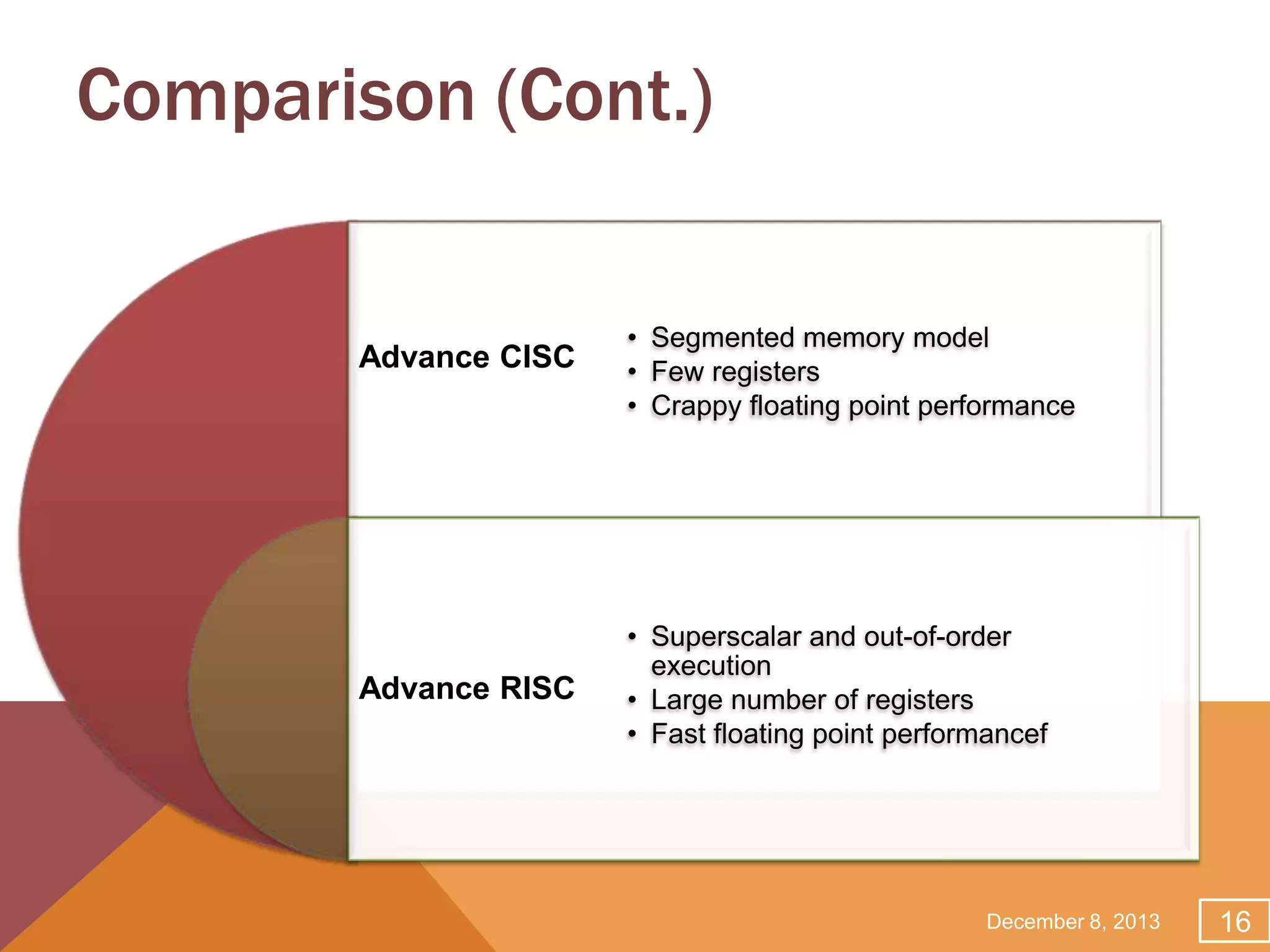

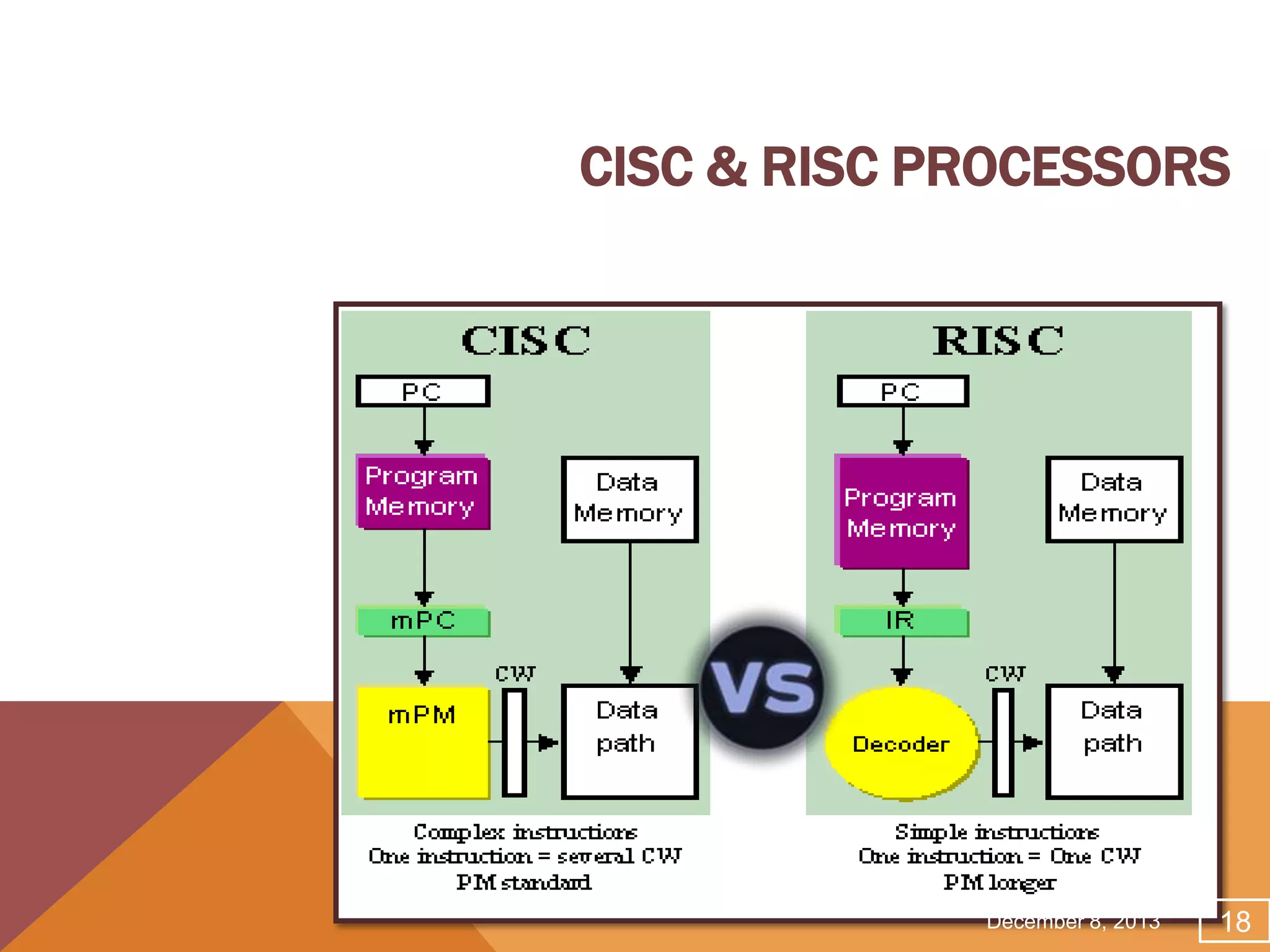

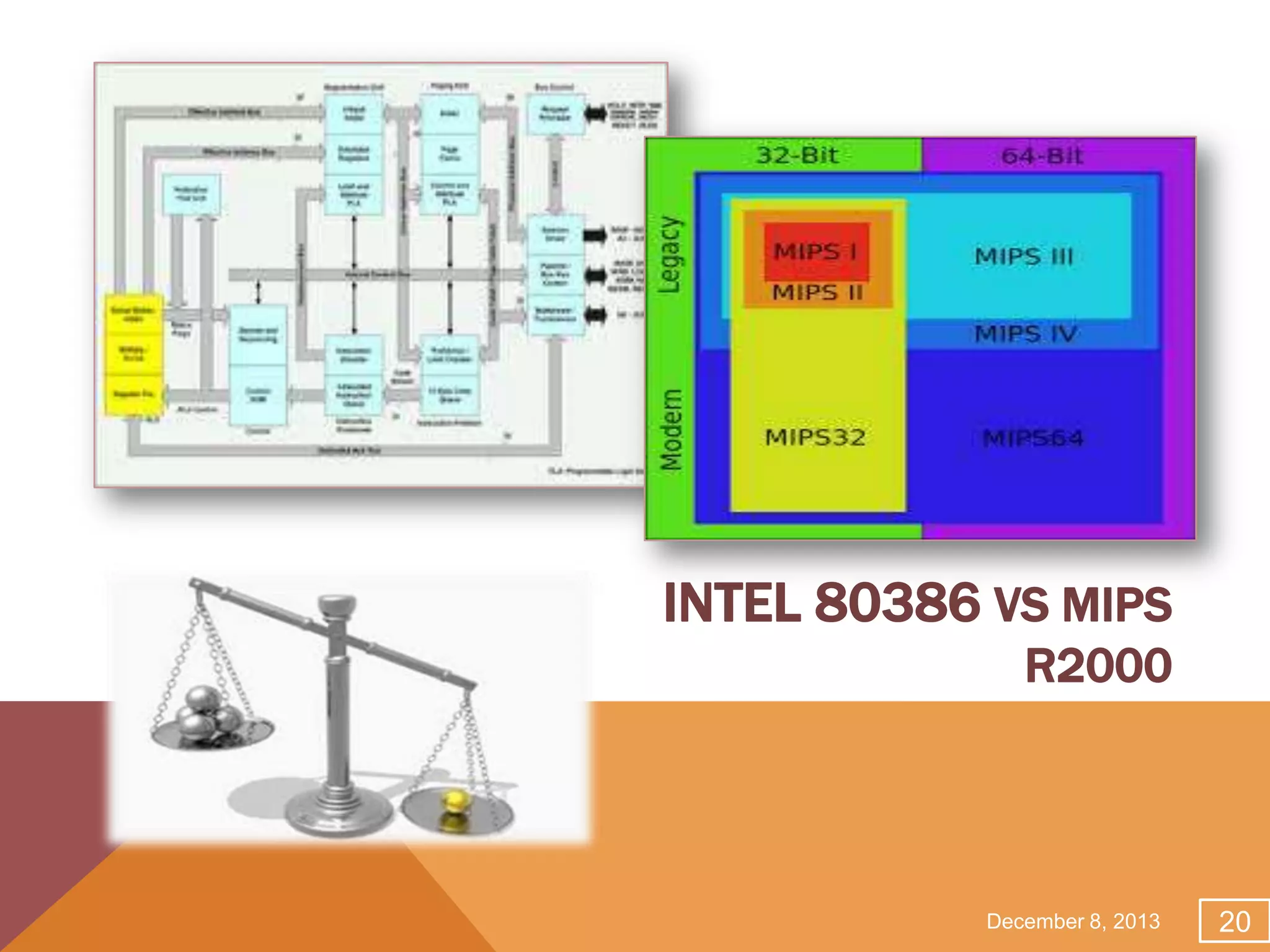

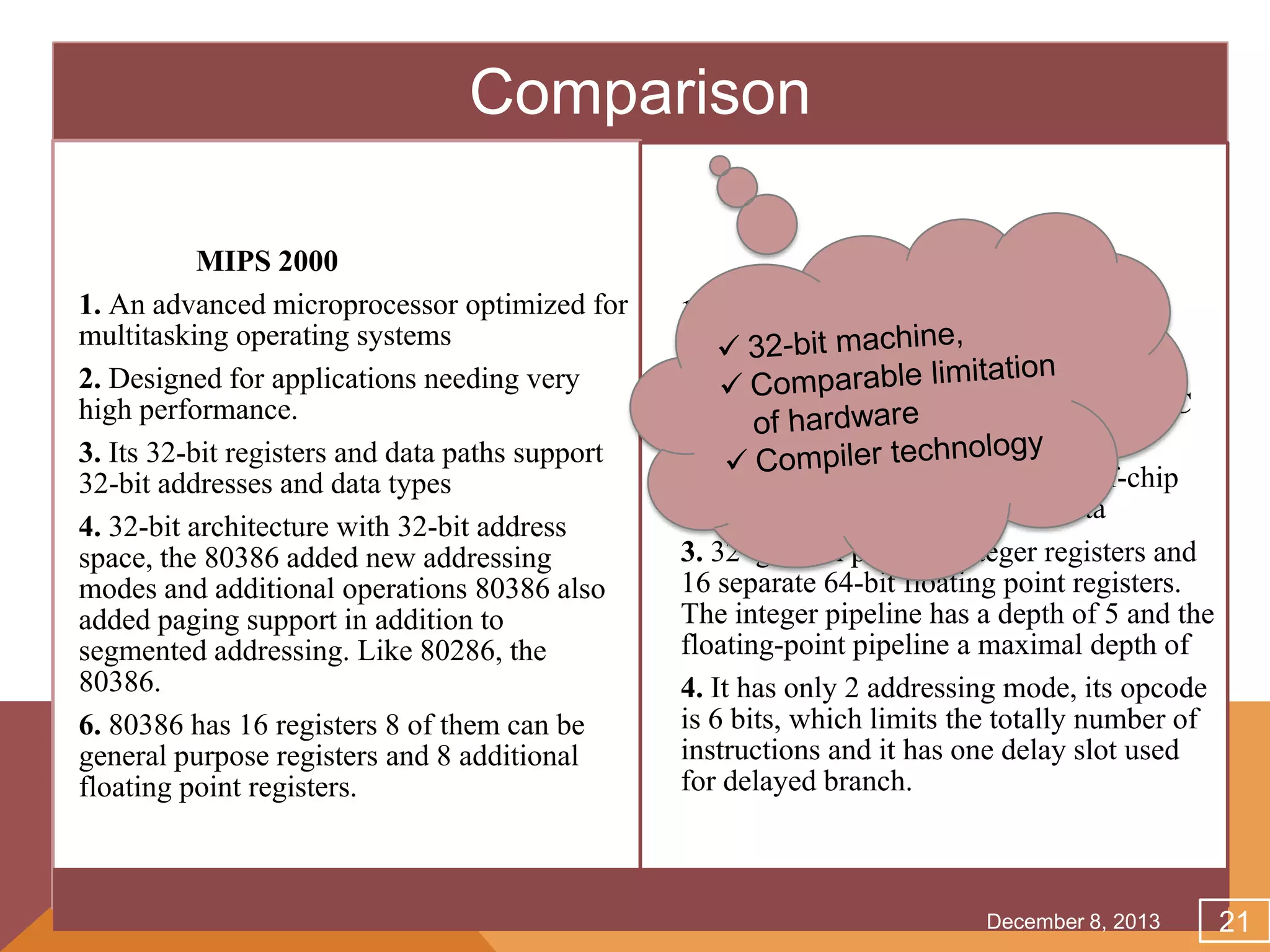

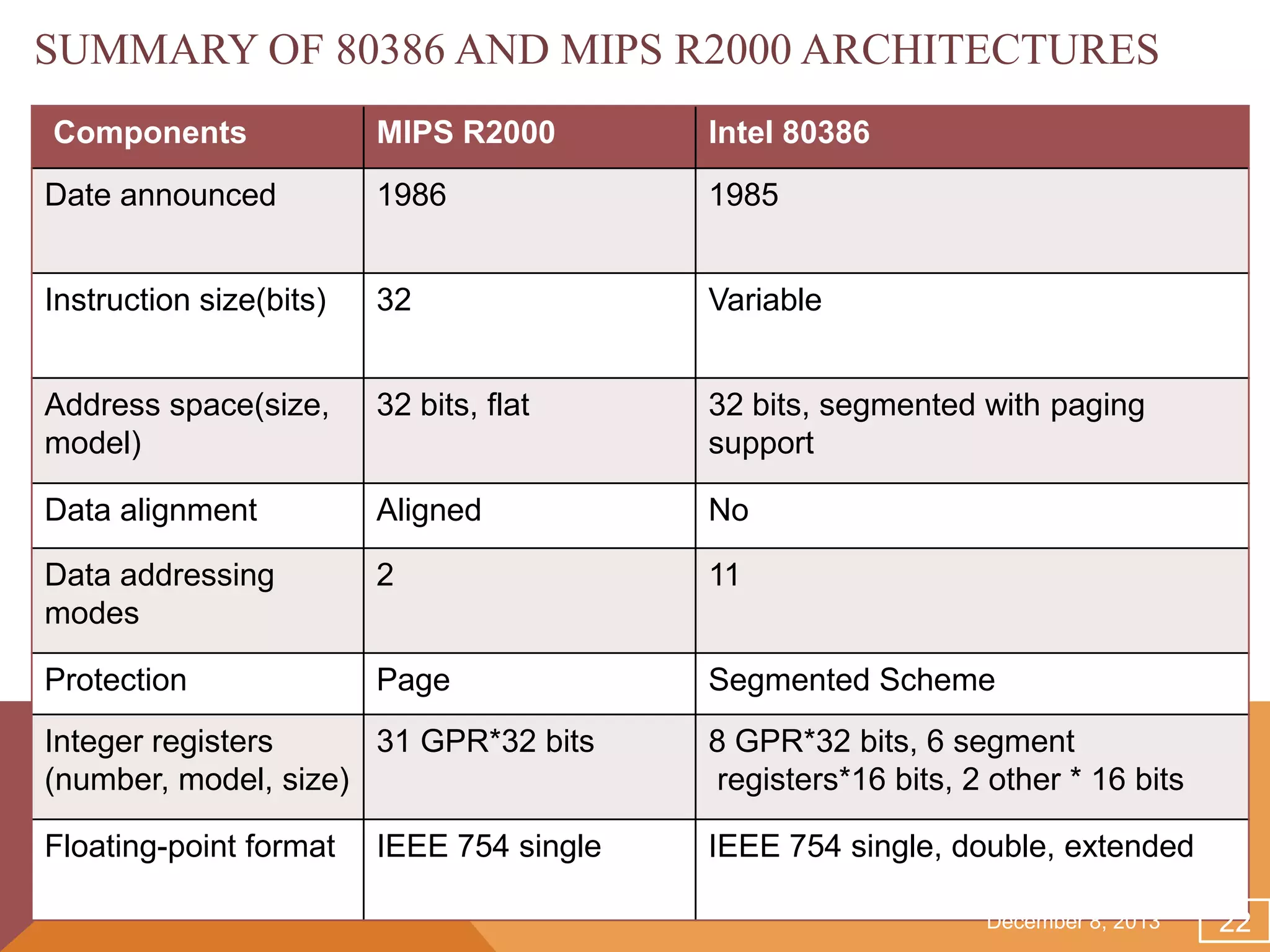

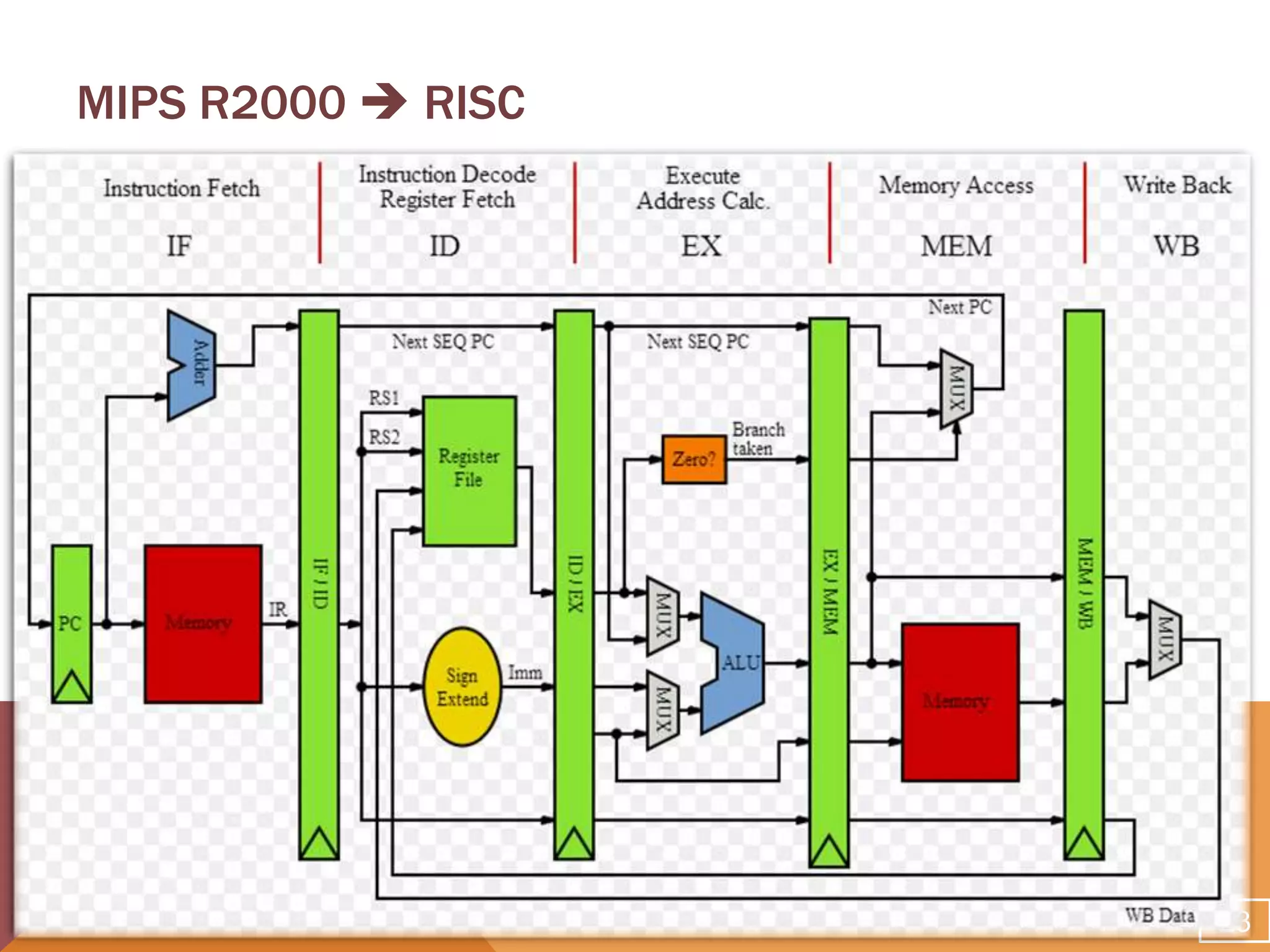

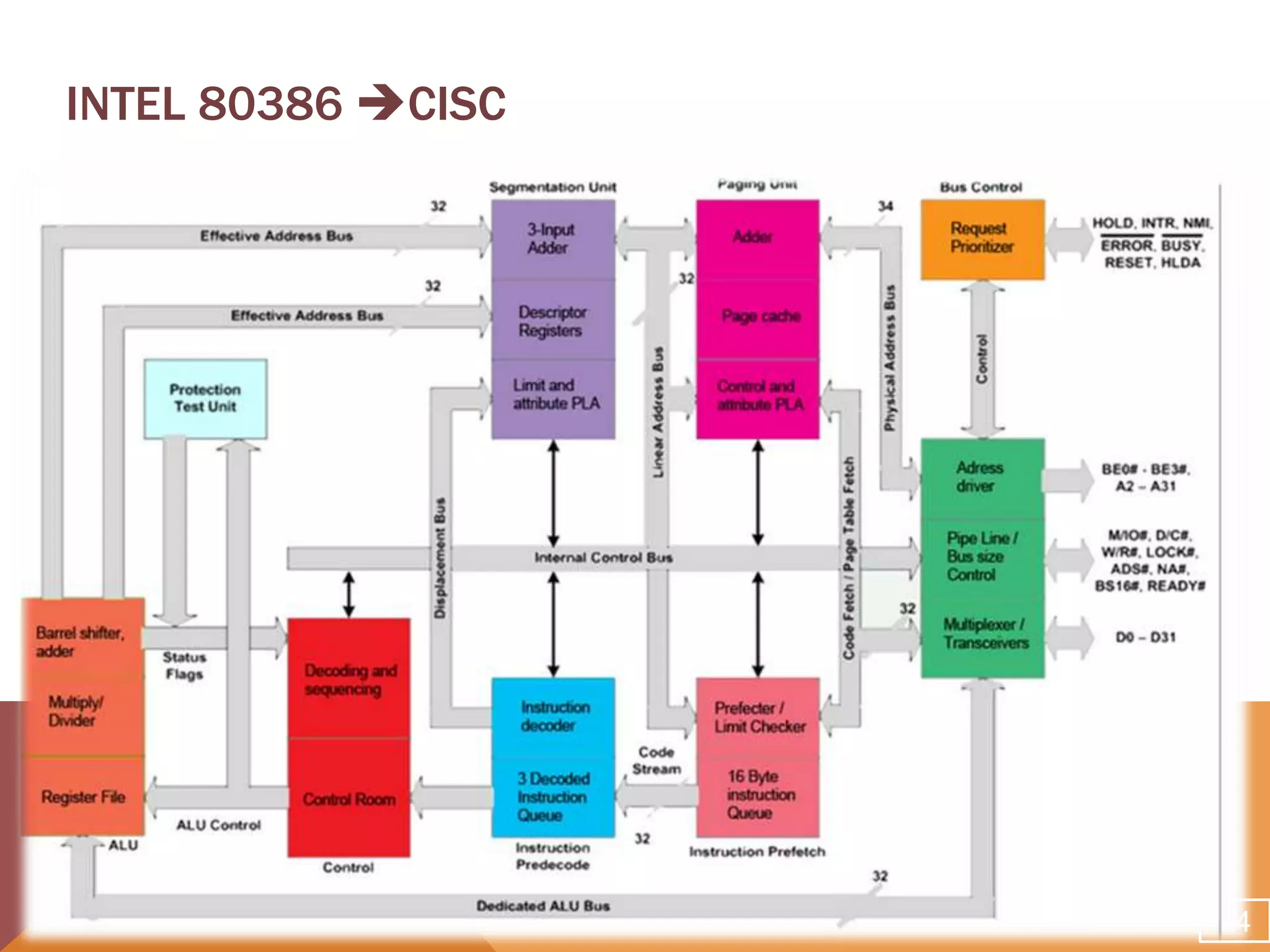

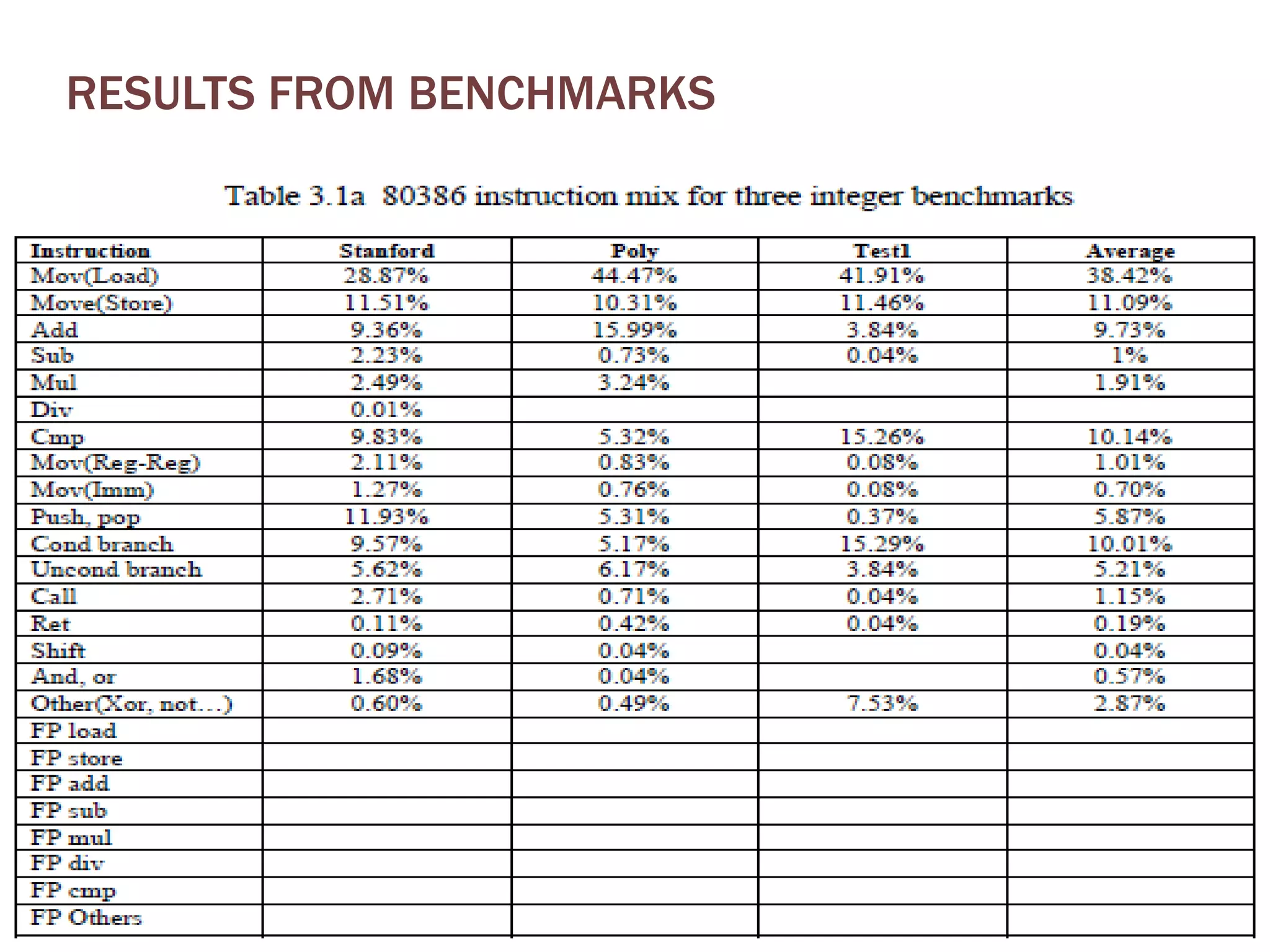

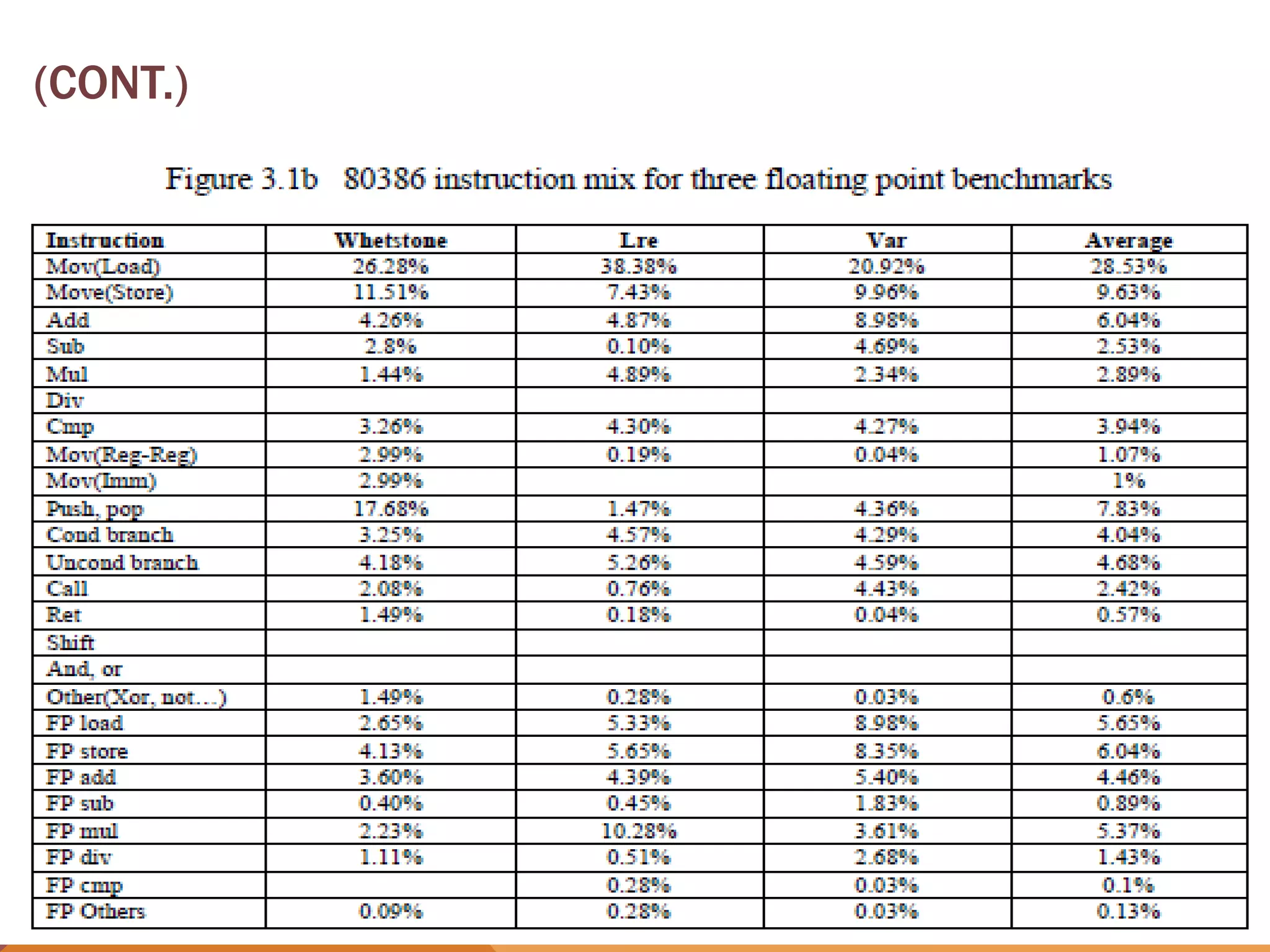

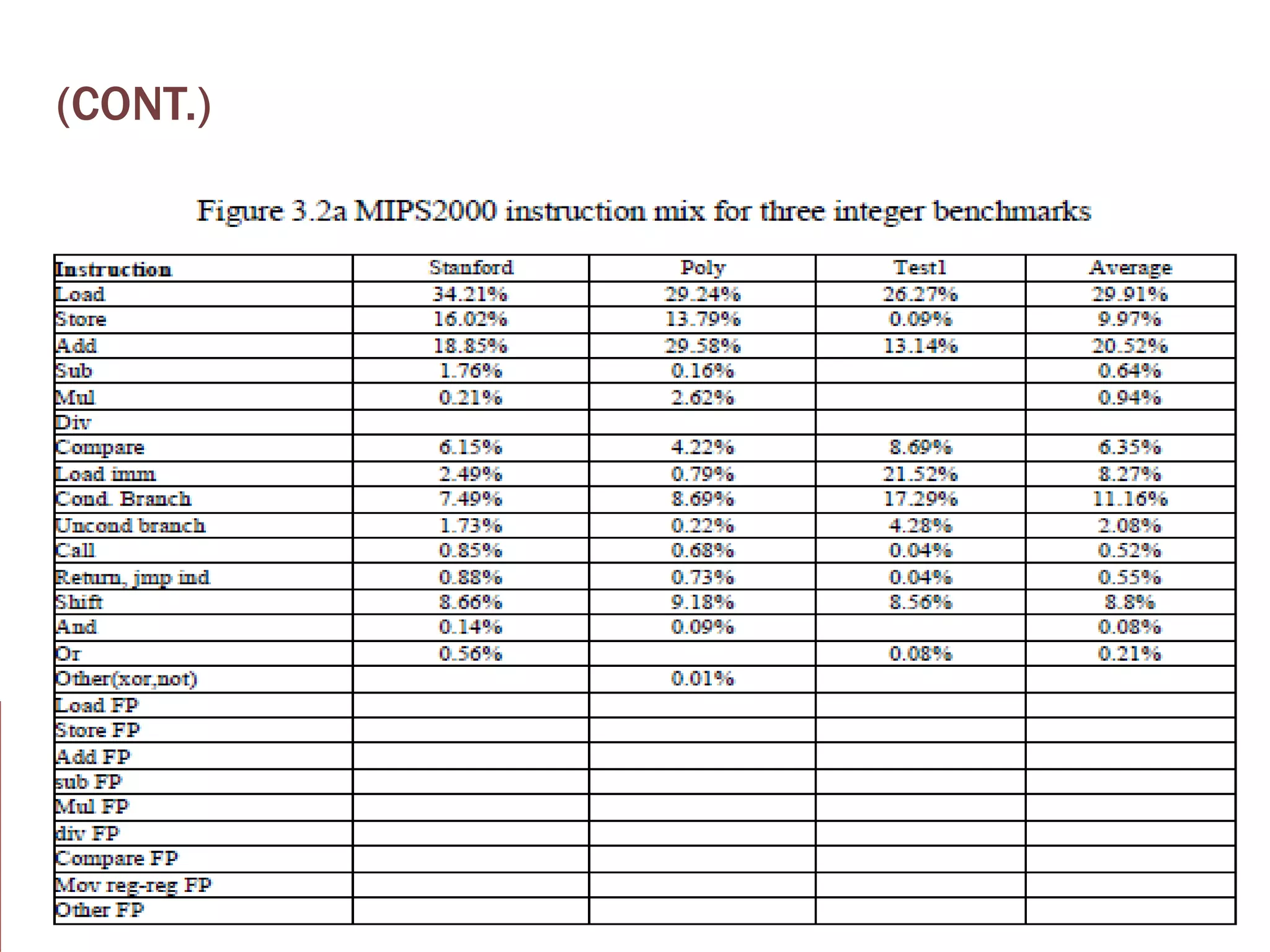

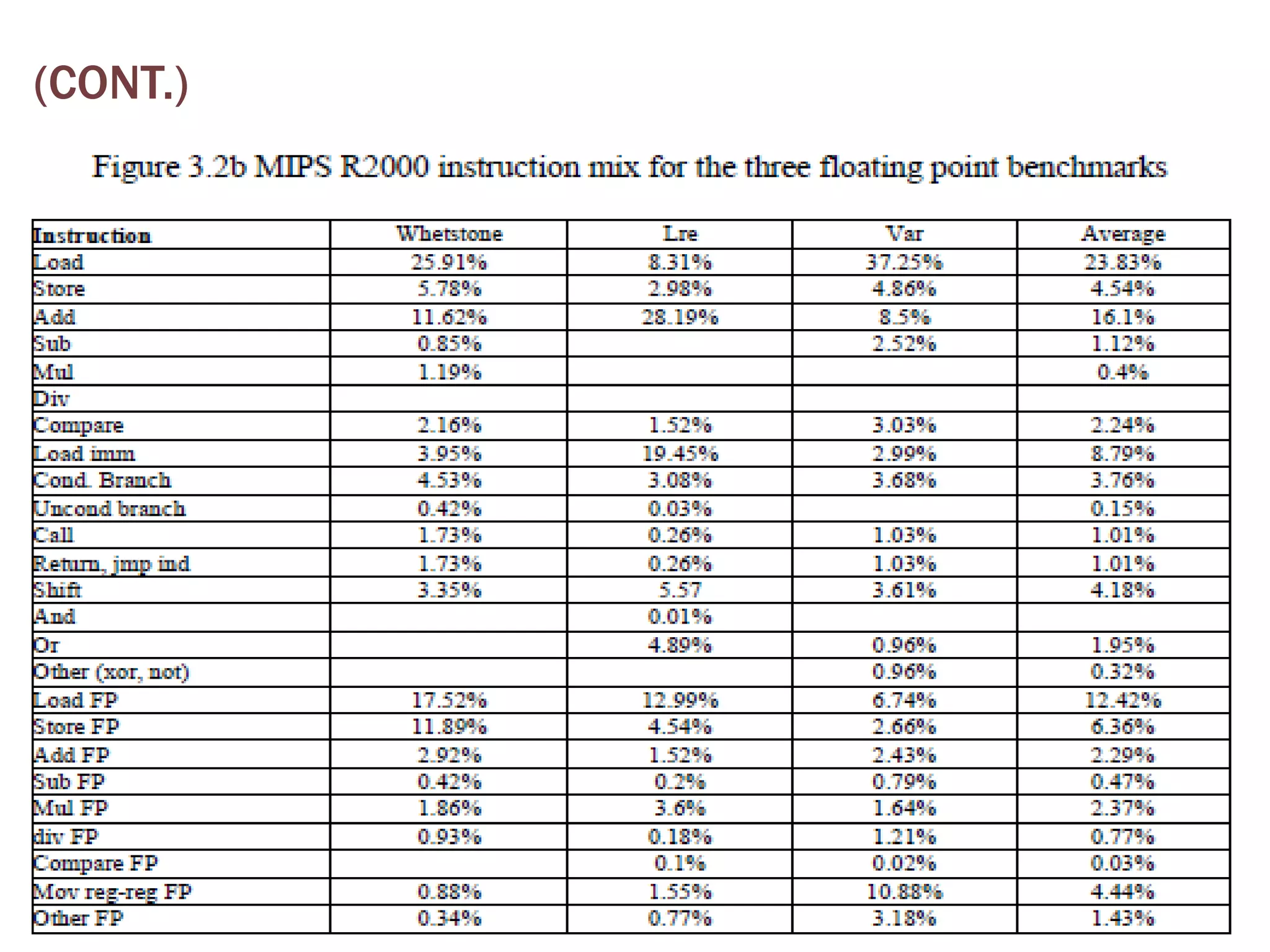

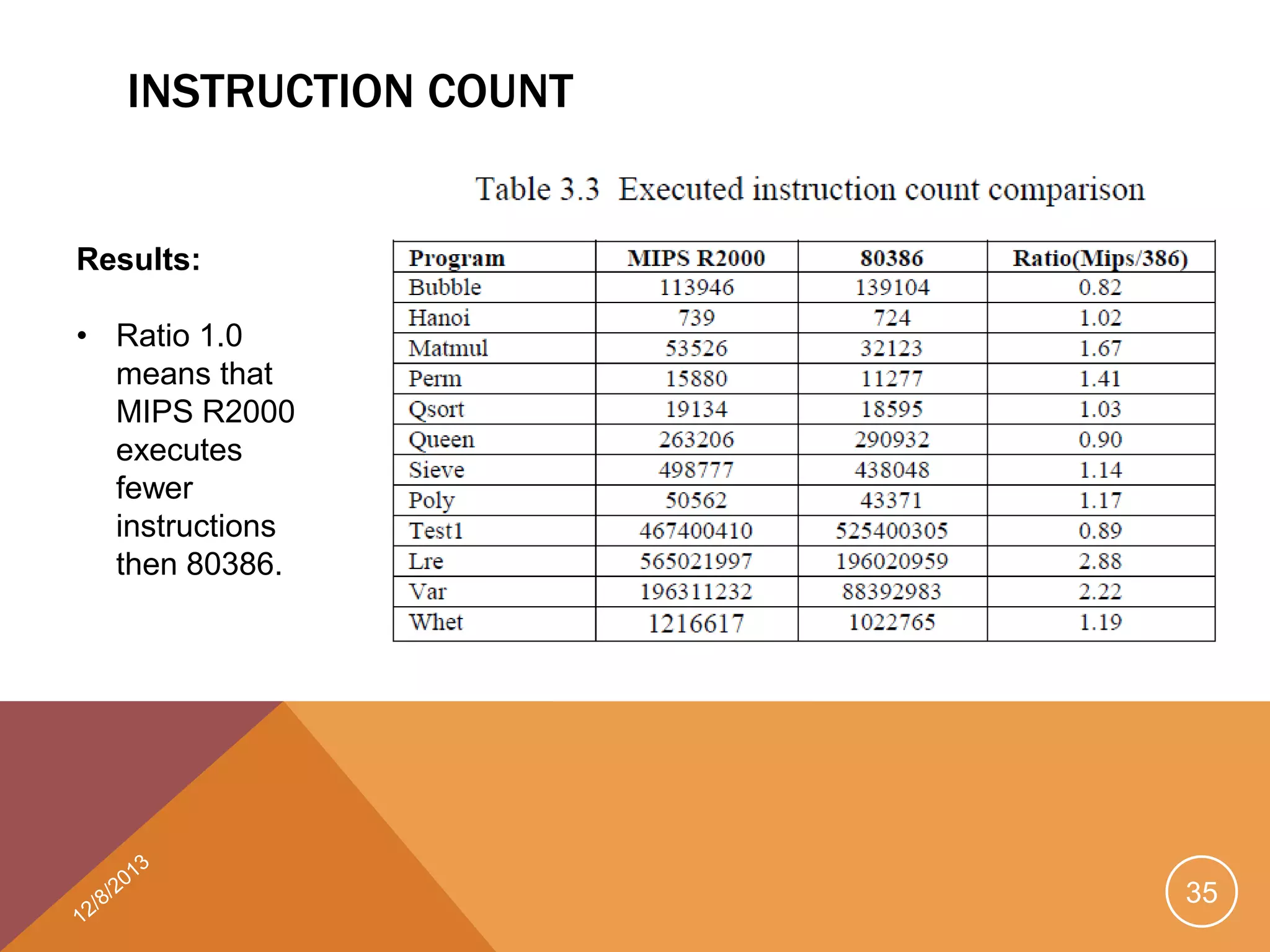

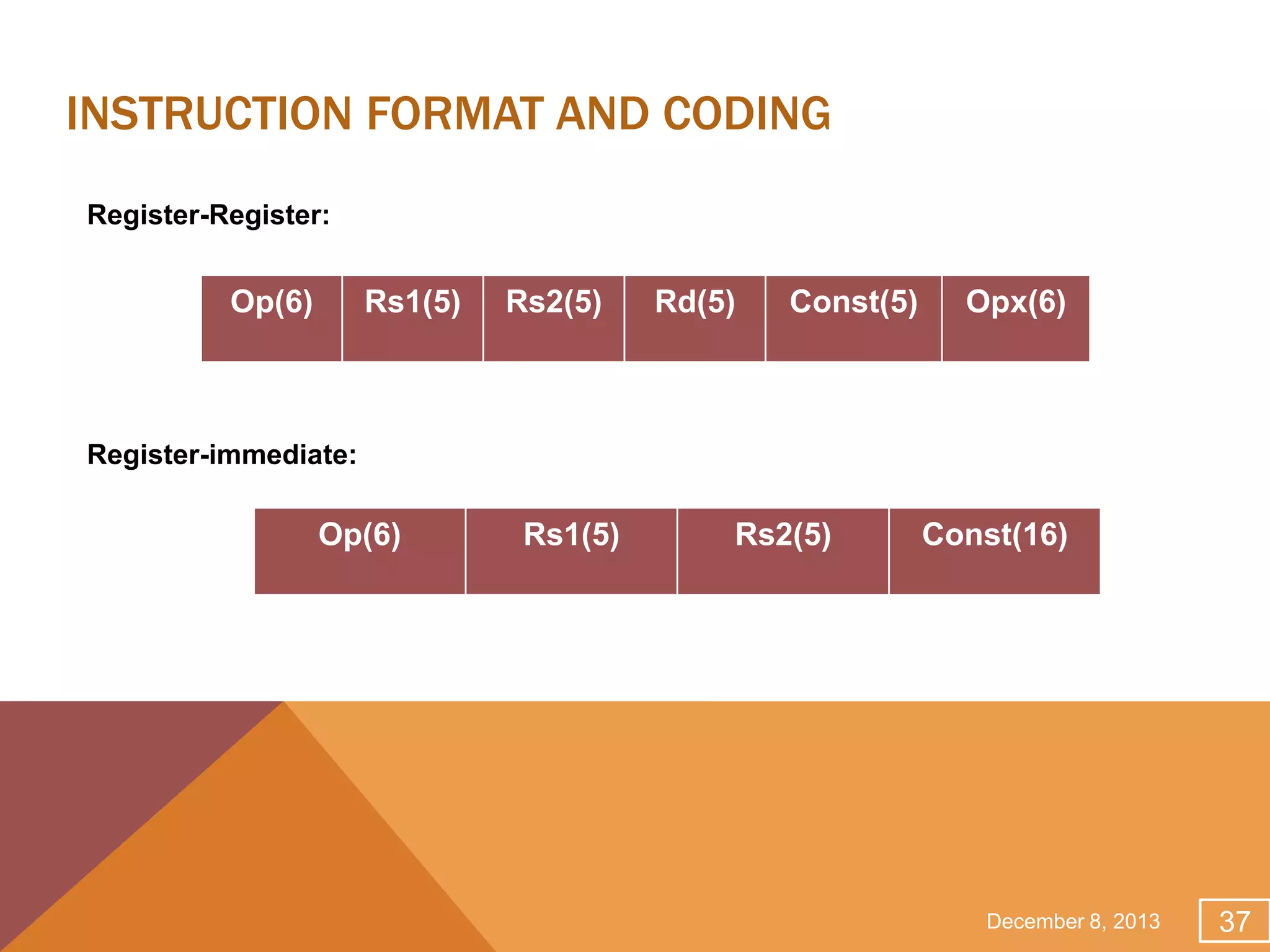

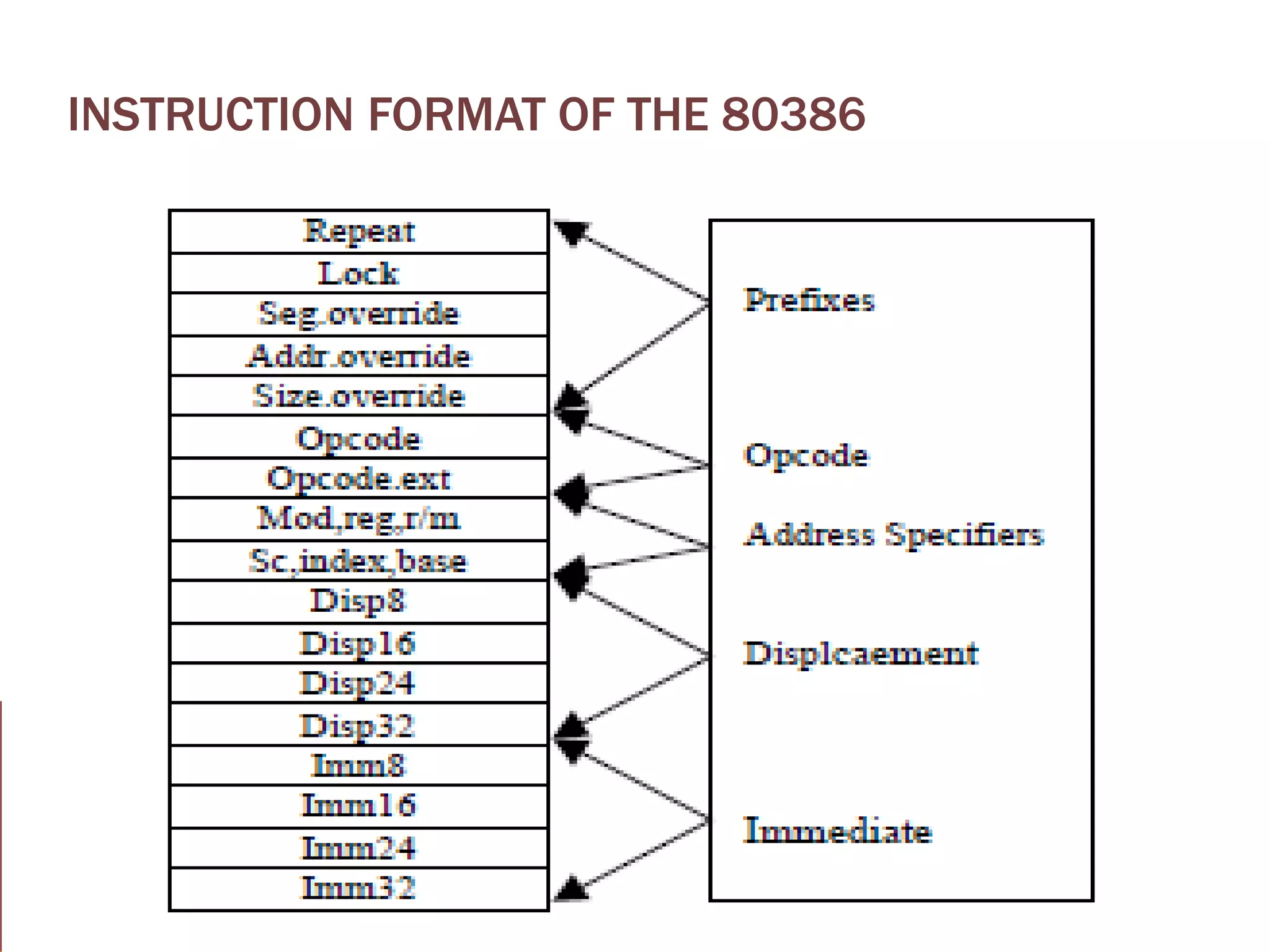

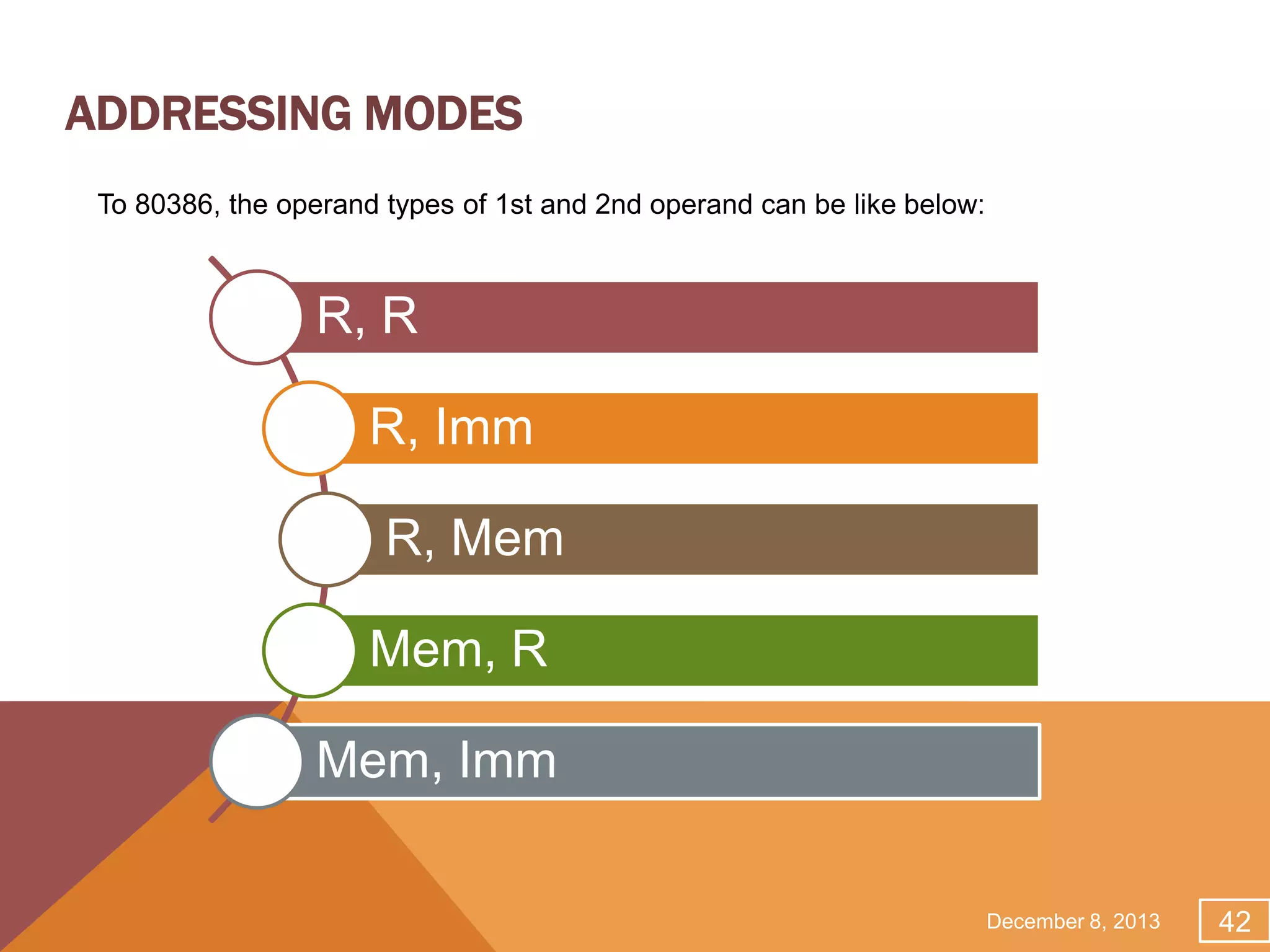

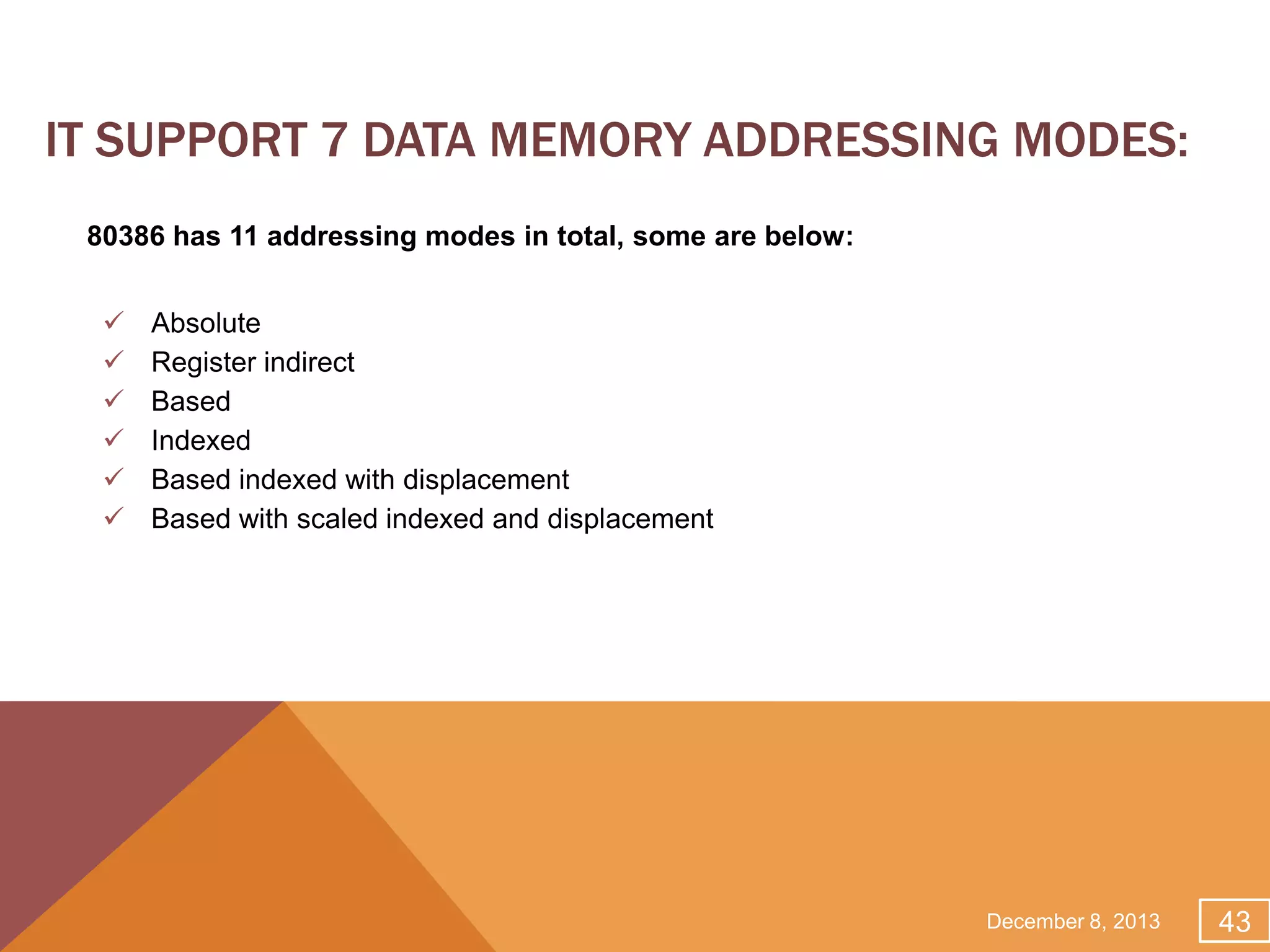

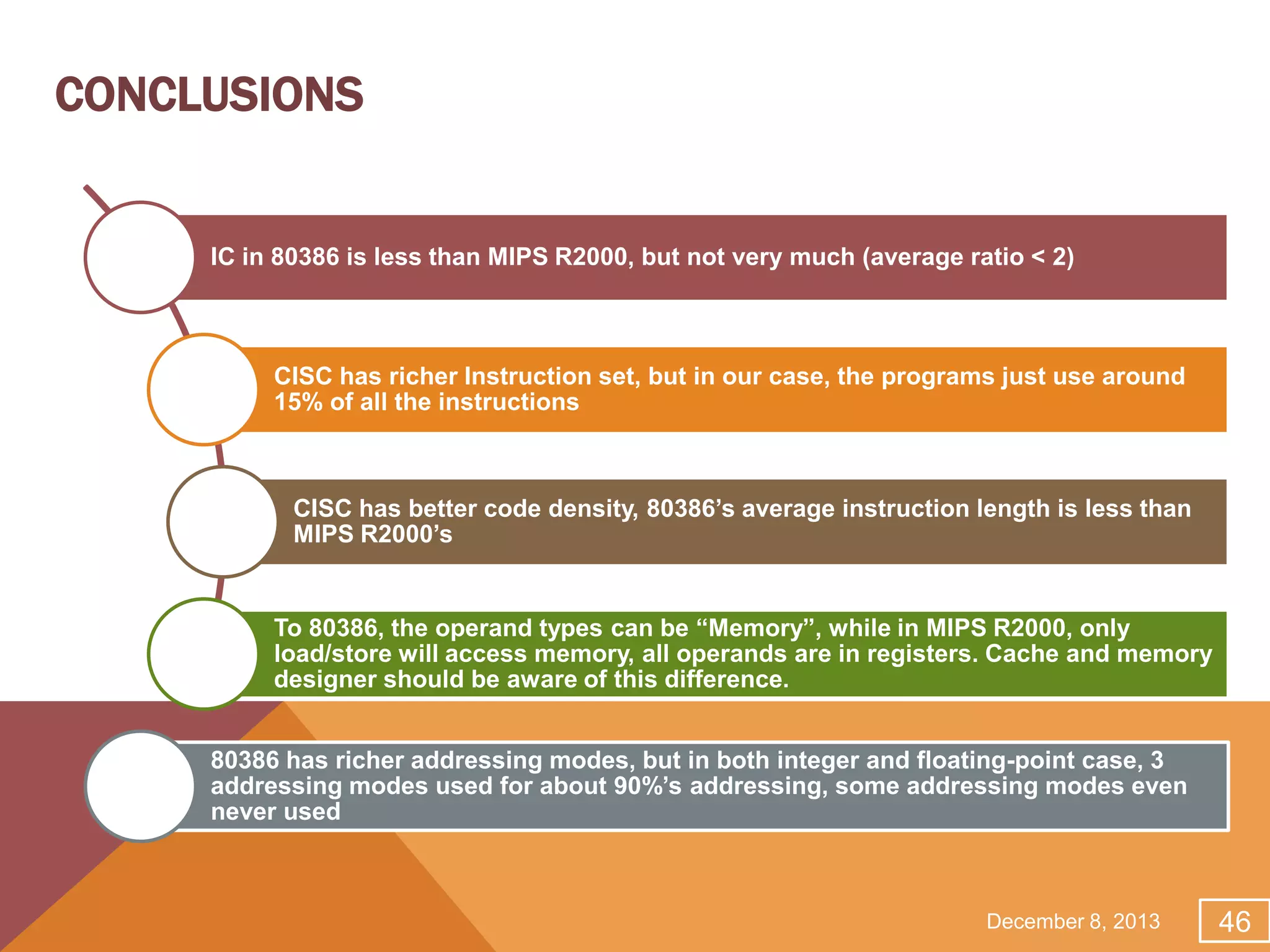

This document compares RISC and CISC architectures by examining the MIPS R2000 and Intel 80386 processors. It discusses the history of RISC and CISC, providing examples of each. Experiments using benchmarks show that while the 80386 executes fewer instructions on average than the R2000, the difference is small at around a 2x ratio. Both instruction sets are becoming more alike over time. In the end, performance depends more on how fast a chip executes rather than whether it is RISC or CISC.