0 ratings0% found this document useful (0 votes)

31 views27 pagesMP Unit 5

Uploaded by

rudrat9012Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF or read online on Scribd

0 ratings0% found this document useful (0 votes)

31 views27 pagesMP Unit 5

Uploaded by

rudrat9012Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF or read online on Scribd

You are on page 1/ 27

$255 Programmable peripheral Interface (ppt)

= SS ———

|

rour croura |. _PA

—T conwor KS = Porta: KS

CONTROL ot

power{—- sv |

SUPPLIES] —> GND J, PArPAy

|

| |

| GROUP A | rey,

1 porTG [ALA Y

BI-OIRECHONAL | Upper

Dae @ I Pop PCy

"— own [aL __ | —__t |

sus ———

in |

INTERNAL

DATA BUS roar ig | eae

o,PCy

ices [

oR ear

tare rou crours

* contxo. |-* +} Ae PORTS

8

CONTROL @)

oy) So

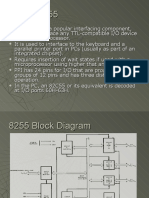

Fig. 14.2 Block diagram of 82554

\) 6258 PPL 1% a programmable peripheval clevice - 9+ can be osed.

to transfer data under

3) Simple ‘Input | outpar Condition

%) Strobed ( Inre Tsuph) Input | ourpat Condition

2) The denice have

%) 2 ports

#) Two 4-bit ports ( Port Cupp

bit ports can be Used Independe

together as one- S bit port

yol word Tegistes CCOWR)

( pertA and Fert B , each of S bit)

Q Port Crower) . these 4~

otly oF tt canbe usec

%*) 8 bit cont

3) post A and port B canbe used to precess $ bit parallel data

4) Port can operate 16

#) Single bit BSR Coit set] Reset) mede

#) to generate handshaki4g signals for Port A and Port B.

4% PCO to PCS generates handshaking Signal fox Port 8.

*) PC4 to Ply generates fandshaeg Agnat for Pert A

5) Ao and Ax line Is Used to Select the ports cr CWR

Ay Ao

© © — PortA

of Port 8

1 © —~ Poste

tL L — CWR

6) WR-2 When WR =0, then S085 ustites He cata cn pest pias

When RD =O, $085 can cad he data of ports through

data bus buffers.

Medes of Operation

4) Bit set/ Reset (BSR) Mmede -£

eS ee

x) Only port C operated fp His mode

3) We can transfer legic't’ or legic ‘0’ en any cne pin of Porte -

Without changing the status of siest of the pins

to de the operation wwe have to transfer § bit control word 19

belew format

07 be 0s Py pa Os Oi _ oe

[eo [ «T= Tx

. E T oF the Value ef De

if 0% aan Port ¢ pin selection is transferred into

iplo0 = Peo selecl&d pest ¢ pid

if 1 Tlo mode coL— PCL

aii. Fee

Exp> Reset Posty pio of 8255 having port A address EocoH:

selh>

alma oun = OGH ,

a4 a oo° . Reset means O

eee PCy pi

60C0H — fest A address

6oo1n — fort B .

6co2zH —— Porc"

Gee vegisley address

Program -

Mvr A, OEH

STA € 003 H

HLT

Control word for Parallel Tlo mode -2

kK Group A —__>1 & Greup 8 >

Ds | De \ Ds | Pa D3 Di] 00

a

{Se > Port Crowen

0 = BSRmede ‘42 cle

O=0lP

mode Selection. L—> fost 8

of Pont A 2clp

00- made Oo o-olp

OL - mode 1 > mode of

1% - mode 2 post B

O= mode 0

1= modet

Port C upper,

12tle

o- olp

>

Port A

is tlp

0=0lP

4

2) Parallel L/o Mode -3 ‘In this made & bit paraliel dato cwill be

a =a tronsferred blur tip and Zo device

there are 3 types of modes

il) Modeo ( Simple Input [output )~ ) There 5 no handshaking

ee 3) All ports. can be used

*) Outputs ane Latched

©) Input ports ave mot latched

Port Can eithes be used as & bit post on bS Upper /iower parts

can eperate endepencently

jl) Mede £ ( strobed Inpur/output) -

In this mode handshaking Signals ave exchanged between MPL (eR)

and external peripheral before actual data transfer. main features

Of this mede included

%) Port A and Port 8 actas § bit parallel To ports. they con be used

elthes as cnput om eutput port-

*) Each port cses 3 lines of portC as handshake signals .

*) Intemupt logic 15 suppvted

%*) Input and cutput data will be latched

*) PCs, PCy 4 PEs generates handshakiig signal for Port a

PCo,PCy , PCa generates handshaking fox Post B

cohen tath

pert Used

Qs tnput

port

‘ : hen both

* PCs, PC, PCy generates handshaking Segnal fer PA perrowd

Plo, PCs, PCa generates handshaking Cagrag fev PB [as ae

8255A MODE 1: INPUT CONFIG re

‘STB

PORT A INPUT]

Ter (Buffer full)

(NTR Lnterrupt request)

Data strobed Dataread by

into port microprocessor

Tirning Drageem

vy

8255A MODE 1: OUTPUT CONFIG

PORT A OUTPUT

Data sent Data removed

topo from port,

Timing Diagrom

This mode IS used when

Lle) -8

————" data has to be transferred blur

two computers (ox processoxs) oY data stovage derfces Such ab pen

daive or hard dist.

%) Only portA can operate 1h mode2

#) PLg —PC% will provide handshaking signal fos port A ,

#) Pert B Can operate Ih modeO oF mode-1. When post B operate 10

snede-4 , PCO toPCg will provide handshaking signal for Port B

Control word for mode- 2

i) When Post B 1s medeo

TILT XT XT XTOTT 1 pee-re;

| Cteue

Ports o=ele

moda -O

li) Wlhen Port B 15 mode-1

xT to

221 XTX)

Port

mode - 1.

Control word fox mode —4

é

eee

a) When PA and PB OS input post =:

ESCAESESCORRESE?

> net defined aa they provid

hands hdieing cic

posta ¢—_1

mede- 4

> Port B input 2

——> port B mode- 1

PostA mode-4. * PC6, PCy as tnput(s) or

as Lnpat

output (0°)

b) When PA anc PB as outpet port -2

——

porta 16 mede-s

—

Fort A as output

[4 | © lee 4

[tLe

x

°

—> Fort 8 ad output

Port B wmode-4

Pla Pls cd input( 4) or

outpar (©)

Exp> Detine Pext Aas tnpat powk 18 mode o, Port B as butpat

Wh rede £ and poxke Upper a8 Lapet - goss adaress

starts from 6oH.

TH Jia, [nap] pa [Pu] Me] ee] Pe /

(eealealeal t lox =,3¢ Cif xo)

3 * Ls oteill provide handshakig for

pest B

Pregrom—

mvt A,9cH

our 63H

*) GO Feat A aactd re se

61 — Pet B on

62— foto *

43a — CwRegrcler add ess

Programmable Intesval Timer ( 8254J63)

= me

Tt is not possible to generate an arbitrary time del i i

f n itrary tim lay precisely using

delay voutines- a

Intel's programmable counter) timer ( 8254) Is used togenerale

precise time delays

%®) When S284 iS usec for timing and delay qenecation > the micsoprecesso

becomes free from the task related tothe counting poocess and can

execute PIOgFaM Ip Memory.

This minimises the software overhead on the processor -

Axchitectuye -*

cael | Counter Ne

a ues

Replat eee) Garten

_ ovT a

Block diagram of 6254/<3 FQ: Pin diggracn

i ntecs +

%) B2r54]shas 3 lodependent 16 bit cour

*) oer have max count vate ot 1oMHe tere

%) These 3 countess can be Contsolled by 3 Command word reg! a

26) All Pnese counters are Udentical 5 presettable

to opescte either in BCD ov in hexadecimal mode -

3 down counters ,able

4) Arand Ao are used to select the counter

Ay Ao

oO counter ©

oye counten. 1

1 00 counter 2

1 L Control word operation

a2 S254

WD Mon. cloum freq 18 26MHZ 9) Max: clo Frey BMAg

yf) Does not have ead back command A’) gt has read back command

# Read back Commanct allowse the uses to chet he count Value, current

Stafes of ovt pin ond programmed mede -

%) Read and waite of the same

%) Read and waite of fhe same

Gunter can be lterleaved (mixed)

counter Con not be jsterleared

(mixed)

CLK-t Clock Isput 1% the timing source for each of the inteanal county

This isput is often connected to the PCLK Signa from the

‘microptoce ssow System. BUS Conhoiien -

2k) 9+ 1S also used to decsement counts -

GATE-% Qt i's Used to enable He Counter

When Gate = 4, counter will get enabled

out —% ulse output pia of Hoe Counter -

ouT-s p P

Contrel Word Register. -3

| sca | Sco RLt|RLO ma] mi Mo acd

— ~ L,. WW i

Z aaa - decimel

Countes selechen Mennins eae ecstasy

scr oe counto ‘Y= Bep county

a °

eo 1 counter! 0 0 O— mode O

4 0 Counter 2 0 O4— mode L

yo %K (Read back © 4 O-— mode 2

Command) O11 mode 3

1 oo — mode 4

i ol = mode 5

i to- %

Liv x |

Read | Load (tonite)

Bit definition

RLo

°

p

Fe

e

Latch Counter for "oN THE FLY" steading

C counter Latch Cornma

L —— Rood] write Jeast Significant byte only

© = Read | Atte Mask Sxgnificant byte only

1 — Reeds walle LSB frst then MsB.

Kr oo

Mode 2 € Rate Generator)

ee ee ee

®) St IS Olso Known ag divide by N counter.

% If N Is loaded as the count Value, Hren after (N~L) cycles , me oudput

betomes low for one clock cycle

® The count Is leaded again and the olp remains high for(N-1) cycles.

® It Gare pulse goes low , the counter stoxts counting from tnihiol

Value

ee LA Ee

me ‘starts Coudting « : —

Mode 3( Squone Wave Generator) a

Of ~ cperttion

Similan to rhe mode 2 PP nb pues HF vem low ond fo

*)

*) it Count value Nf even then for 2

lees it remains high: : .

ae fos (Qt) pulses output remains high Gs)

* 4 vee eh ylces cutpat rremaing loud (0).

ana ty (Nat) P

= SUT E

cs :

. 4 — 4 eee : .

OUT

WR

our

lo

(& loaded Ihbetween the operation 3

3

What happen if another covet volue

Mede 4 ( Programmable Monoshet) -s

ae zone ee

3) In this mode 8254 Can used as monostoble ™

#) Gate input is used as tagger input

#) OvT (on output) vemains high till the leeding of count and trigger i/p

y

Apter appling triggenLon rhe +¥e ecge ot a) 3 the ole goes low ad

cremains low till the count reaches AED -

¥) So low state of ole depends 09 Hhe count

int value, Hen cb will oof distusb rhe opemba

e fs applied ot the GATE texminal-

ultivibrator:

value.

¥) If we lead a new cou

till a new tagger pule

cLK [] re Gly

Trigger “/e

# Gare

Sperating, | Modes of 8254 -3 u

fccaeninetiied Ind

i) Mode Mode 0-3 (Intonupt on terminal Count)

#) output 18 initially Low after setting He mode

# output gemains low even after loading Hye count value.

%*®) on the next tolling edge of clock C apter loading count valve), the

counter starts decremenhng tne Count value. at tis time GATE

pulse should be + ( Gate = +)

8

elk SU SA

WR jens

eas

eee ee _

Gate ge count —_ coust=4

OuT a whent

Countso

is loaded into counter

#) Attar leading and GaTE=4 , the counter stots decrementing from

374 clouk pulse -

® Apter 4 clock cycles (4M, 5, ehh and 7) y the output will switch

from © t6 4 which is known as interrupt on feaminal count:

What happen if Gate pulse goes low inbetween the operation’

x * i

-_ - - eh gh

mann

out :

Bolas Bot a8 :

e—_—<$+_—_—_.

fe SS SE a

' : , 1 ’

1

OvT ; ;

Mode 4 ( Soft wore tnggered strobe) ~e

©) Allows Hhe counter to produce q_ single pulse at Phe output.

38) if SK leaded hen cur will be high for *N? cycles and hen low

for one clock cycle at He end:

joaded again.

4) The cycle does not Fepeat untill the counter. 16 I .

4) Counter starts counttag after first falling edge ef cleck and si'sing edge.

of write Signet -

ck 1 me ert

[’iood Hye count valve and stants Counting

ig ig 2 we 1 fo. Fo?

Mode 5 C Hardware triggered mede) ~F

ete SO PON ONG I

%® This mede IB Used to generate a delayed strobe cohen

a trigges pulse at the GATE pin by the exteinal hardware.

3) counting begins when GATE pulse 1% triggered from Low te HIGH:

Phere Is

cuk SLT LATE AAA

ro re

Gate (tagge) “ . ae °

b

eaten device

OvT —

Gate

CL a7 - 5

823% DMA Controller

—_*« x—

DMA stonds foy Direck Memory Access. Data transfer blo Lo and

memory tokes place by 2 ways

1) Through iAshuctions ( Software mode) —8 Im pis mode of transfer

transfer reteis very lew.

rE

St is not suited for bulk data tvonsfer

2) Through External Havdiwave (Oma) When a peripheral wonts to

exchange heavy omount of dats

with memory , ‘Ub tekes the helpof OMA conlreiier. the OMA controler

transfers Fhe control ef buses from cpy to externa! priphers! Lo

device: external peripheral devices like Hard disc, Sound cards , graphic

cards ctc uses OMA Controller for dats trensfer

Block Ciagrom and signals -!

Deen SE

rama Bus

DMA Request ©

sbit ey

Data bus { nee DMA ACKNOWLEDGED

eee

4 On :

neset — pant sear me

© Ao ae entra PORT 7

HPS AS) => Ho

aol devices

a Sar fone?

haa

45<— A008 | PORK?

BE Sloan

READY — >} 190

ot KS

spe >| Sah foros

wats or | poem

1X =

ose «| |

pe t

Prony

CEBP) wank < resstver

Fig Block diggrom of 823%

) 823% Con tronsfer 64kB dats at aq time

iG odes — ff DMA ead

x) St opeates 19 Sm #0) oat

#OMA Veoufy

#) 8234 hao Bbit dete bud.

4) FOR , TOO ave used for Tlo eperation and MEMK ,MEMY

signals are Uasd for Memory solate.d spuahins.

* 3234 hannels

hao =) c el che to CH3.. each chenne] ¢

Connected ith only one pempheral device jon be

) 8234 has Priority siesolver unit

Init to Hesolve the ‘

chonneL 0 to chonnel3. : eerste

¥) Each chonnel has (

aS 16 bIt Current Addyess ‘eld

le bik current wore Count RegisleA CCWR)- aici _CcAR) and

CAR holds the storing address ef memo OM

cohere

Gee ee eee af oa)

oof Byles thet hae jo be transferred in DMA ope

"

CWC holds he 1

3) 223% Can perform Memory To Memorp » Memory to tlo + tio to

smemory transfer»

*) S23F ppersites on MHz to SMHE

4) cascacting of 2234 Gan be usad fo herense the number of clerrices

*) 2 M88% of count Regislar Cer) defines the typeot Oma operechon’

Le bit

[>e[oToo[daloe le: ee] cn Rogisle Cor)

lue>

EF ia Bits for Count val

© © oma Verity

O 4 OMA Write

LO oma read

4 4 legal (x)

2) Nowmolly one OMA Cycle comsumes 4 clock cycles (54, t0 $4) but

B23at provides compressed timing to improve thsoughpet of He fn.

c compvessed Firming 5 pot valid dusing ‘memory to memory +0:

Function of Impostant Signals ~*

anaes re Active Hig Sin

_. B Signal generated by extend te device

88 Fa] 3) DRQ= L meons external peripherot wools

te Contre) of Syplém bused CDatO » address +

CORRQO tO DRa3) conte) bus). |

achive HIGH SisreP:

*

DMA Acknowledge ( ACK) — #) if goSs] Boke *eleases the conlvel of |

buses then B8a3% genoa PACK signal

DAK [z1e| fo isaicate zlo denice hot pnp, peamissia

we granted:

Coacko * pAcK3) When OACK= L , thot means external t/o

device can access MeMeTY without up BpU-

Hold Request CHR) ~: we) Active HIGH cignap -

3K) HR@= 4 Indicates Up tat any extern?

Pele 2237 device usonts Me Control + Sys lim bua

oma Request CDRR)

Hold Acknowledge ment ( HLDA) — ise

*# Active HIGH Signal

3 When HLDA=4 , microprocessor tells 823+ that he &

steady to transfer the Control of Syslém uans «

Fermina| Count (Te) =! When the contre] word cont Cewe) valu

H e

exhousléd then 8237 makes Te pid HIGH

To21 indicates Mp that Complete dats byles han been tronsferted

End of process CEOP )->

% Active Low signal - C Bidirectional )

2) EOp20 means pmaA transfer process hap been ended:

4© When up wonts to Stop the OMA process, it mokes EOP

pis Louw.

3) When BABF sieaches or exhousléd He coum

Zor pid active low

+ Volug , it makes

rol

Ax

AY TS of S234

aS

pe

ate ane Ca llinee alec cca a generate chip gelect logte for 823%

# Yo "© selecléd when Aq As AE are 000

¥) for Eo te at loge O 2 Ay =O

a Aq Ae AS At are alocys O000H

W® Ag to Ao lines Ore ured to select different Regis)ers of S234:

Aq AcAs 44 Az Ar AAO

o 028 8 20600 = OCH CHO MAR 0% CAR

ooo Lt oLH = CHO CWE

chip Select oo te o2H = CHL CAR

ook t OSH cHs CWS

fot) oF 2 cee cleor mask register

4h 4 F OFH Alt mask vegiste

#) CWC = Current word count ww

#) CAR = Current Address regutes, also Keown ob Memory Address reyl’s'

if Reset= 1, then b

Register CCR

Ree Repti c (<8) pu these registers will get cleared -

Request Register

Temporary Regi'sl

8234 will enter into slave mode if Reset= 4

Reset -3

Ready -+ (REAOY)

3) Active HIGH Signal generated oy YP

#) Used when 8237 operates lb Maoten mode-

4) Master 823¢ adds woit states th oma cycle if READy= O

AEN-I( Address Enable)

When AEN= 1, Higher orders address bus (Ag- Ais) will be

available -

ADSTB -% C Address Strobe)

This signal 1S Used to contol Latching of upper address byte

(Ag-Ris)-

Ao- Ais

Oma Data Tronsfer Modes ;

a >=, 2

4) Single Transfer Mode =

36) 823% tronsfers only one byte (Bits) ih this mode

24) After each transfer, word count register Oil! get

Current address veqistes coil get incremented or clecre mentesl

3) After tronsferning one byfe , the 9237 disables HRQ and enters ine

idle state or Slave mode. gt is also called os “cycle brealing mode”

» tt disables He corresponding channel

decremented and

4) When Tc f reached

2) Burst oy Block Tronsfer Mode -!

*) All bytes are transfered continuously +

4 HRQ= Active HIGH during all the DMA oO

@ vy word Count register C yelling from 00 tO FFIO% EOP

any external medium -

OREQ must be held active aorill

RES °

ones Sar oma fs acxnosletged

3) Demond Transfer Mode ee OACK OMA REB IS disabes:

— wee *

peration untill TC =

© Back becomes active

ered %& contsolled by Ilo device -

#) The number of bytes to be teansfe

peration by

*®) The Ilo device C0 terminate He o|

5 activating Bop signal Cre Eop=0)

> Disabled DRED Cte DREg®=0)

\& disabled), He 823% stores ne intermediale

*®) When DRQ=1 ( DREG

Current Count and address

value of Count and Memory address 1%

ogisl& respect ivaly -

4) EOP. signal & Used when outoinitialigahon | Enobled -

+) DREG i used when auto Inihaligation 1S dhisabled -

4) Cascade Mode -*

So eee

40 ‘This mode fs Used to cascade ‘move thon ©

the number of channels.

#) Fig below (1 next page) shows the connections of meoter and

Slave OMA contreliers.

2) In Cootedes! mede 823 activates only HRQ@ and DACK Signals -

ne 823% to increqce

24 Level

=

fa

uP cele <—- ——_nees

HOLD HRG on ————7]4-08 |

HLOA HHLDA

| |

| pre HRE

onsf oA 3 HED

Master

S237

3) CHO and CH3 are 19 Cootaded ede

Slave $237

Fig Capcading of 823%

e234 openating Mestet

ee,

value of current add re

L) Autoinitiolization Mede-3 In this mede

yy word count Cewe)

ee

are automatically sestored from base addnre regisla and ane

wor count rrogisi® » The values are -eestored only cohen Heve

(3 on EZop signal gets activated of Her 1S TC-

©) Fora Auteinitiolization peep ‘mode should be Selected +heough

mode vegisler CMR).

2) Priovity Mode 623% operates th +00 pevowity medes

Rotating Priovity

3) Chonne| hich 1S Cuvrently active

hap highest priostty: abe

Sewice it will get lewert

priovity .

fo N

on CHL

~ ce

Sowice» jst 2nd st

Fixed Priostty

#) CHO has highest and CHS

hao Lowest pmowity

currenth 9 2¥ 3

oS hie ra ee 3 8

. ©

poonky and 3 ar 3

being Seswited -

. o OMA cycle has 4 clock pulses 11

3) Normal Timing Made “i Ech y P

me = i

4) In normal timing made IOR and MEMR Signals are ochvated

during 3°94 clock cycle and 4h clock cycle -

® TOW ond MEM will get activated during + douk cycle.

T10s1) T2(S2) 73 (54) Ty (54)

LELFLE LIL

*) S for stale

(aR) Write + tFr

# Aclock cycles

Compre ssed Timing Mode-+ In order to achieve greater,

4) eee een thwoogh put , 823% can Compress

the OMA cycle to 2 dock pulses -

3%) In compressed trening mode only S, and Sq needed +o Complete

one oma cycle «

S284 Sp 54

mort |

= 7 |

RO it

we !

#2 leek cycles

5) Extended bivite mode

+) Not Used 16 compressed timing made.

#) Nosmally used for slower clevices y BA by Activating the ussite

Senal CMEMW , TOW ) 1h 3™4 clock eycle C Sa) -

St Sn 83S

LDL LT |

mw { I

WR —— yt

Cae write signal fs activeled ward

dock eydle , denice usil] get move time +o

write the data -

Progvammoble Intertupt Controlley (Pic) 8259 /ae)

x x

*) 9259 IC {6 e@ programmable IC used to expond He intersuphs

of 8085.

*) One 8259 Con accept $ Intersupt requests ond allow one byone

through INTR pin-

3) Cascading canbe used to expand the interrupts upto 64.

%) 8259 manages the fntersupts according to the instructions . writen

into its control register

#) The peiovities of interrupts are programmable .

How 8259 Works?

ee A 8

First 8259 1% progrommed by sending Toitialigation Gmmor

words C TCWS) and operational Command words (OCW Ss). These words

will isferm $25q about

© Type of interrupk Clevel triggered or Gage triggered)

*®) Type of processor (Bo86] 26)

%*) Call address and its ibtewal (4 or 3)

*) Masking of interrupt

%® Priovity of linterrupr

*) Type of End of Intersupt ( cot)

once 9259 iS programmed with these Command words Lt

becomes Teady for accepting (ntesrupr Stgrals

Steps of Servicing -%

eT A _

%) First 8259 Tecelves the iotessupt and et will check wheher_

creceived istersupt 1S mapked oY Unmasked:

4) 9t also Checks the priowity .

4) Th Here & po pending fnterrupt fom last stequest and Current

srequest han highest priovity 6259 Sends Signa) on INTR pla .

%) T4 processor & ready fo accept Me vequsst i+ tends & INTA

Clow) pulses one by one-

TRTA ('0" for3 clock pulses)

FuncHonal Block diagram ~2 25q hap S functional blocs 2

FuncHonal Bleck diag"

gwar send INT sgnal to INTR pin of 808s»

4) When Hne processor occepted Hhe request, BOBS £erdo

3 INTA Clee) one by one

ie Tie — TZ TA

yt ts lL

NTA a i ~

es0~C<“‘<=s~*wSY

ual ““GpperwyTe of call addwess

1) Contre! logic -

1

lower byre

Of Call address

Once processes receives CALL opcode and address » tr saves Hhe

Current content of PC 18 STACK and Start executing the TSK

DATA

ore CN) hus

BUFFER

INTERRUPT MASK REG

(WR)

INTERNAL BUS

2) Sbit data bus buffer tO %*) Send Control worel foorn Goes to

Intessupk contsoller -

34) Read the status of B8S9 (by 8085)

#) send datq

S) Read write logic -sx)The BOBS uses RD, BR and Ae to perform

Sead wr~0ile jon +

*) CS is used fo gelecr 8259 TC-

4) Interrupt Request Regisl& (ZRR) ~EH)9F is an 6 bit regisle

ye) Qt bas & lines CERO to Rt)

*) Gf any of the line & high , tt will get stored

lithe Commesponeling bit of yeghe -

e . 2

5) Interrupt Maok Regist CIMR)- gt 1S on wbit veglsle ushich

ee WA Pe ee : « e

Contains isformahen about macking

of any frtewupt Ifne. This regisler gets datz trough ocw1.

6) In Service Register (ISR)-2 gt keeps treck of ewhich interrupt fis

ee Cupnanhly being saviced.

3) Priovity Resolver -f This block sesolves the psiovity ff bere ave

Rn ee d

‘more Than one InFexupt at a time.

8) Cascade buffer /comparatyy -2 at fs used when 8259 fs used 1

~ _aee eee ‘master clave ede ( more than one

gosg rc {5 conneclad to S0eS).

Initialize command words (rew*) 2

Toitialige Command wowds Lzcw

; Ic Commands ave used to load Fhe inteanal conbrel

vegisters of £259 to speaty the nets of operation of B254-

Hhere ane 4 command words configuration

*) Tews

® Tcow2 (stores details regancuing intereupt vector address )

*) Icw3 ( Used i) Masts /slove mede)

*) ICW4 ( Used 16 8088/86)

Hhese command coords are used to inihalize He S259 IC only

Operation command words Cocws) -

eee Oe , 7

Once Phe 8269 1s initialized , rhea 2+ becomes

ready to seceive he intersupts* the 2269 acceprs rhe varercupt

Request on its Own way called Gs mode of opashon- nese medes

of operation can be clepred by 3 Command words

#) OcWL — ( Used to access the content of Mask regi'cles )

#®) ocW2 selechive maskhg of idtesrupts

se) cca . 4 Cused te select the peiority schemes)

Cat permits the Heading of Content of ISK, Of IRR

fisough se¢t wae)

3) ICWs and LCW2 are Cumpolsacy Command words.

iL A,z0 and D4 Ll, then conhe| word 13 recognized as

IeWws- it contains .

#) Edge/ level taggen9

#) sitgle/ Cascade mode

%) Cal) address toterval

Whethar Sea is needed om not

Lew

Iewt -

Ao

itL , Cwy needed

Ifo’, TcWa mot needa

————_

used in Go@S only

#®) Az toAs bits of

intestupt Vector

adaress

4) Dodt Care th BoR6

1 = Single

© = Gascaded mode

Address Infexval

— 4 = interval of 4

as Sage ae 0 = wtesval of @ bytes

39609 3) for Bogs ADI =L

sa, then srs are 4 byte apart (0200, 0204 ete).

if Aor<0 Hhen TSR* ave @ byte apart (0200, 0208 etc)

ECW2% if aps, then Cone! word i vecegnized as rena?"

*) Ot stores details oF Iotersupt vector addresses .

Ao Dy De os D4 03 P2 D1 Do

CE] Gee TLS eel A TAD oy oot meet

Sg Ore lines of proceso”

28) For BORS Syslém All the bits ave filled by Aig “Ag of Totewcupt

vector address -

3) For SORE

Te = Ta ave the 5 mest Significant bits of Intessupt type by te of Beat

Dlo- Ag defines the type of iotesoupt for xp IRo = 000

brie eee IR, = OOL ete.

: L These bits ave Onginally held at 000 Ciro). tf ony other

| Wtertupt fs Here the 8254 automatically add rhe number to boat

Co value of Ro to get the sight isterrupt:

X) Icw2 isdicalés & bit vectos addwess 14 case ot S086 and higher

wyte ef ISR address 14 case of PORK

When SNaL bit of [CW =0 Hat means £259 15 16 Cascade

amode ( Mastes/ Slave mode) -

# Tawa f the stead only Command coord when S259 openales 19

cascaded nede-

%) rows holds the & bit address of Slave.

Icw3,

Peete alone st ) coeetleh res MS = eis lew,

(K the Bbit Slave vegisl® will be cet bit wise to 'L for

each slave iy the Syslia-

Sp veprecents IRo

Ao 7 De Ds Py D3 Da Oy Do aaa

2] [s]selss Sq [8 [s-[s,[=| és veprecents Ry

agarose

if Spe 4 then Rn has a slave

© then IRq does mot have slave

Exp- let IcWZ= 00000010 ‘

- L» IRL hada slave

cane 2°: In slave mode C5P=0 ominsuffer mode M/s = 0 ,BUF=4 Is

Itw4) .

A = 1. (eee ° © [x,[z0,J is]

#) Slave 4 on IRq will have oS

ICwWs = 0000 Of 0d (04H) ose — =Ro (Slave 4)

s'ti— IRF (Slave 8)

ICW4 -2 4 5 x

if req bit 1 ICWIs 4, then only Tewg will heeded.

% Gt 1S Used only with BoRé/ Bose -

© | © |o |senm| BUF [ris AGOT| mPM

[5 02 S085 mode

special Fully Nested come oe

S selected

rope if4 then Automatic End of

y - Intersupt mode it

enabled

M|=0 then B8Sq Isa Slave

4 then ©2859 180 Mavley

»#)ifauFs0, MIS ts Negte clea «

ee ee

15 selected.

lo the wufferrd mode sP/EN

actas enable and

maste, / slave | determined

using MS bit of ICW4-

OcWi *~ 9tis used fov

yO Access the Content of maok vegest

36 Selective masking of intessupt inputs.

bo

1 [eg [ me] Me] my [ma [Me To mo |

if bit= 2 sthen Mask Set

© 5 then Mask Reset

ate

let we want to mask ZR2 ythen Ma bik shouldbe 4

oo ocwi = 0000 0100 =04H

ry Sel jowitie inte’ FS.

Ochi2 <2 Used to Select priosities of intesrup

T Bleeder ET)

J

Level of tntersupt

End of 000. Z£RO

Intessupt ool Ri

specific. Rotation oO 10 tR2

Automatic Rotation Of ERB

1 06 3Ry

{or Rs

110 =ZREe

4

IR7

R SL EOL &

° ° 4 —= Non specific EOL Command (in Fully Nested)

° :— speci fe E0L command

1 ° 1 — Rotate on non specific GOL command

1 ° oO — Rotate 4 Automatic EOL mede (set)

° ° 5 — Rotate 19 Automatic BOz C clean)

a 1 1 —-Retate on specift BOL command

e

— set priority command (Lz-Lo we used)

* ‘ © : 8 C 19 Hhis mode

6 4, Oo — No openartion

OCW3 - Gris used to stead the content of TSR om LRREhroUgh Sof tion

Ao cy Ds De Os Da Di De

L\o fests] 0 | 4 P an ats]

—

oO oO v

re °

Reset spedoL —> 1 0 1 0 — Read. IRR on next

Mask, RB pulse

Set special L

Lasts, oe 1 he Read. Wm ISR 07

next RB pulse

EsmMm-— Enable special Mask mode P= 4 Poll command

srin— spesiak mask mode - © 0 poll Command

Priority Modes at

i ee

L) Fully Nested Mode -% )In this mode ail Intervupr Requests C IRS)

on ee are arranged from highest to lowest

® Any IR canbe assigned the highest priovity

Let IR has been assigned the highes priovity then

IR, IR, IR. Re TRe IRs TRe IR7

4 Ss 6 + ° L 2 3

t

Lowest Highest

Priovity Priority

*) TE we hove not assigned the highest priority to ony TR then by

default TRo wil) have the highest priority end IRz cil) hove the

lowest priority

2) Automatic Rotation Mode-3 In this mode an IR being served,

seceives the lowest priovity.

let IRy has Just been served , then

Ike IR, IR, IRzg IRy Ike TRe TIR7

s 6 t ° L 2 3 4

Lowest Highest

priovity priority

3) Specific Rotation Mode -3 #) Similan to automatic rotation mode

——— exeept thot He user Can select Ony ZR

for the lowest priowity:

thus fixing all other priosihes.

End of Tnterrupt

1) Non= specifre EOL -t When this command iS sent to 8259, +

rresets the highest priovity TsR bit.

2) specific EOL -2 This commond specifies which 1SR bit to reset.

a

3) Automatic EOL 2 %) No command required

*) puving third (3"4) ENTA pulse | ISR bit

(8 reset.

You might also like

- 8255A Programmable Peripheral Interface - 8253 Interval Timer - 8257 DMA ControllerNo ratings yet8255A Programmable Peripheral Interface - 8253 Interval Timer - 8257 DMA Controller24 pages

- 8255A Programmable: Peripheral Interface (PPI)No ratings yet8255A Programmable: Peripheral Interface (PPI)26 pages

- By K. Vijay Kumar Assistant Professor Dept. of ECENo ratings yetBy K. Vijay Kumar Assistant Professor Dept. of ECE31 pages

- Lecture-43 Intel 8255A: Programming and Operating ModesNo ratings yetLecture-43 Intel 8255A: Programming and Operating Modes8 pages

- Jiunkpe Ns s1 1998 23492070 14716 Timer AppendicesNo ratings yetJiunkpe Ns s1 1998 23492070 14716 Timer Appendices20 pages

- Programmable Peripheral Interface (8255A)No ratings yetProgrammable Peripheral Interface (8255A)27 pages

- Programmable Peripheral Interface 8255: Microprocessor Unit 4 1No ratings yetProgrammable Peripheral Interface 8255: Microprocessor Unit 4 132 pages