0% found this document useful (0 votes)

60 views31 pagesVerilog Interview Qs

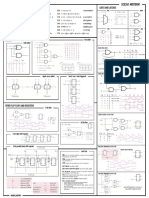

The document provides a comprehensive collection of Verilog code examples for various digital design components, including a half-adder, multiplexer, flip-flop, ripple carry adder, and more. Each example includes a module definition with inputs, outputs, and the logic implemented using Verilog syntax. The document serves as a resource for mastering Verilog through practical coding exercises and implementations.

Uploaded by

sindhuravemuCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

60 views31 pagesVerilog Interview Qs

The document provides a comprehensive collection of Verilog code examples for various digital design components, including a half-adder, multiplexer, flip-flop, ripple carry adder, and more. Each example includes a module definition with inputs, outputs, and the logic implemented using Verilog syntax. The document serves as a resource for mastering Verilog through practical coding exercises and implementations.

Uploaded by

sindhuravemuCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 31