0% found this document useful (0 votes)

14 views11 pagesLecture Slides 07 071-Caches-Basics

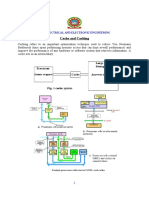

The document discusses memory and cache concepts in computer systems, highlighting the importance of cache in addressing the processor-memory bottleneck. It covers cache basics, memory hierarchies, and the mechanics of cache operations, including hit and miss scenarios. Additionally, it emphasizes the performance differences between CPU processing speeds and memory bandwidth, advocating for the use of caches to optimize data transfers.

Uploaded by

yihuangeceCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

14 views11 pagesLecture Slides 07 071-Caches-Basics

The document discusses memory and cache concepts in computer systems, highlighting the importance of cache in addressing the processor-memory bottleneck. It covers cache basics, memory hierarchies, and the mechanics of cache operations, including hit and miss scenarios. Additionally, it emphasizes the performance differences between CPU processing speeds and memory bandwidth, advocating for the use of caches to optimize data transfers.

Uploaded by

yihuangeceCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 11