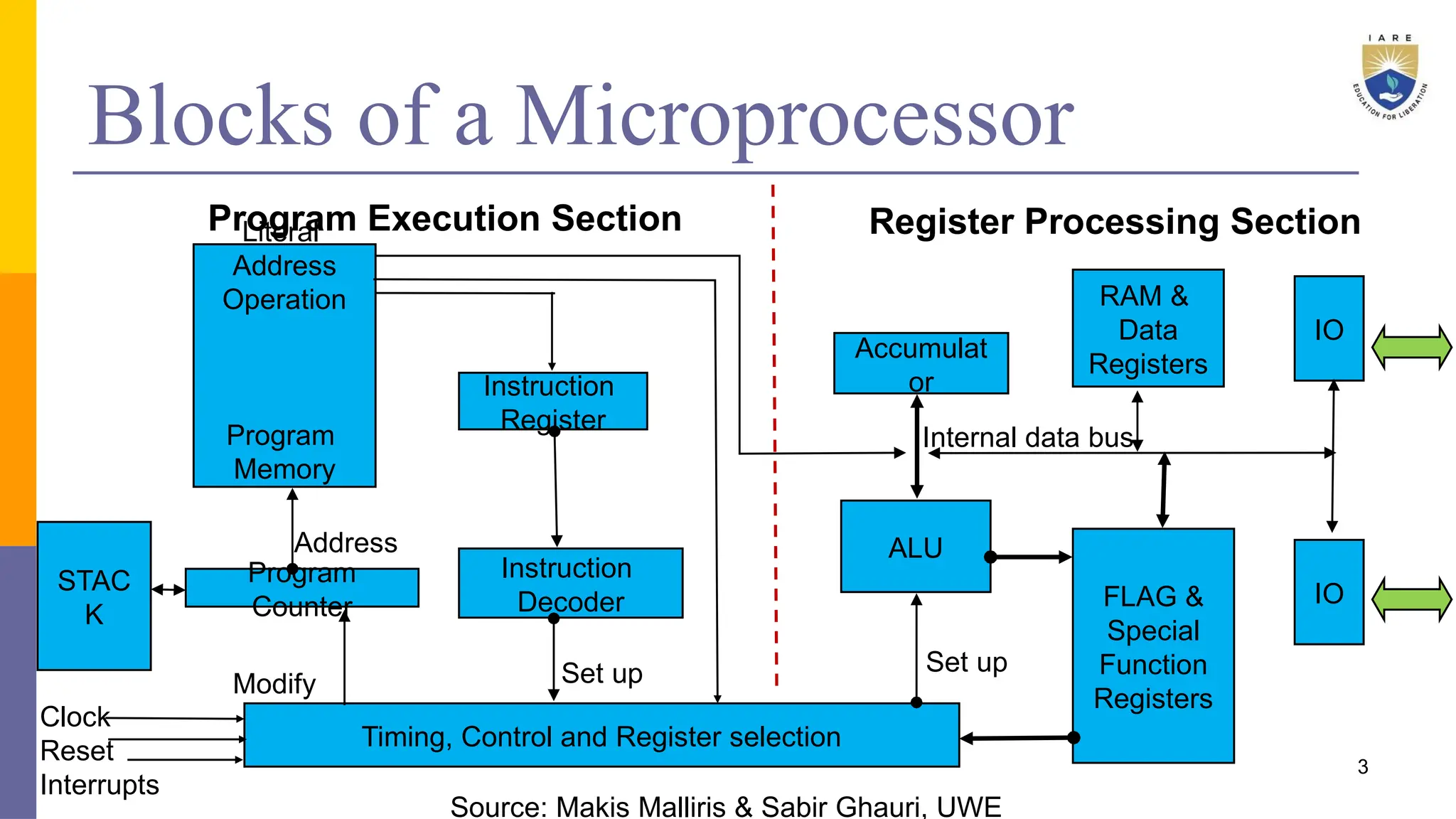

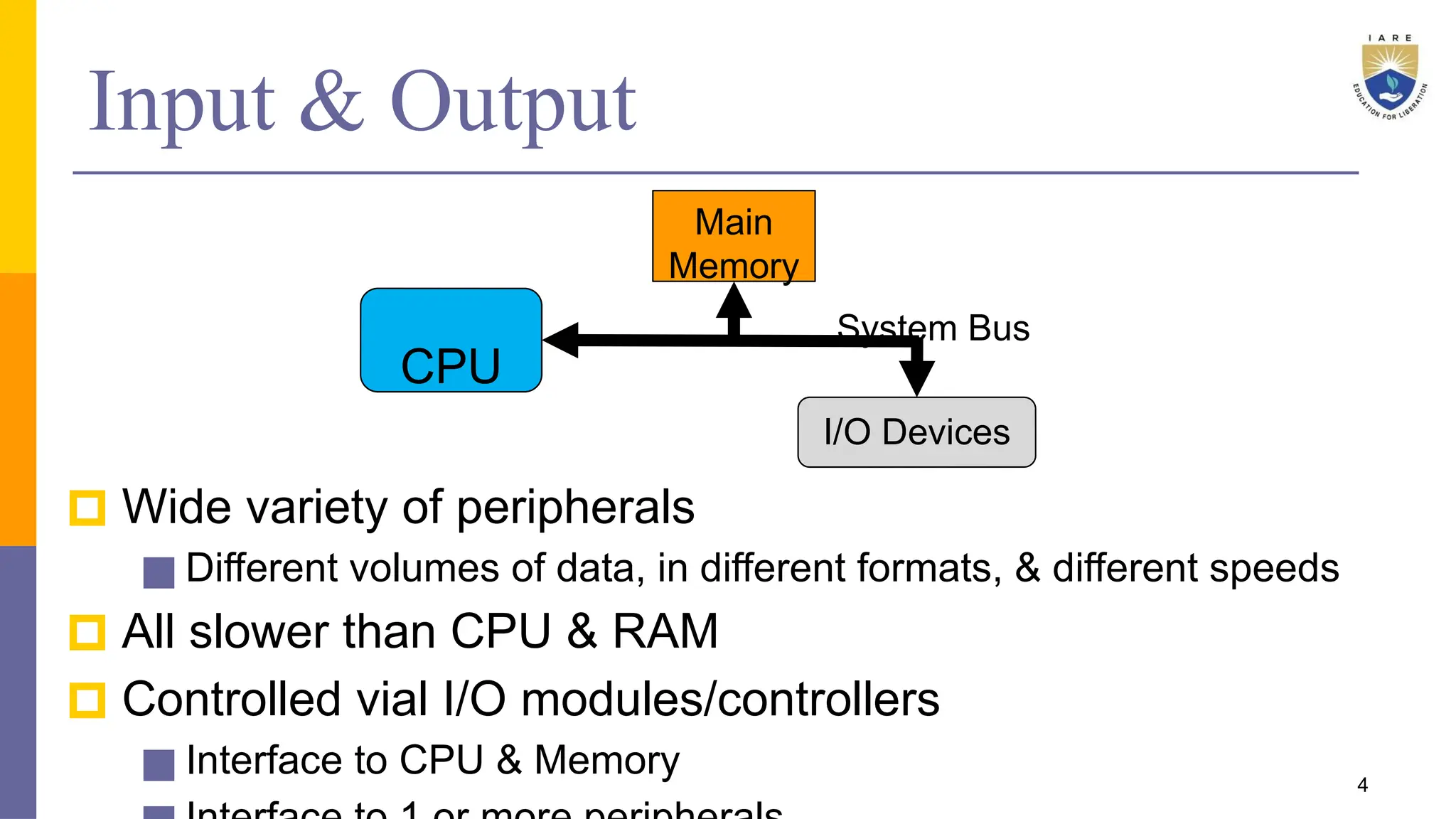

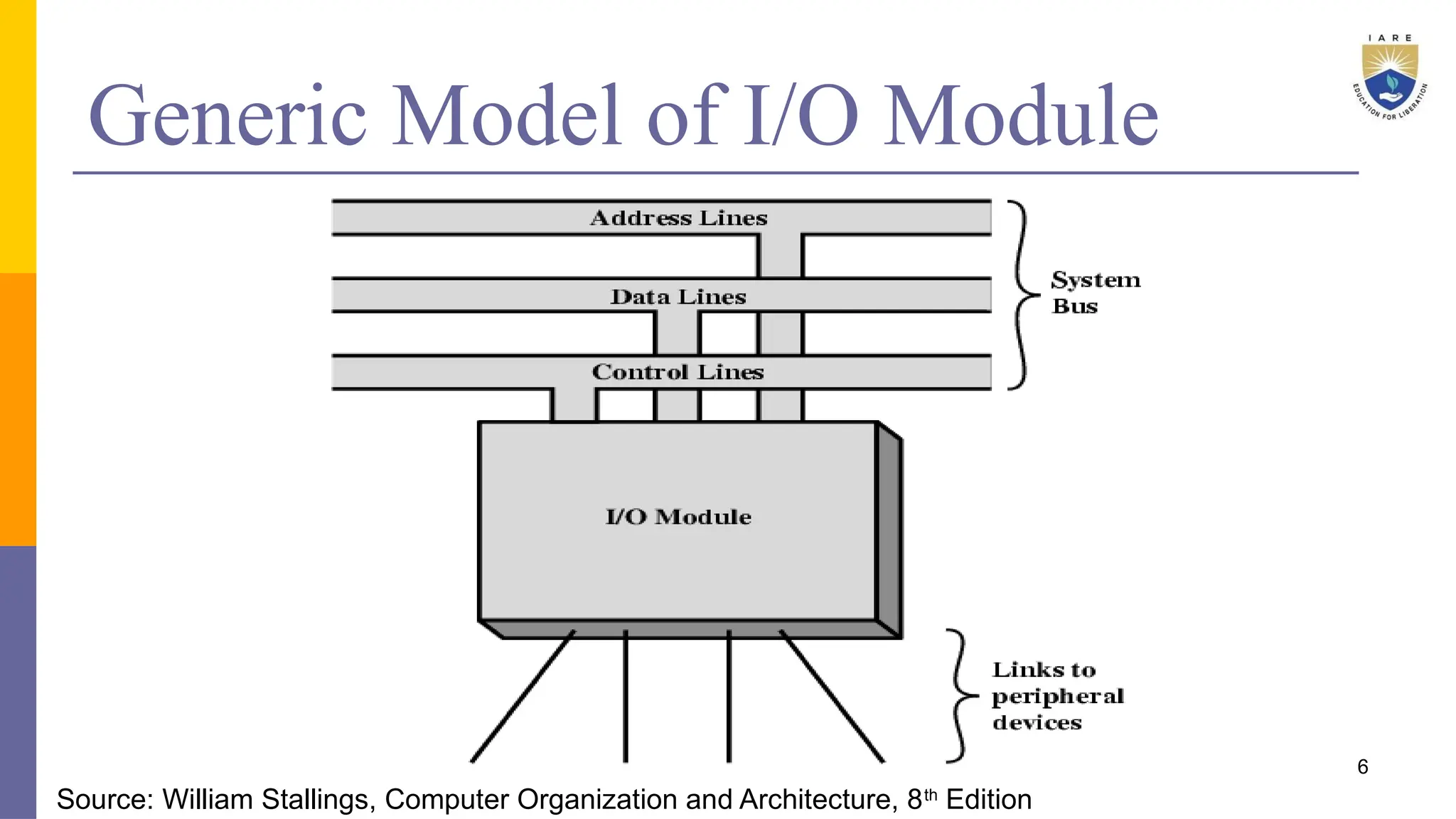

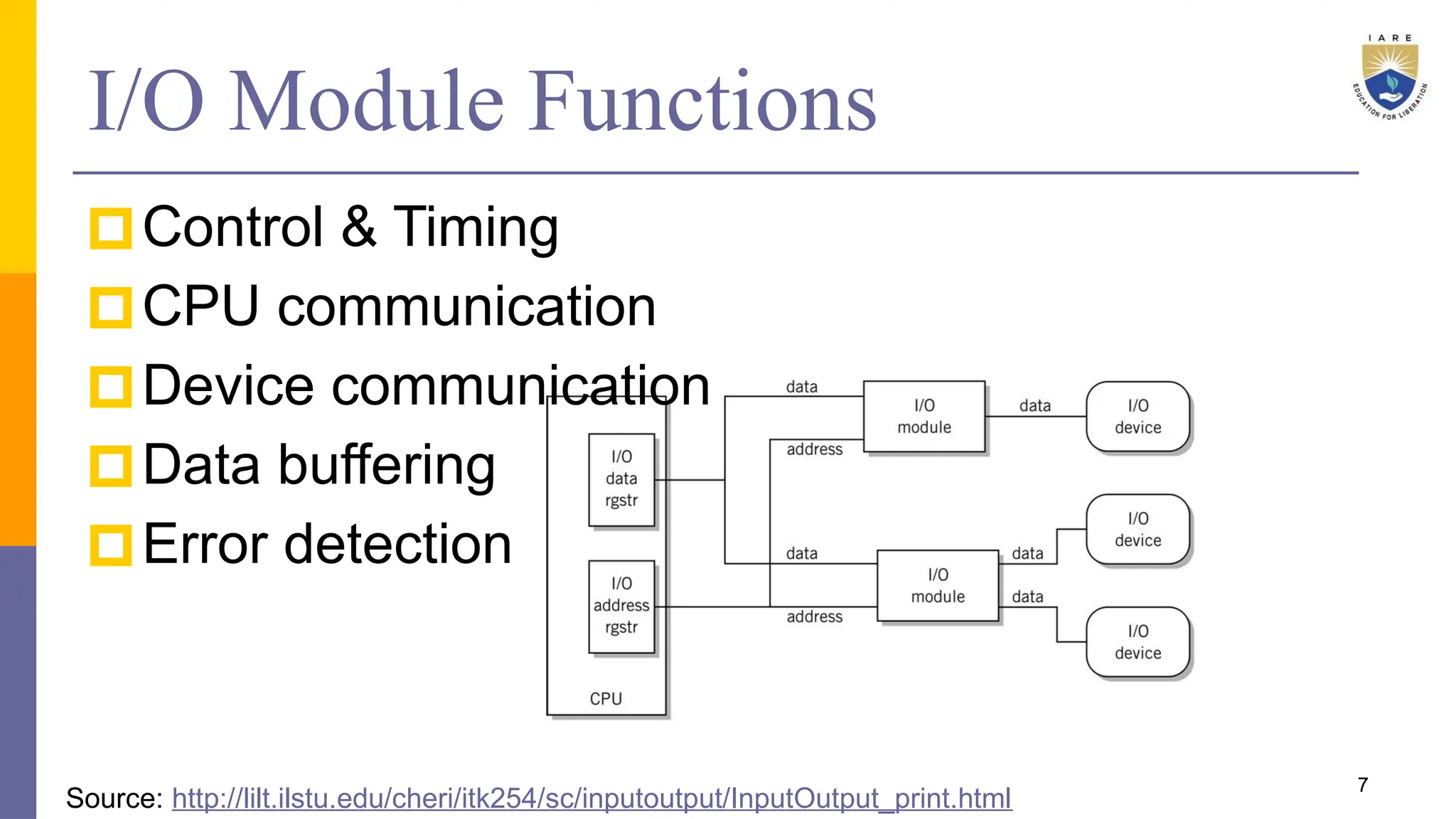

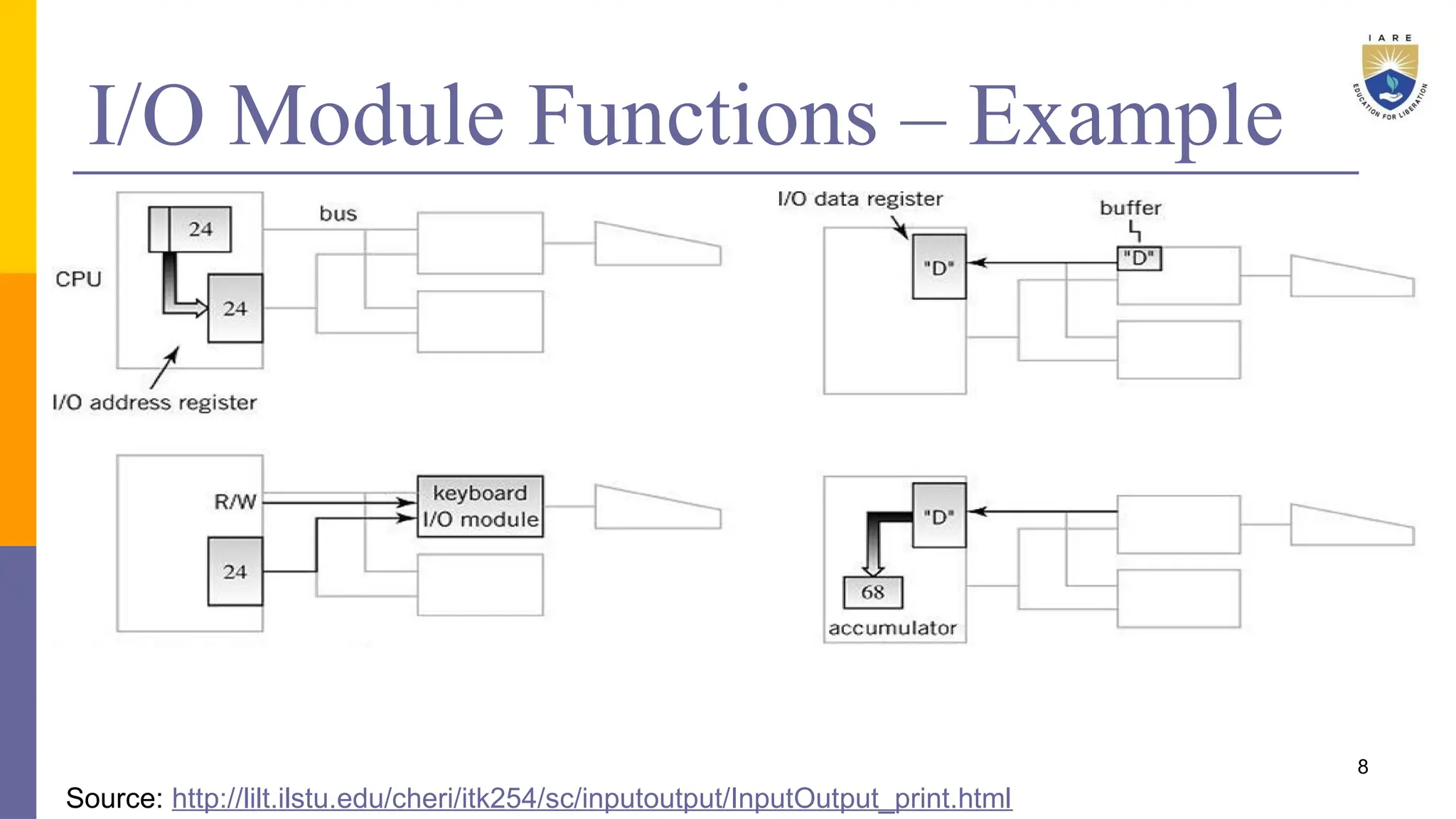

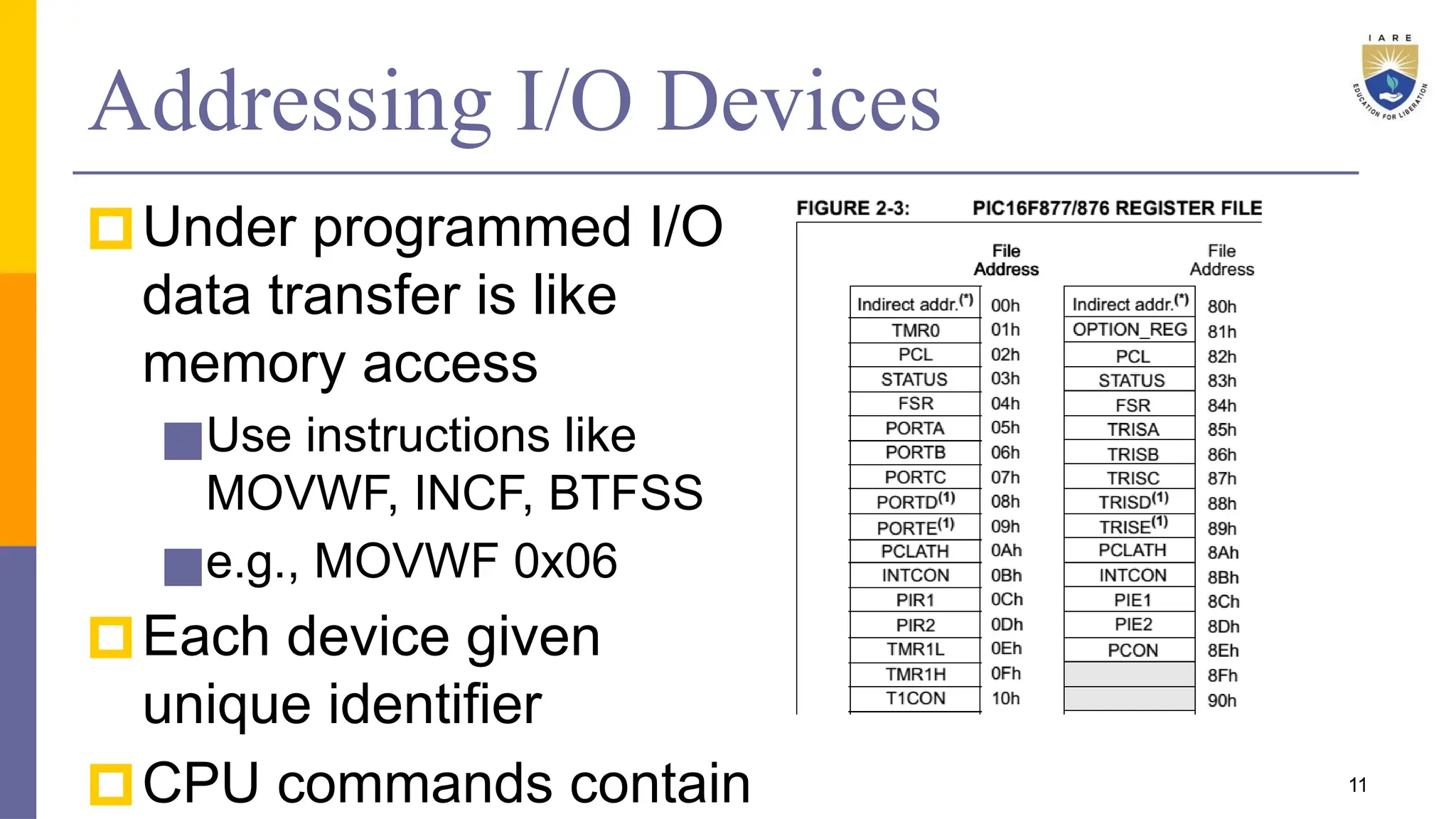

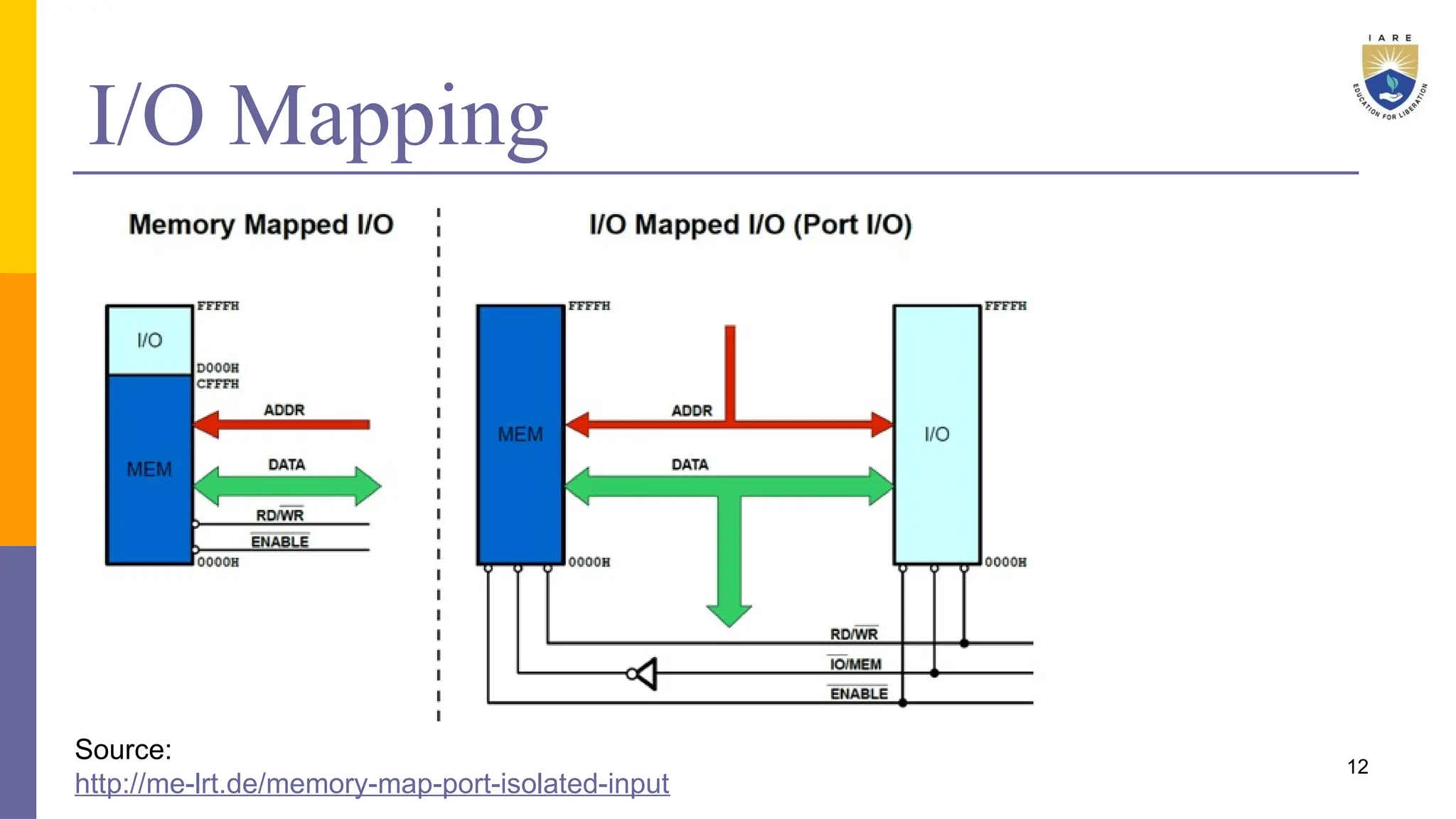

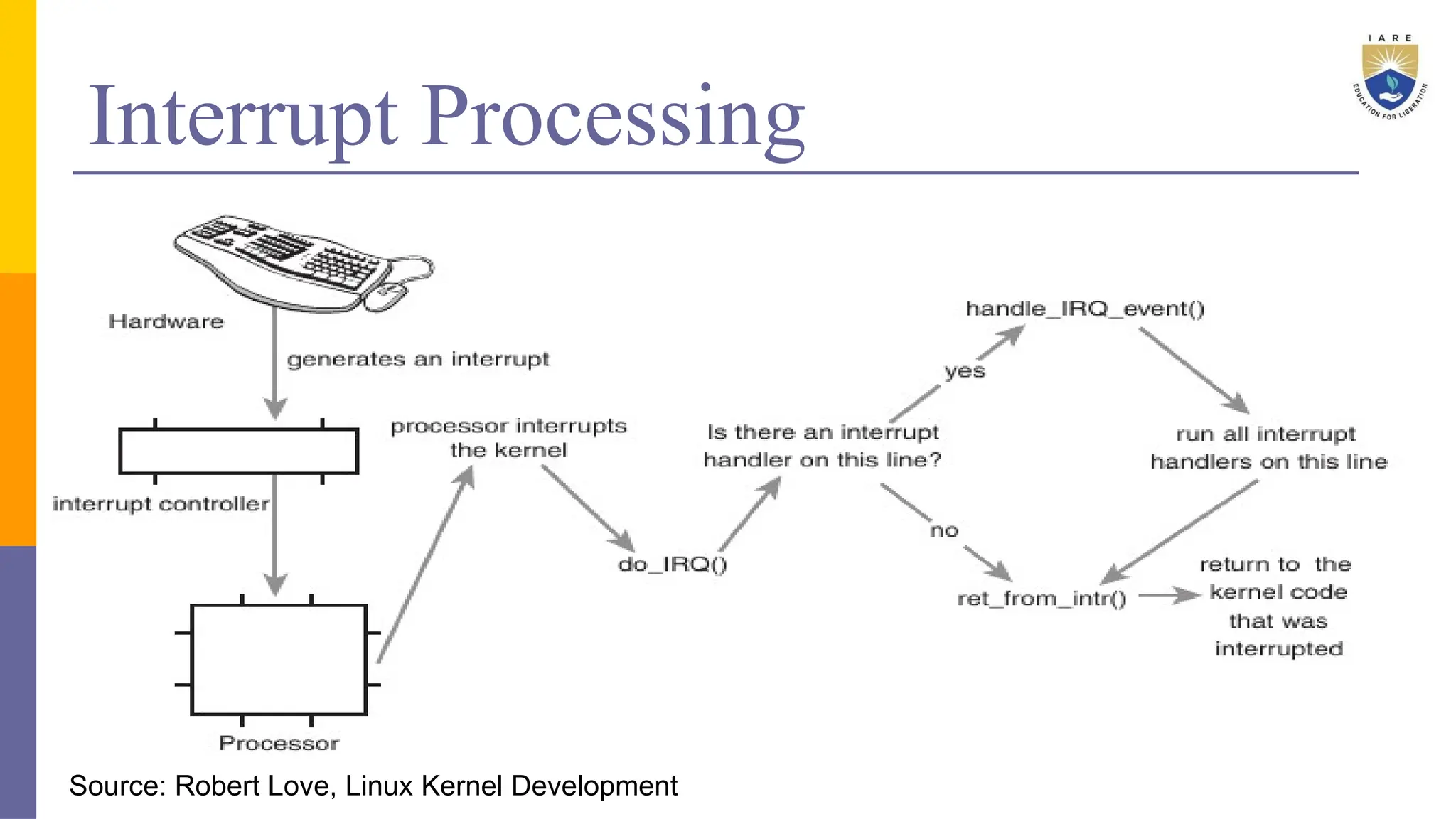

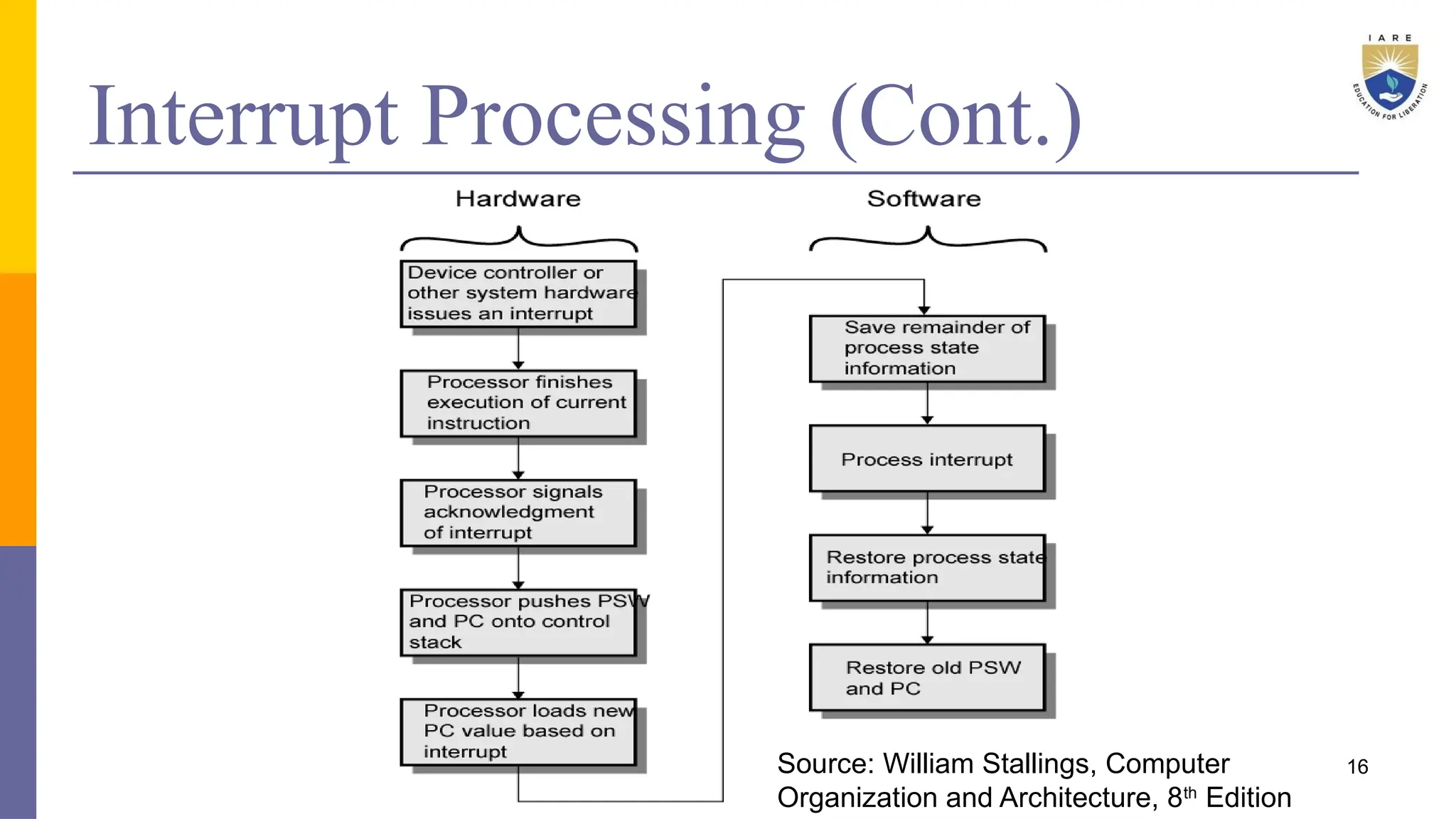

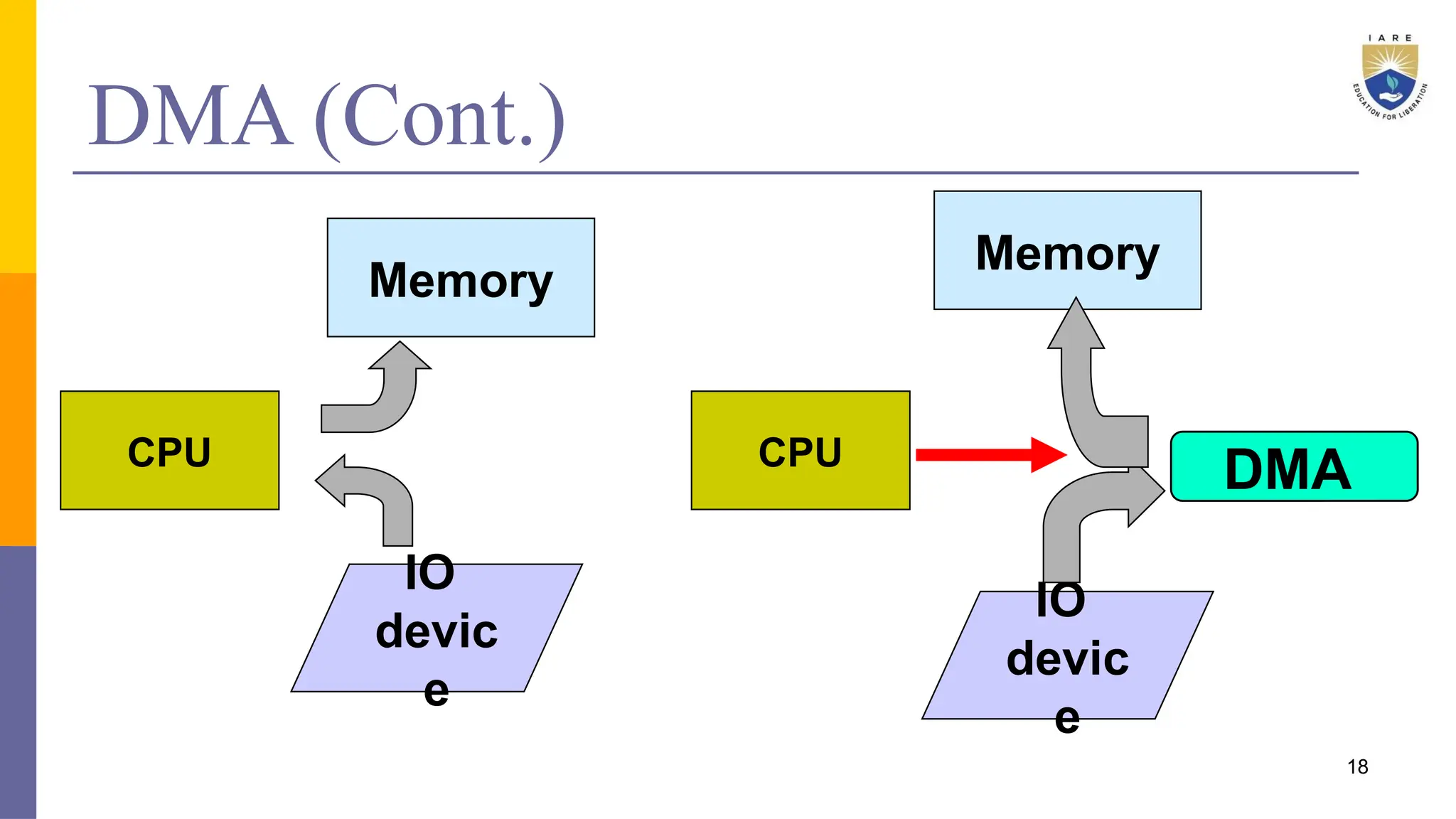

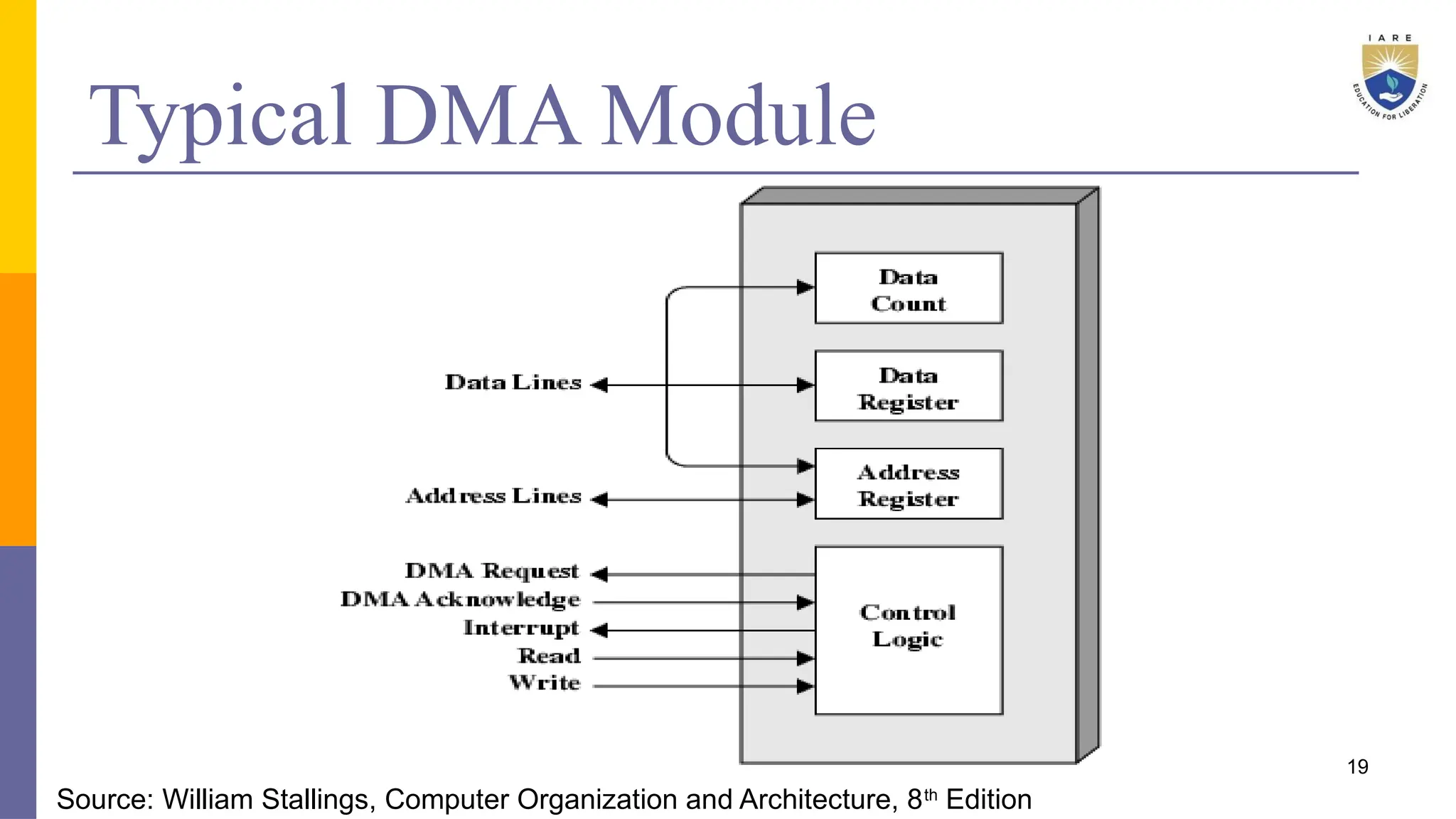

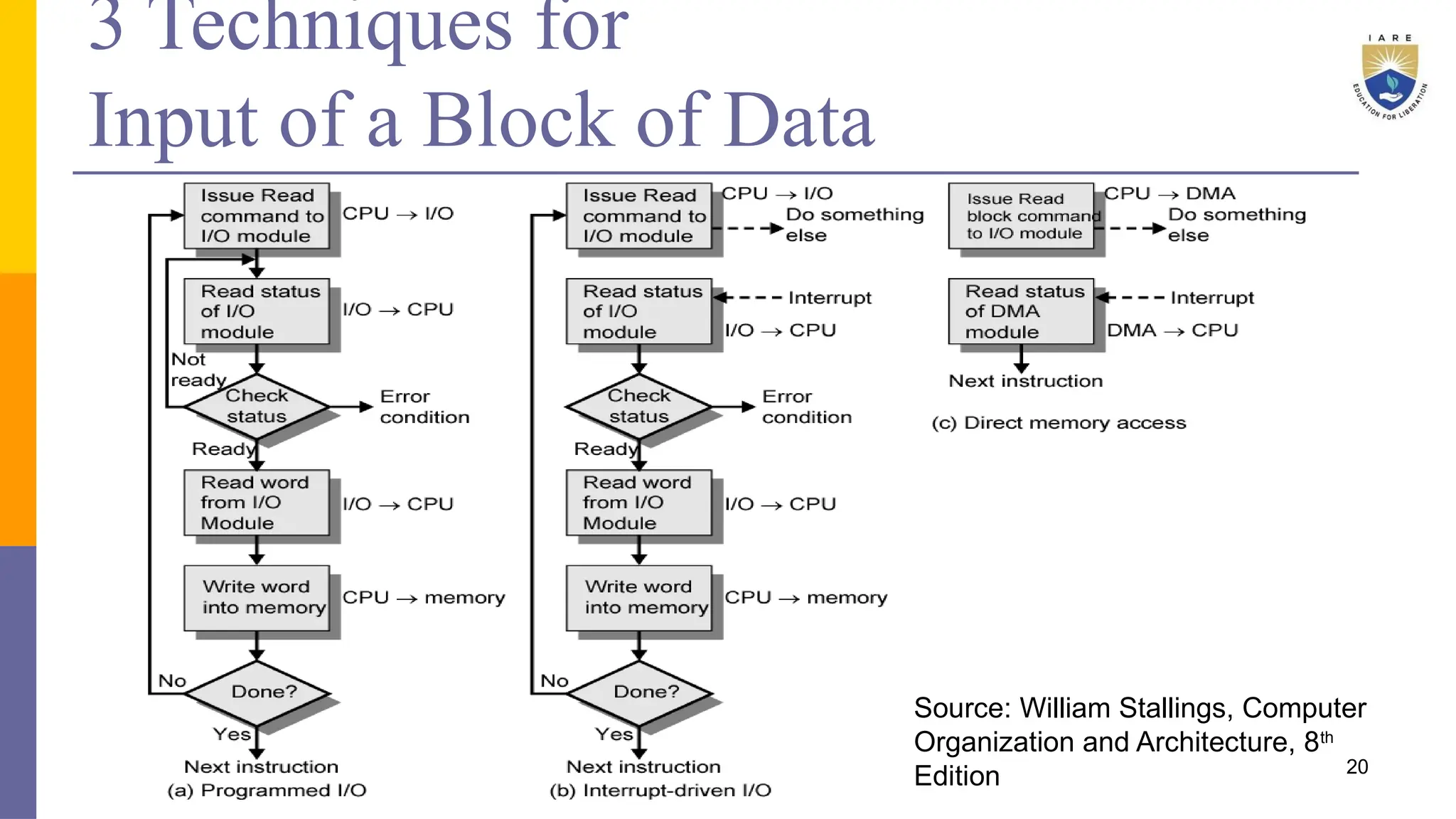

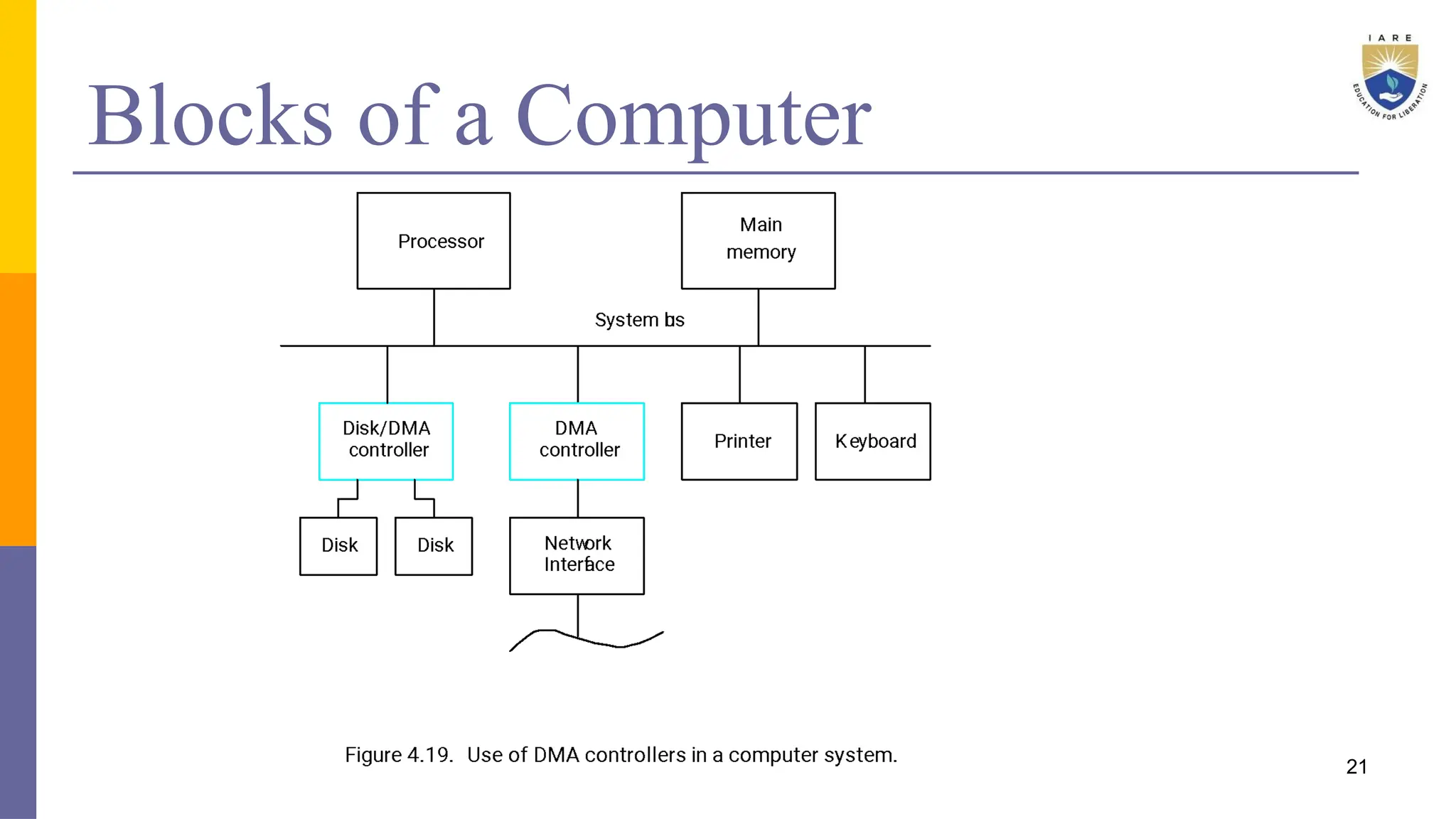

This document discusses the architecture of microprocessors and the operations related to input and output (I/O) in computer systems. It outlines various I/O techniques, including programmed I/O, interrupt-driven I/O, and direct memory access (DMA), detailing their mechanisms and implications for CPU efficiency. The document also covers I/O mapping and the roles of I/O modules in facilitating communication between the CPU and peripheral devices.