0% found this document useful (0 votes)

25 views4 pages2022 Scheme Verilog Programs

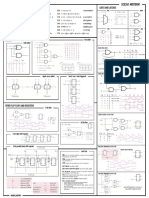

The document contains various Verilog modules for digital circuits including D flip-flops, SR flip-flops, JK flip-flops, a four-bit adder, a four-bit multiplier, a mod-N counter, and an ALU. Each module is accompanied by a testbench for simulation purposes. The code snippets illustrate the functionality and testing of these digital components in a VLSI lab setting.

Uploaded by

Geethanjali RCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

25 views4 pages2022 Scheme Verilog Programs

The document contains various Verilog modules for digital circuits including D flip-flops, SR flip-flops, JK flip-flops, a four-bit adder, a four-bit multiplier, a mod-N counter, and an ALU. Each module is accompanied by a testbench for simulation purposes. The code snippets illustrate the functionality and testing of these digital components in a VLSI lab setting.

Uploaded by

Geethanjali RCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 4