0% found this document useful (0 votes)

8 views17 pagesCoa (Module 2)

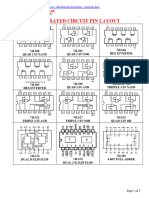

The document discusses sequential circuits, highlighting their dependence on both current inputs and previous outputs, and differentiates them from combinational circuits. It covers various types of triggering mechanisms, including level and edge triggering, and explains the functioning of latches and different flip-flops such as SR, JK, D, and T flip-flops. The document also provides truth tables and circuit diagrams for better understanding of these concepts.

Uploaded by

jasifjabir296Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

8 views17 pagesCoa (Module 2)

The document discusses sequential circuits, highlighting their dependence on both current inputs and previous outputs, and differentiates them from combinational circuits. It covers various types of triggering mechanisms, including level and edge triggering, and explains the functioning of latches and different flip-flops such as SR, JK, D, and T flip-flops. The document also provides truth tables and circuit diagrams for better understanding of these concepts.

Uploaded by

jasifjabir296Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 17