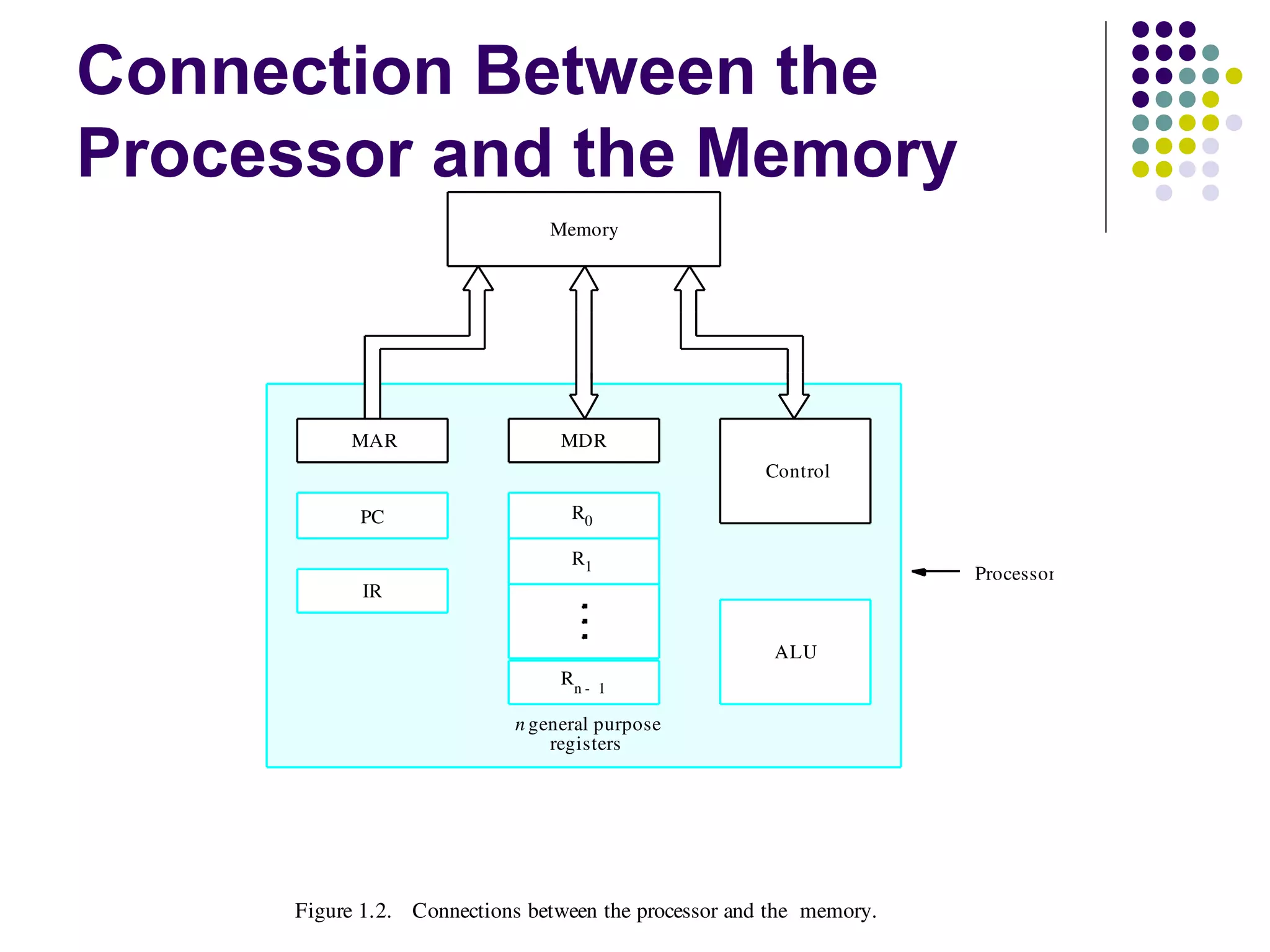

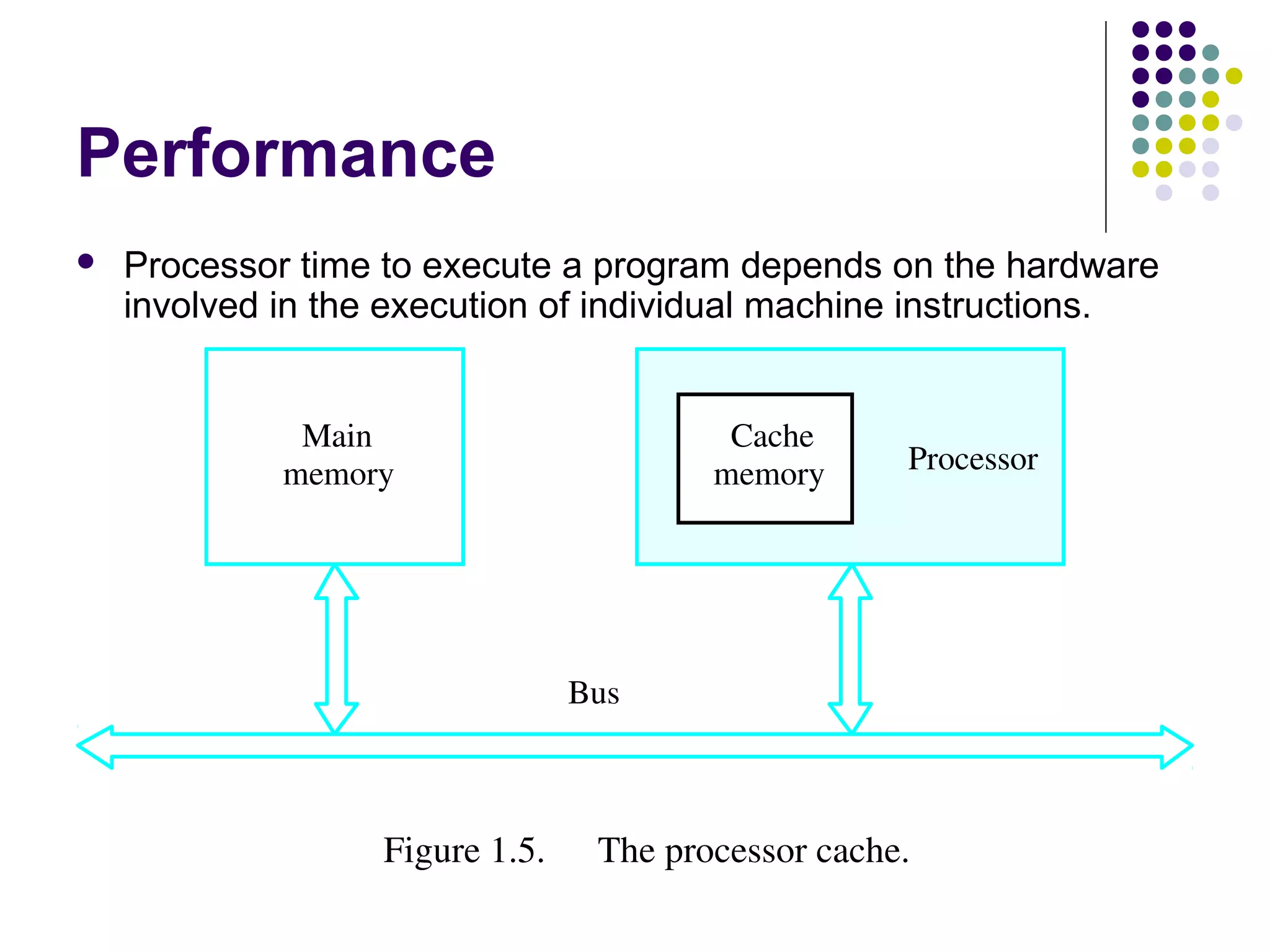

This document provides an overview of the basic functional units and operations of a computer system. It discusses how instructions and data are stored and processed using components like the CPU, memory, arithmetic logic unit, and control unit. The document also covers concepts like pipelining and parallel processing that can improve performance, as well as differences between RISC and CISC instruction sets. It aims to explain at a high level how a computer works from an architectural perspective.

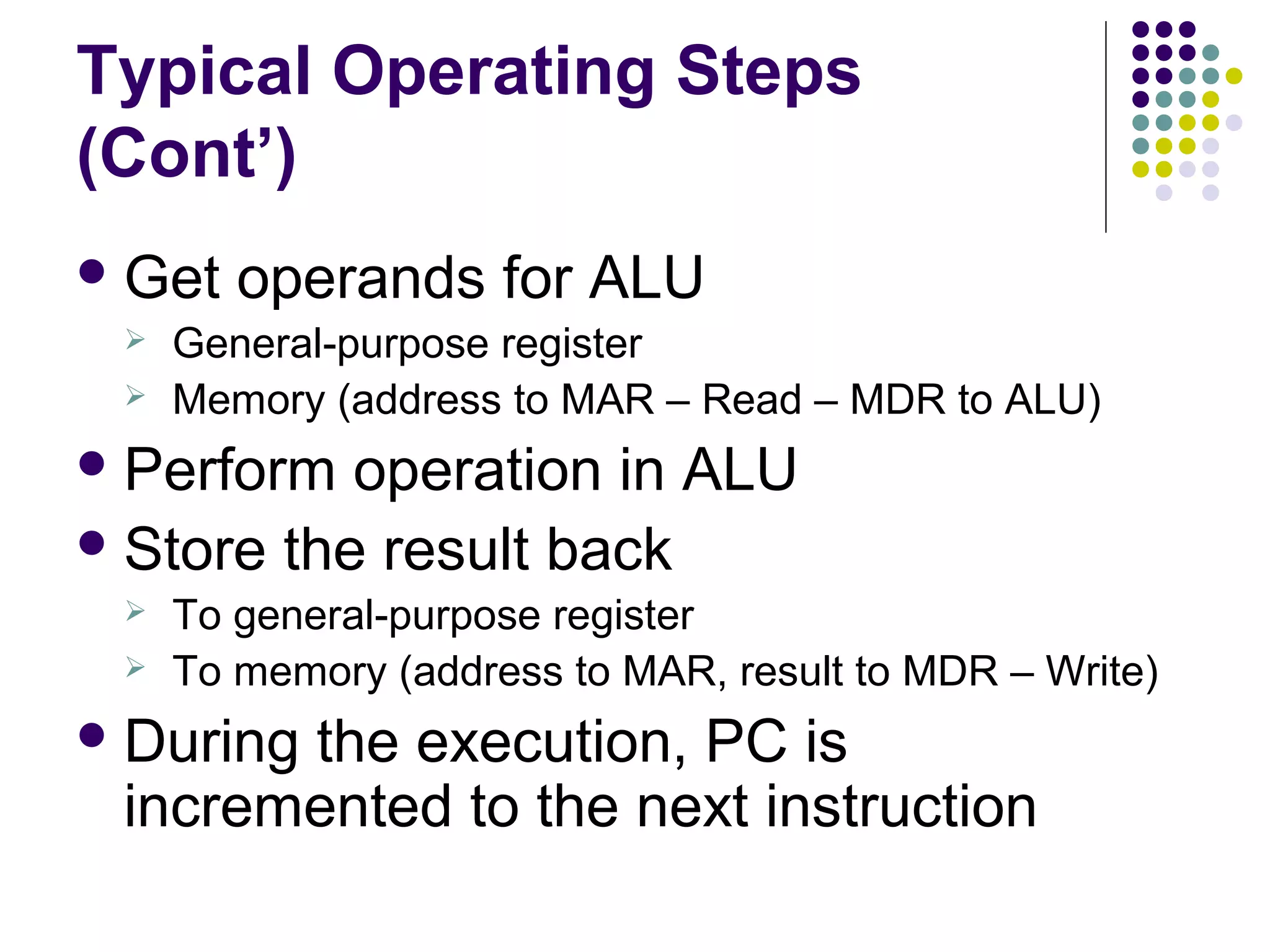

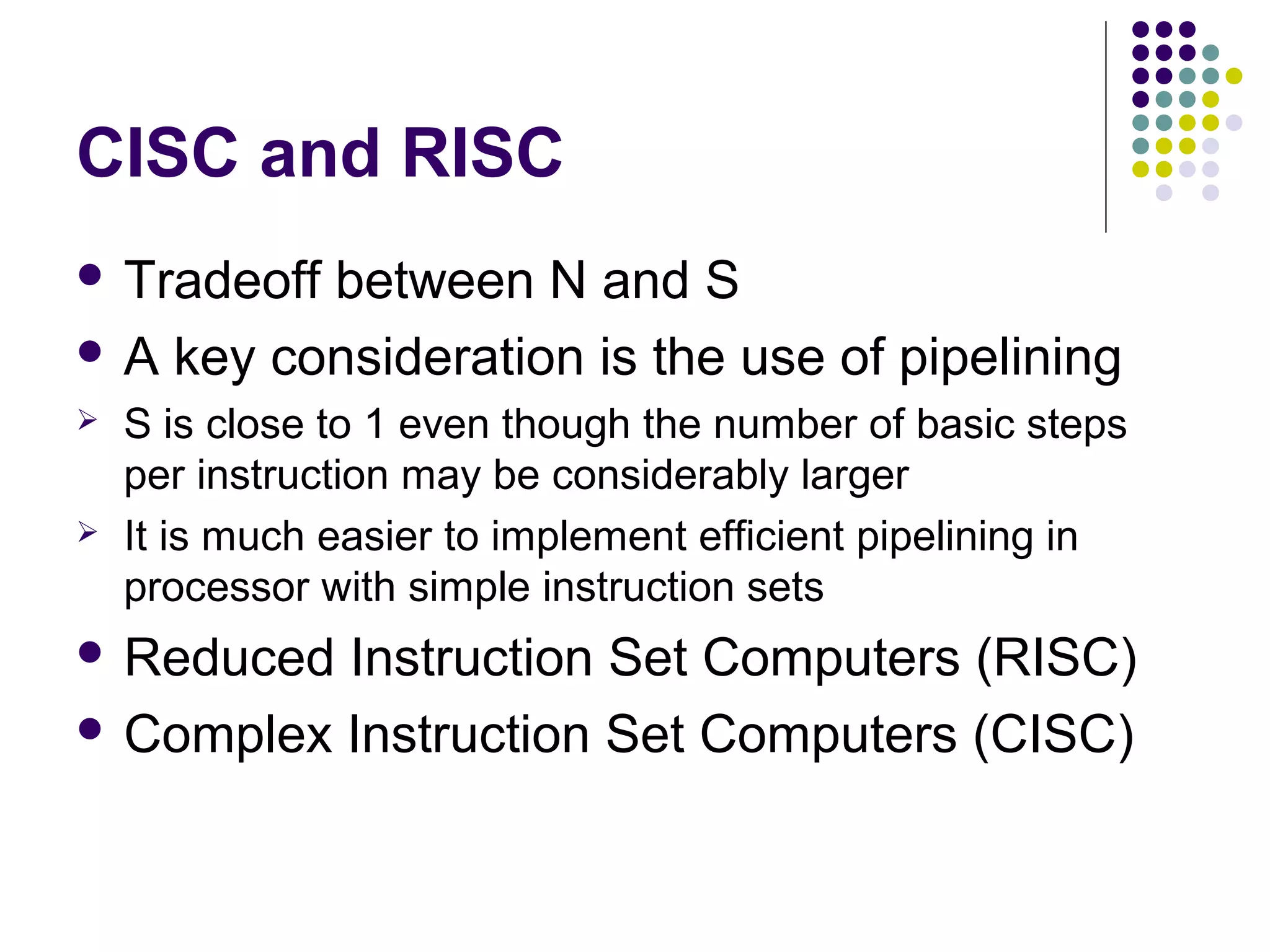

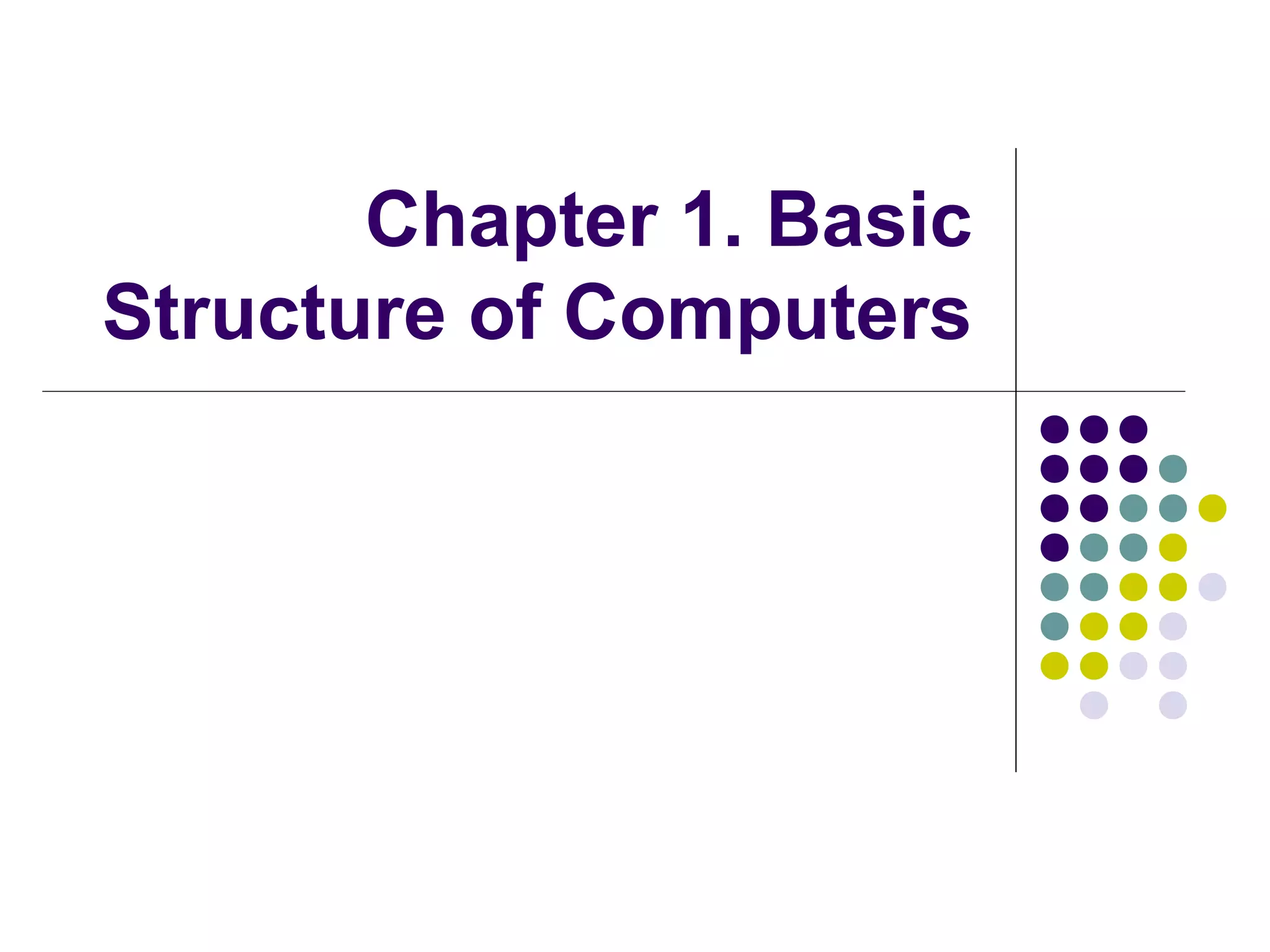

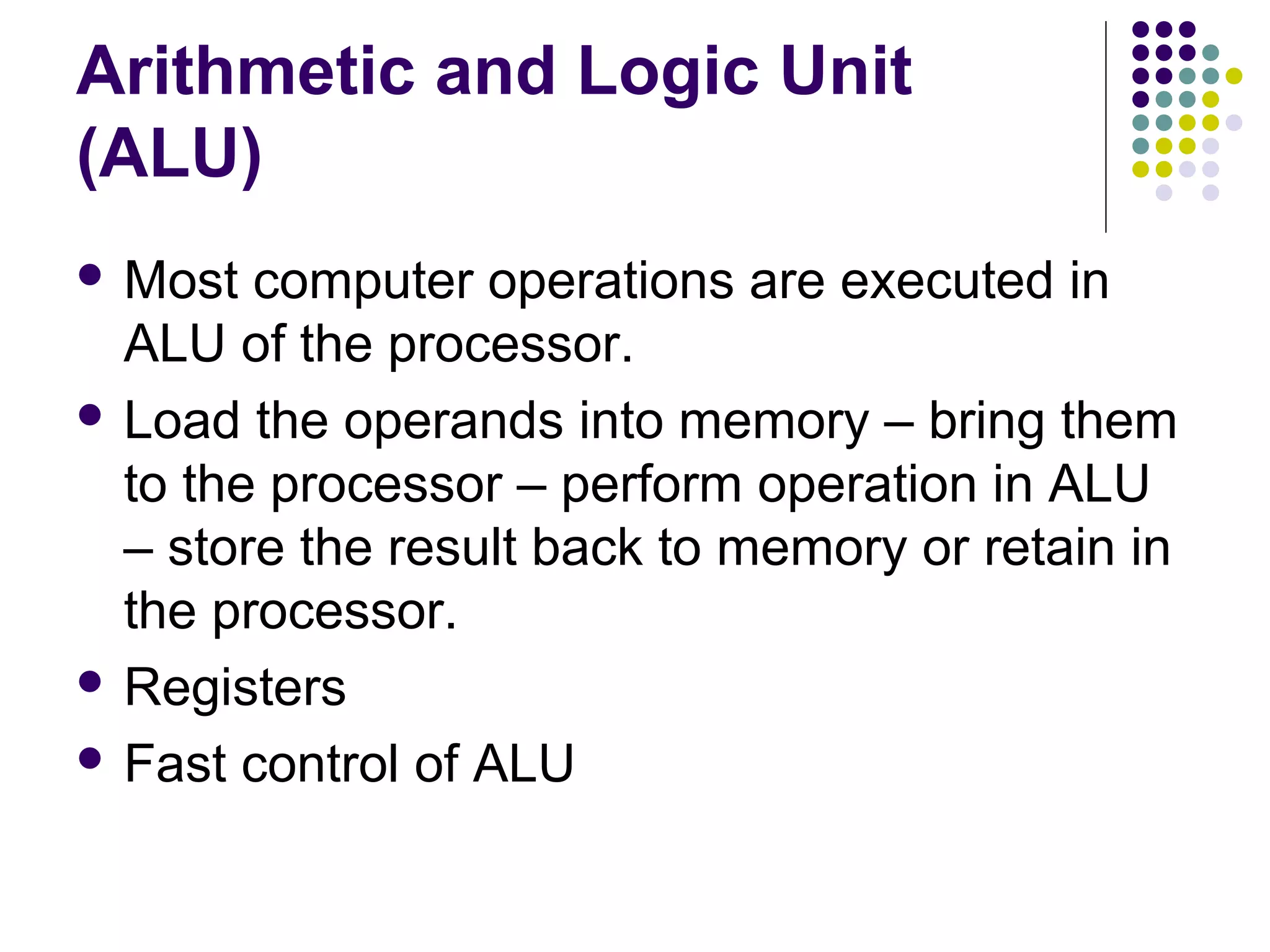

![Five Execution Steps

Step name Action for R-type Action for Memory- Action for Action for

instructions reference Instructions branches jumps

Instruction fetch IR = MEM[PC]

PC = PC + 4

Instruction decode/ register A = Reg[IR[25-21]]

fetch B = Reg[IR[20-16]]

ALUOut = PC + (sign extend (IR[15-0])<<2)

Execution, address ALUOut = A op B ALUOut = A+sign IF(A==B) Then PC=PC[31-

computation, branch/jump extend(IR[15-0]) PC=ALUOut 28]||(IR[25-

completion 0]<<2)

Memory access or R-type Reg[IR[15-11]] = Load:MDR =Mem[ALUOut]

completion ALUOut or

Store:Mem[ALUOut] = B

Memory read completion Load: Reg[IR[20-16]] =

MDR](https://image.slidesharecdn.com/chapter1-basicstructureofcomputers-120919065217-phpapp01/75/basic-structure-of-computers-9-2048.jpg)