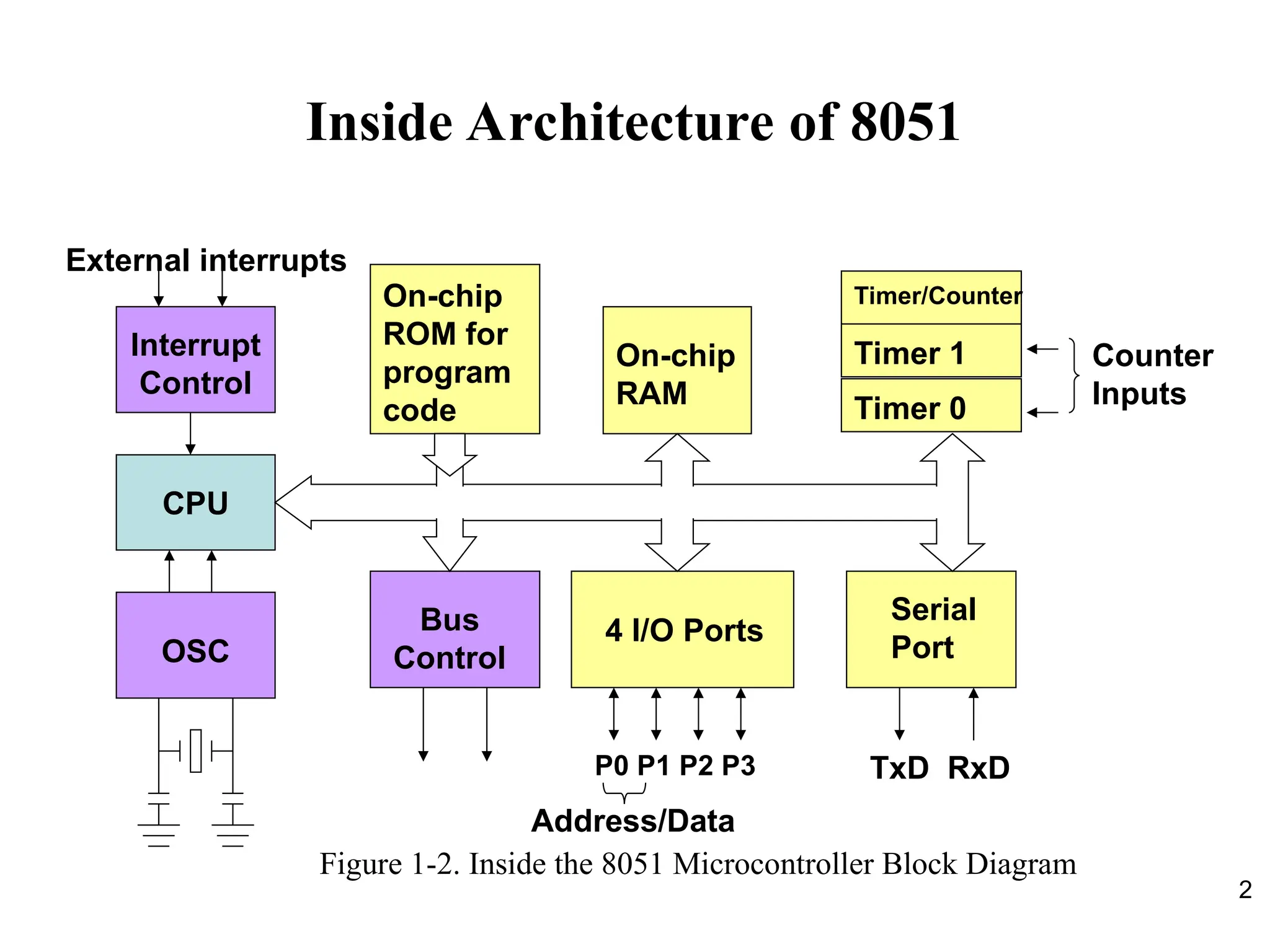

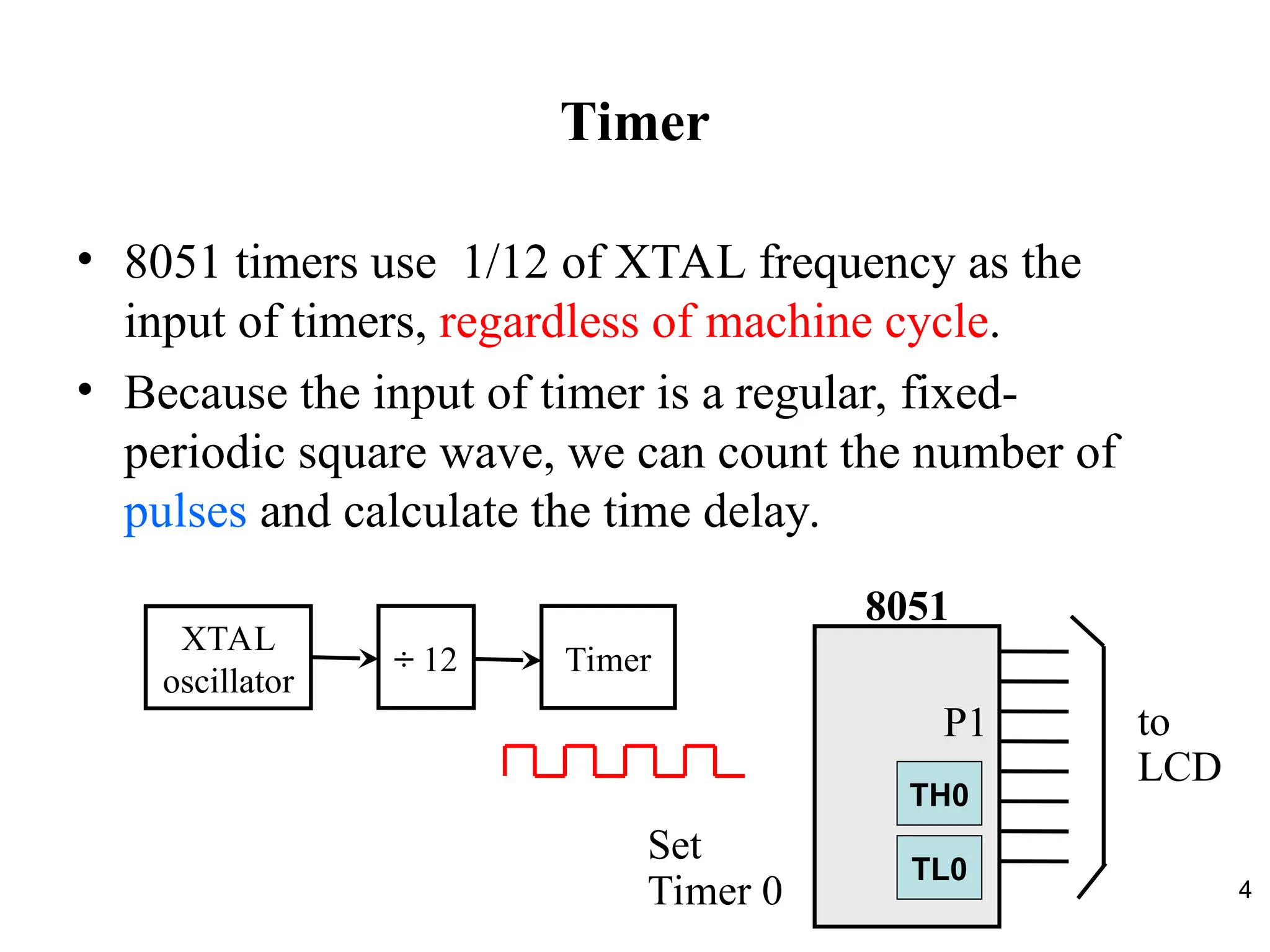

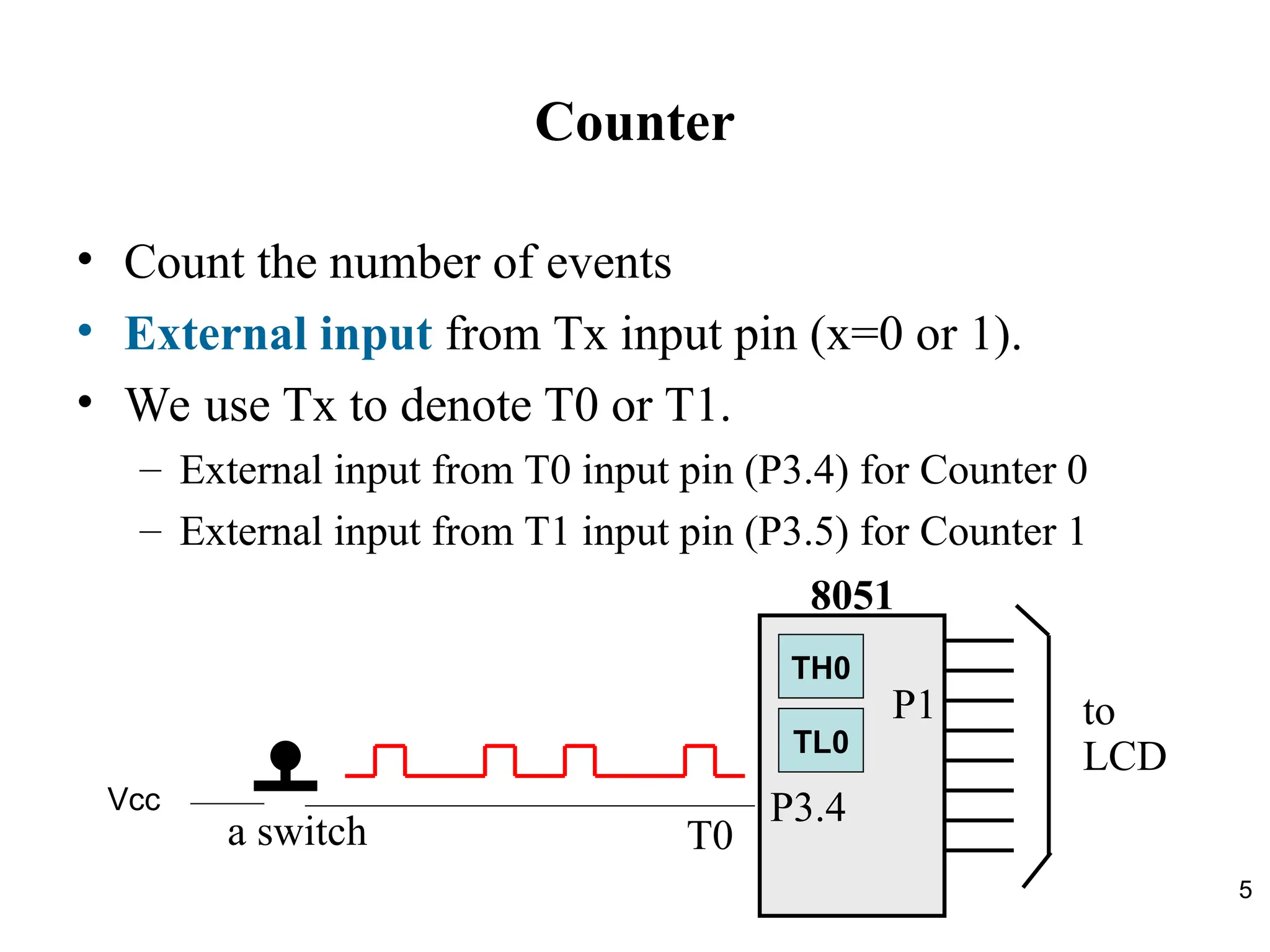

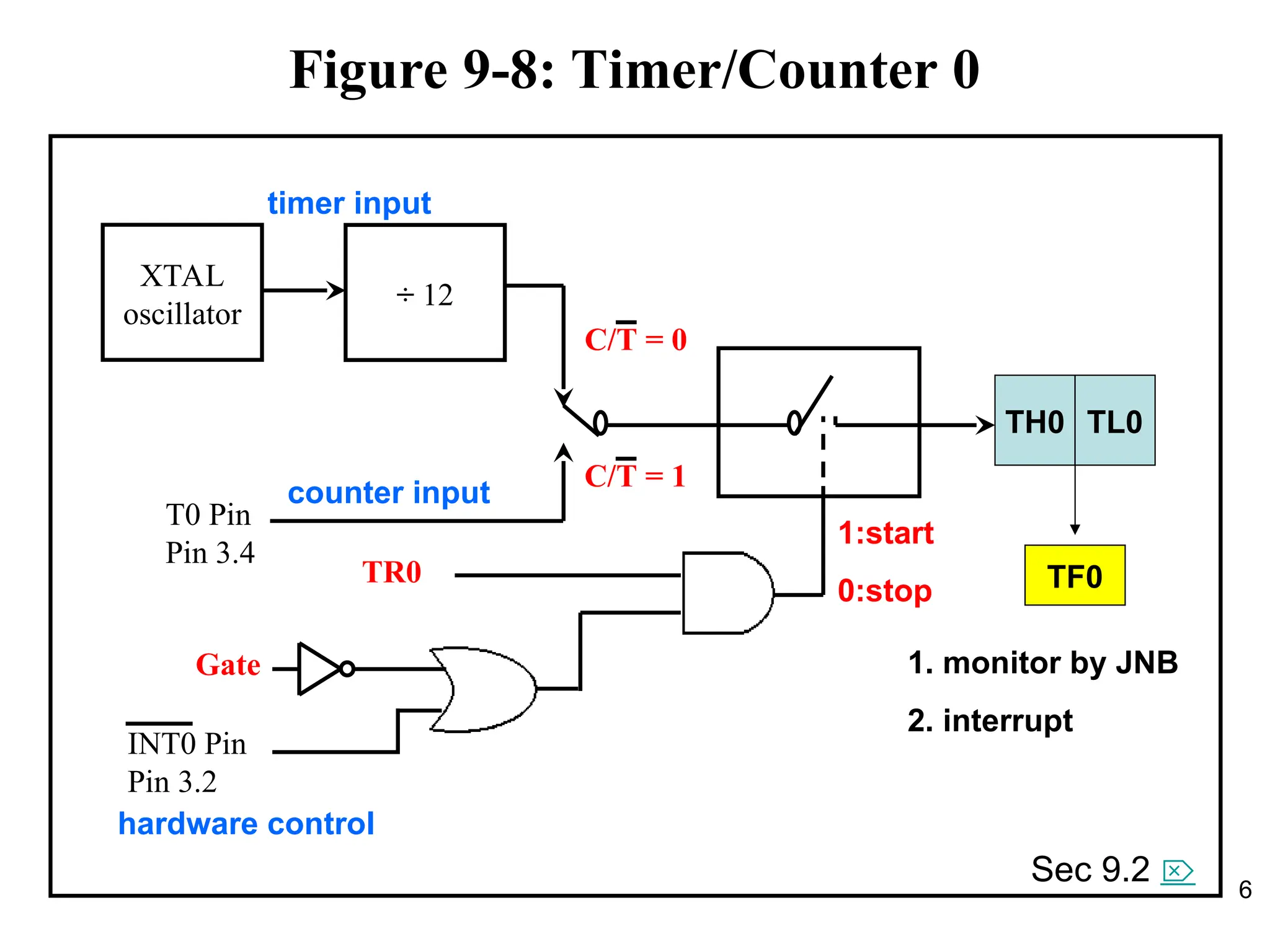

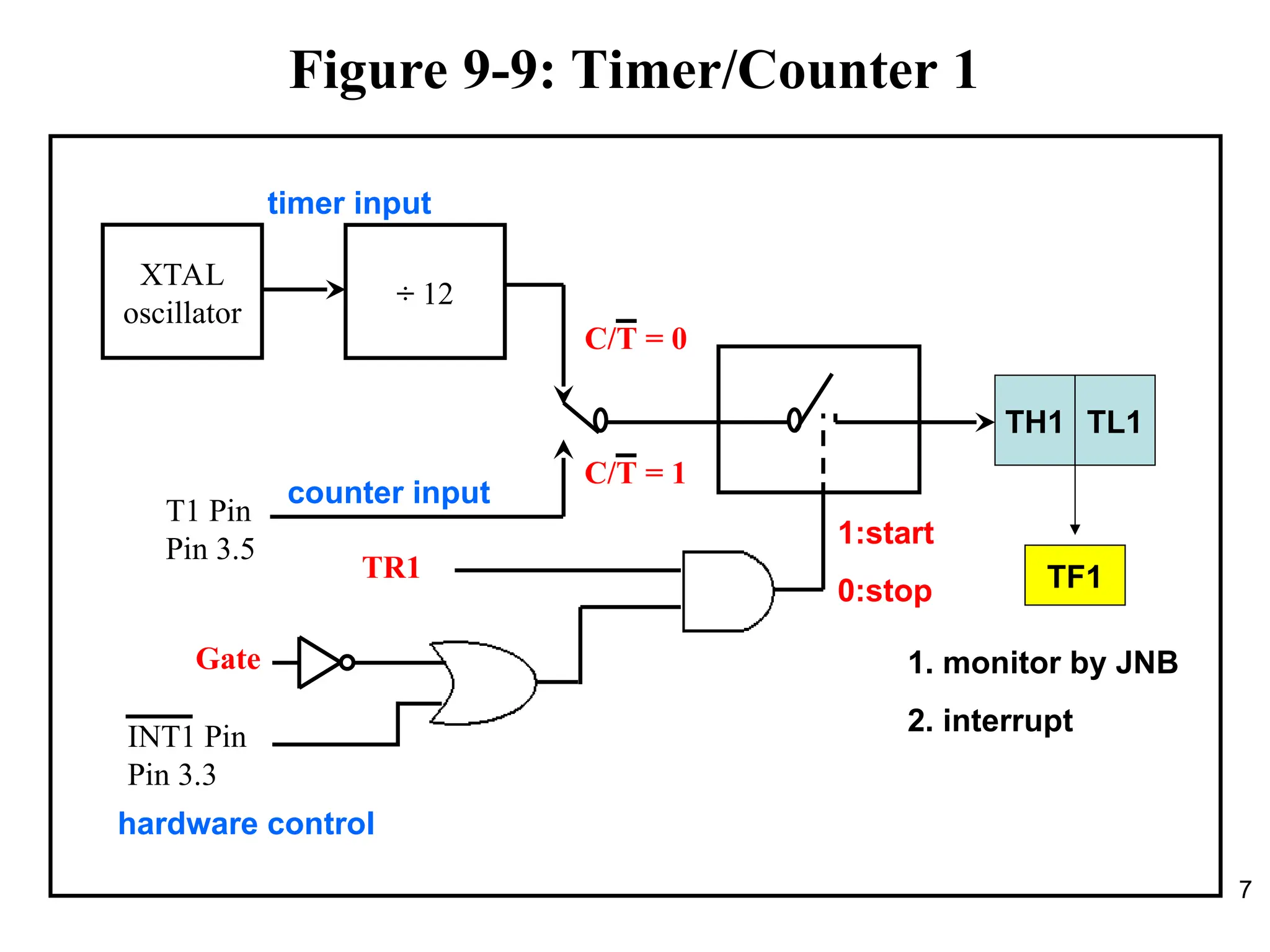

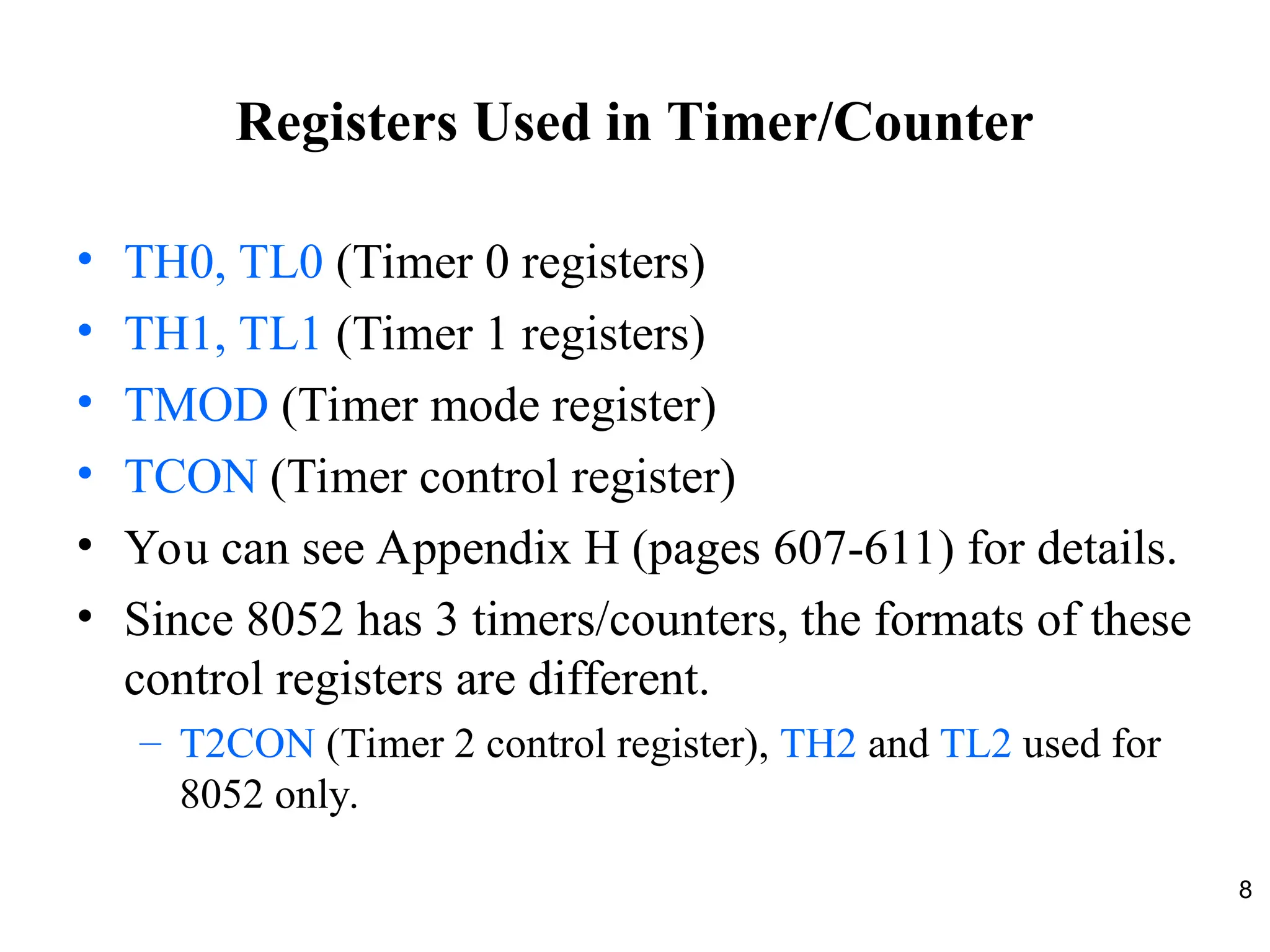

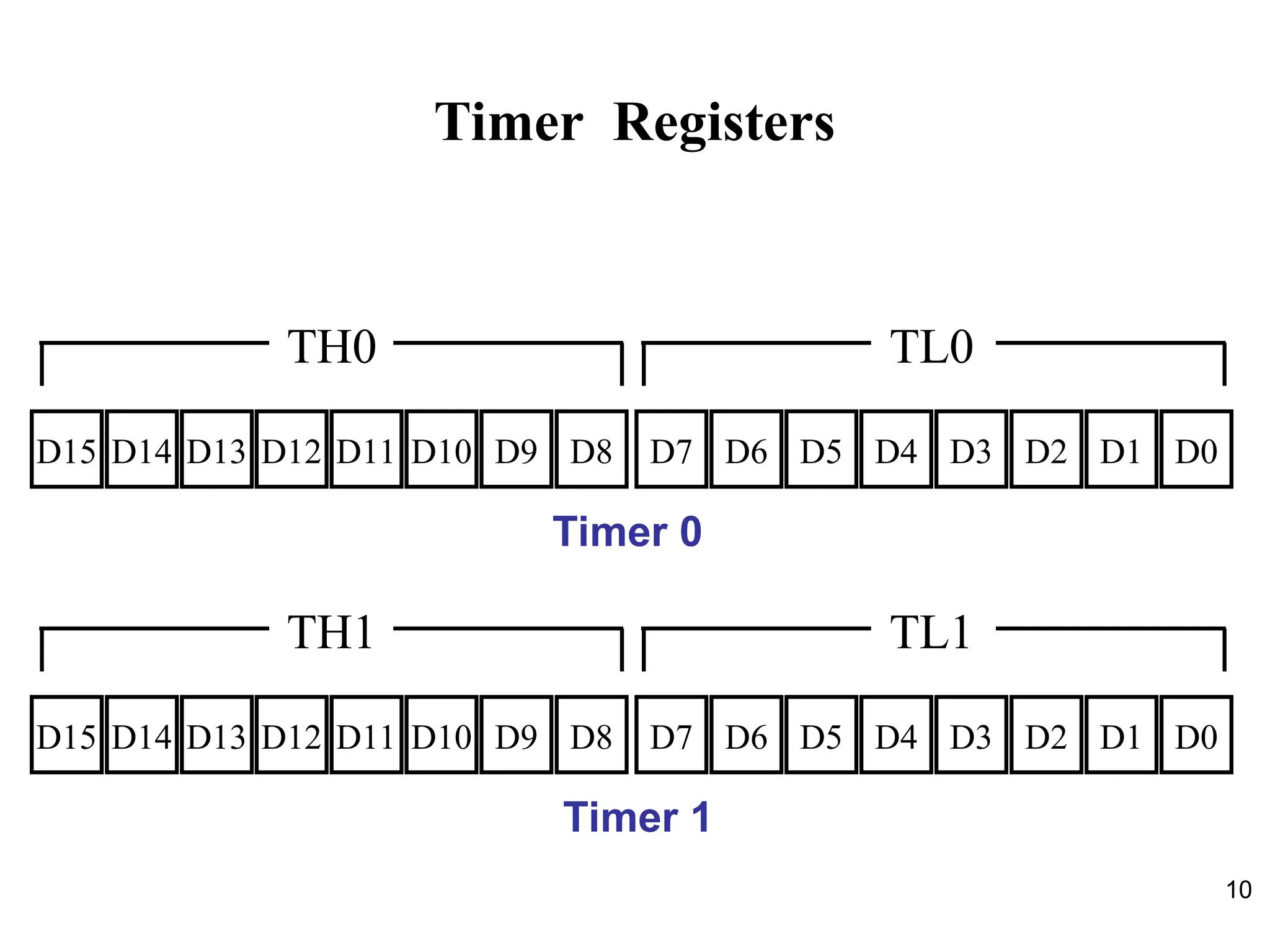

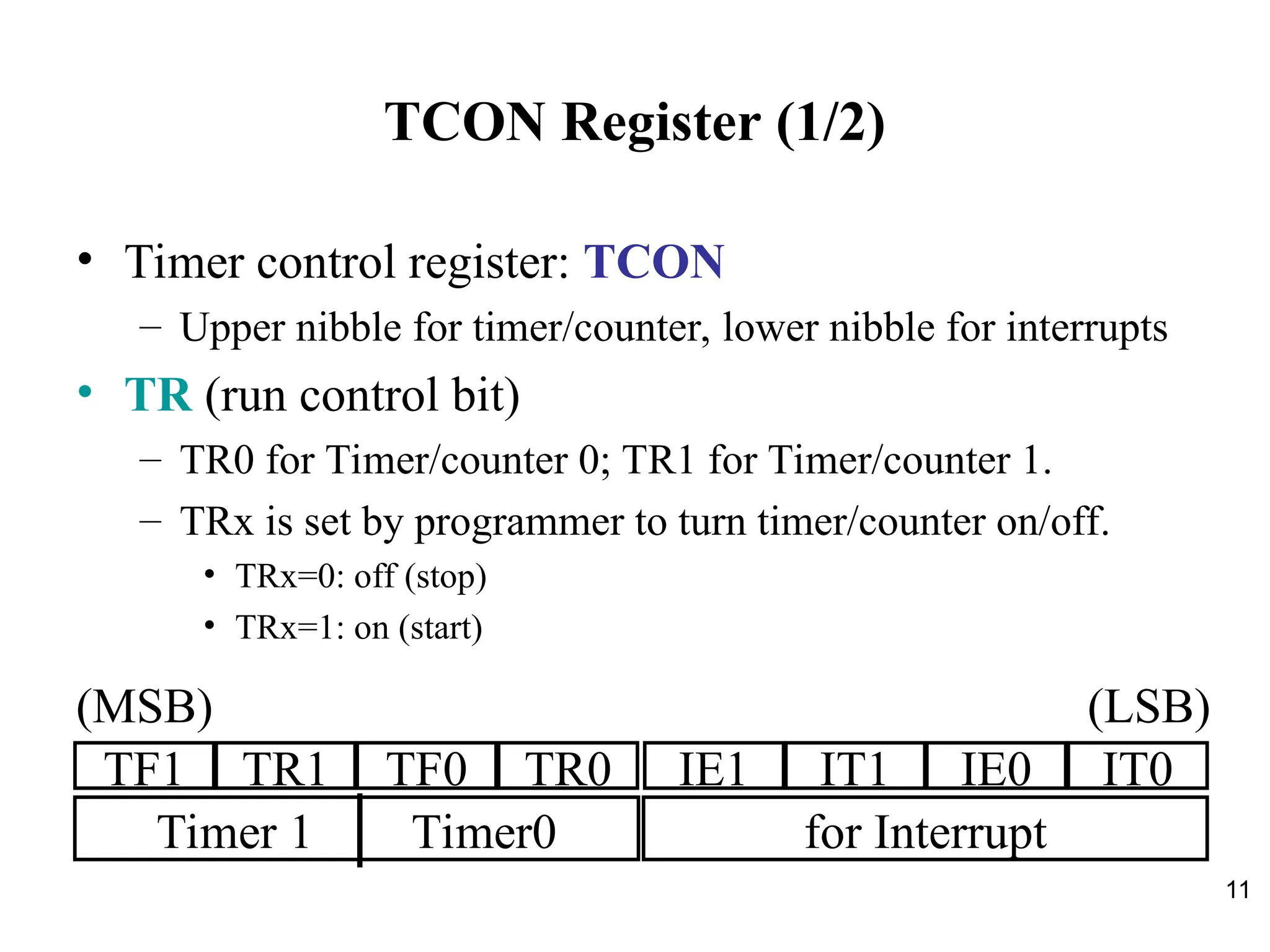

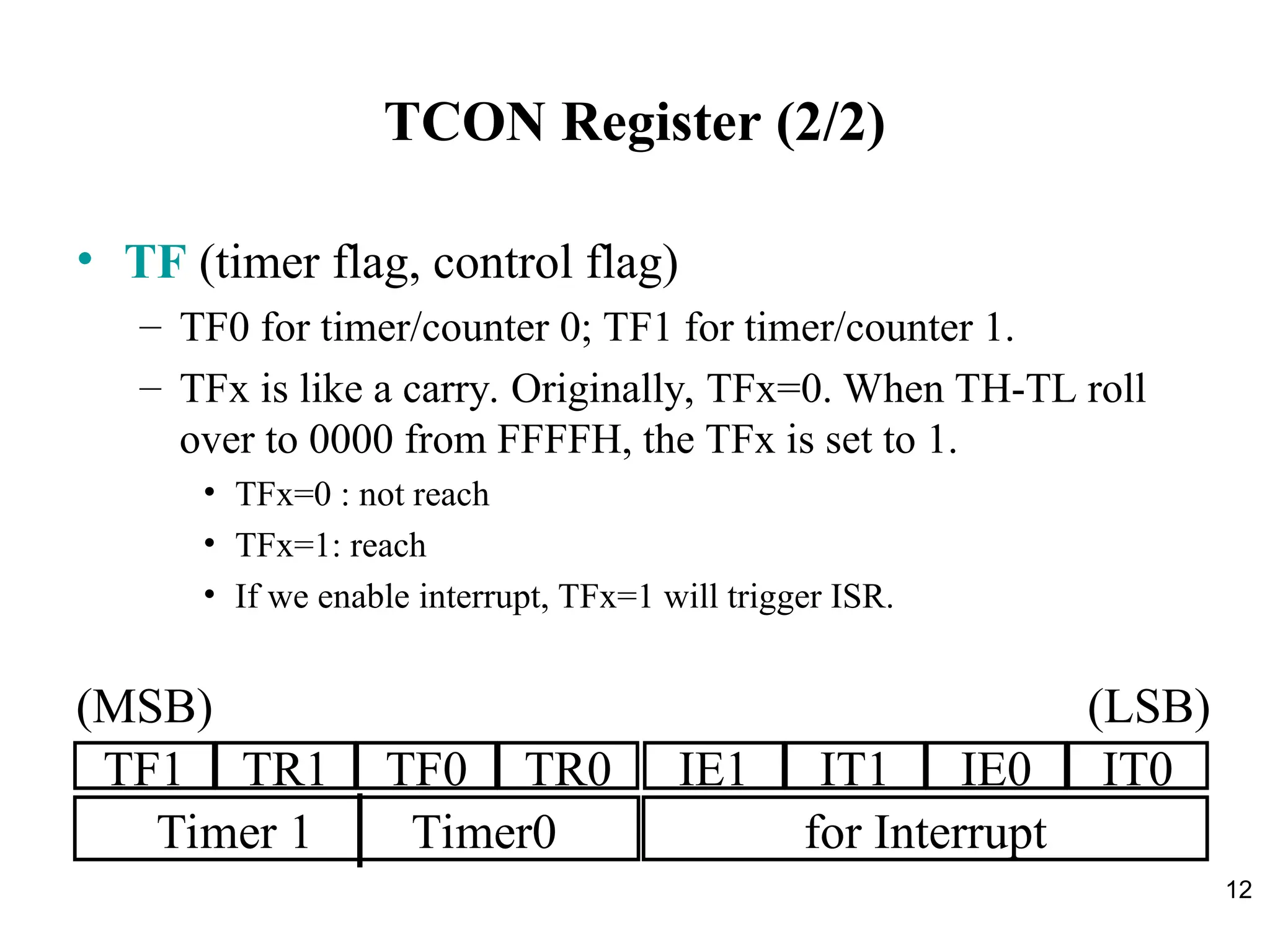

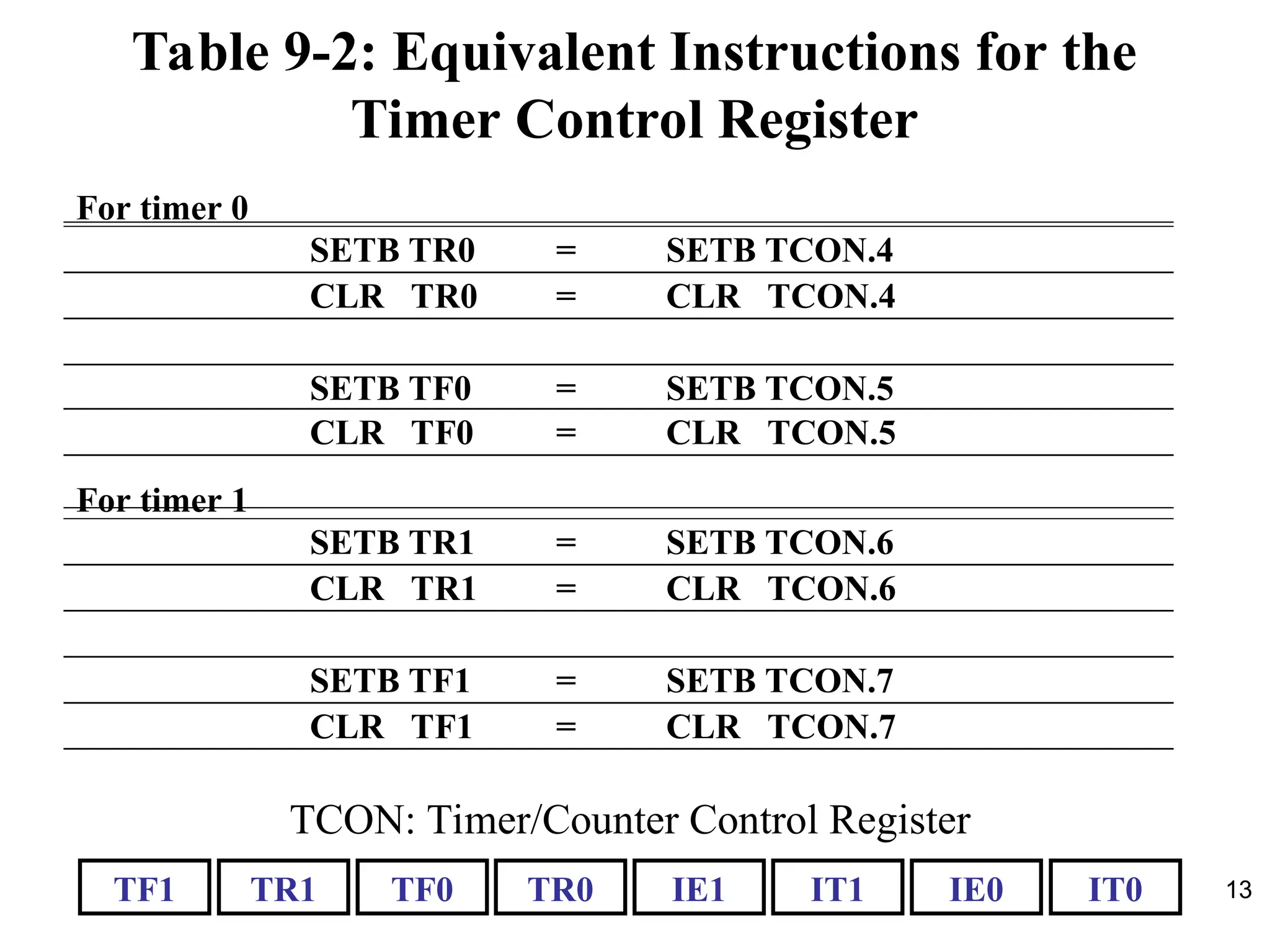

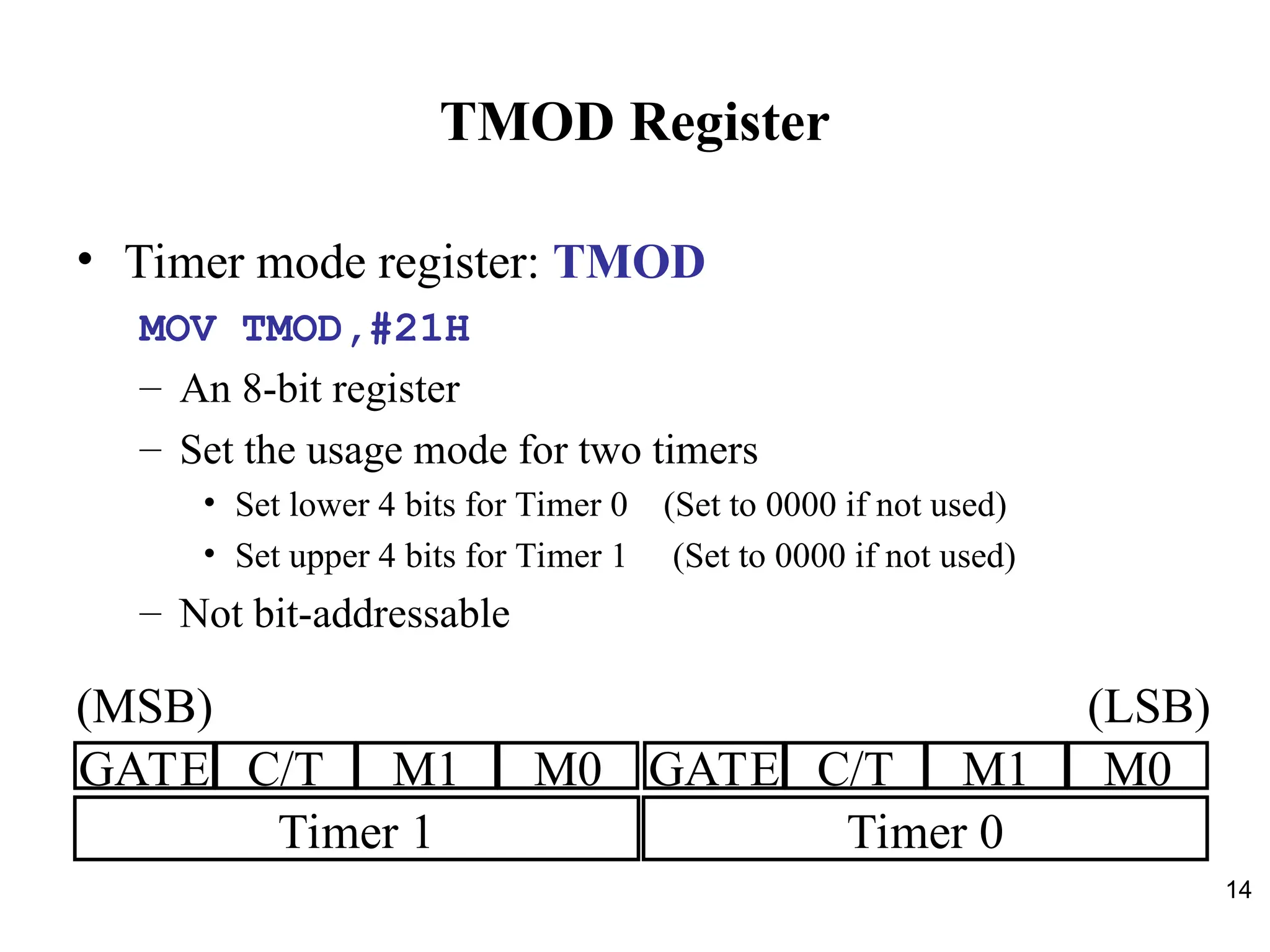

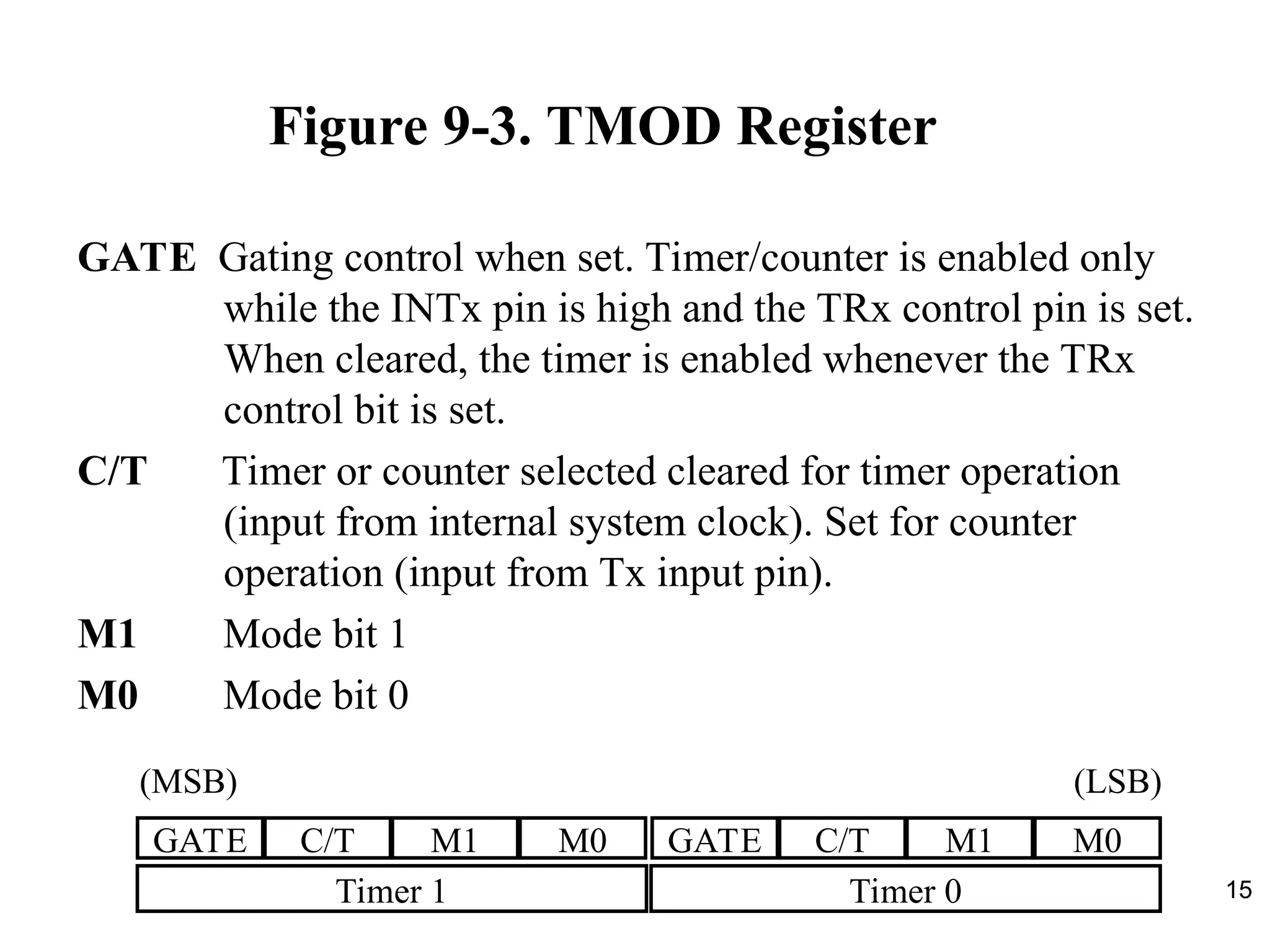

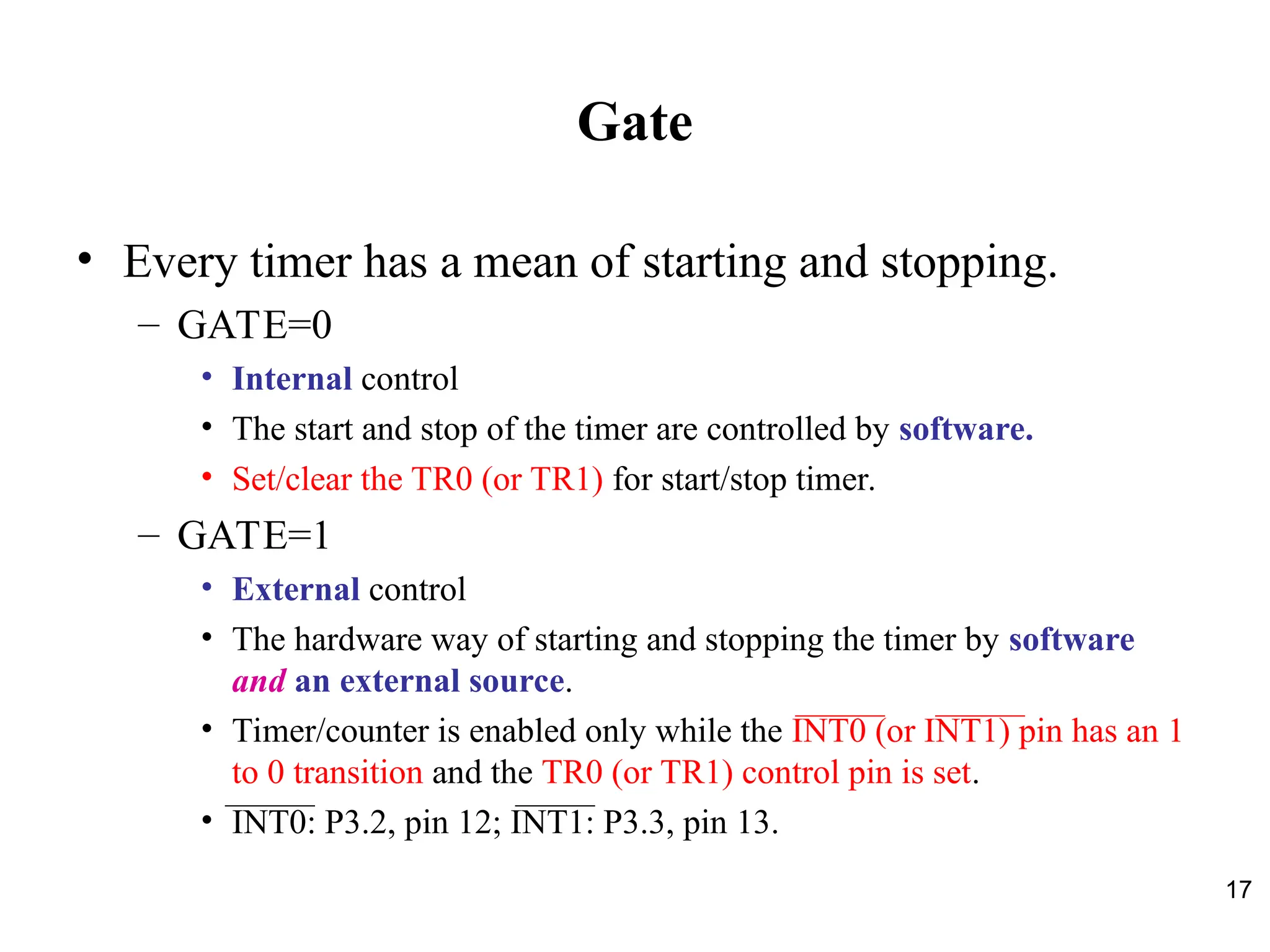

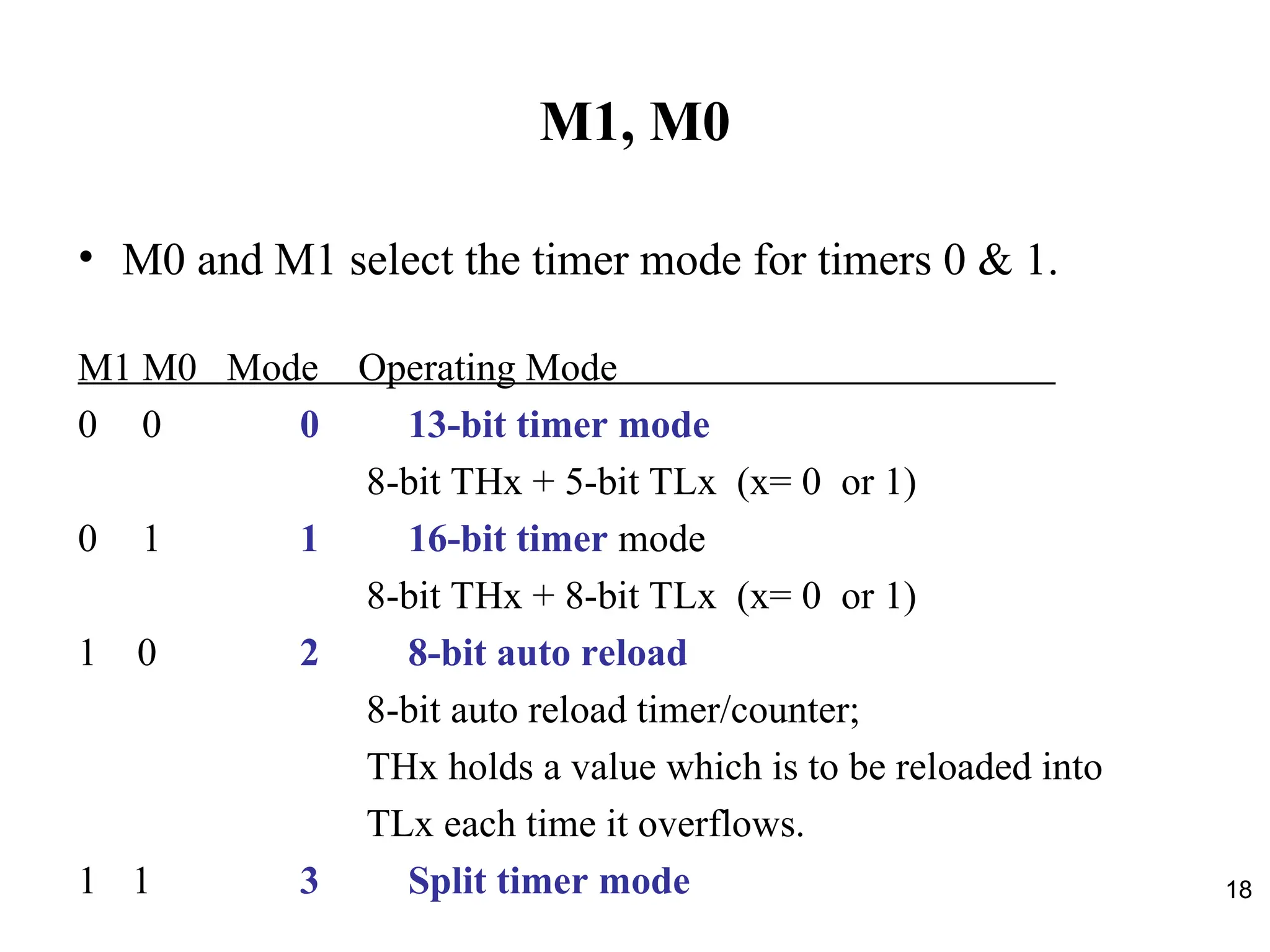

The document provides a detailed overview of timer programming in the 8051 microcontroller, outlining its architecture, operation modes, and the use of timers as delay generators and event counters. It discusses the registers associated with timers, including Timer 0 and Timer 1, and describes how to control these timers through various registers such as TCON and TMOD. Additionally, the document explains the configuration for using the timers effectively in assembly and C programming.