Downloaded 186 times

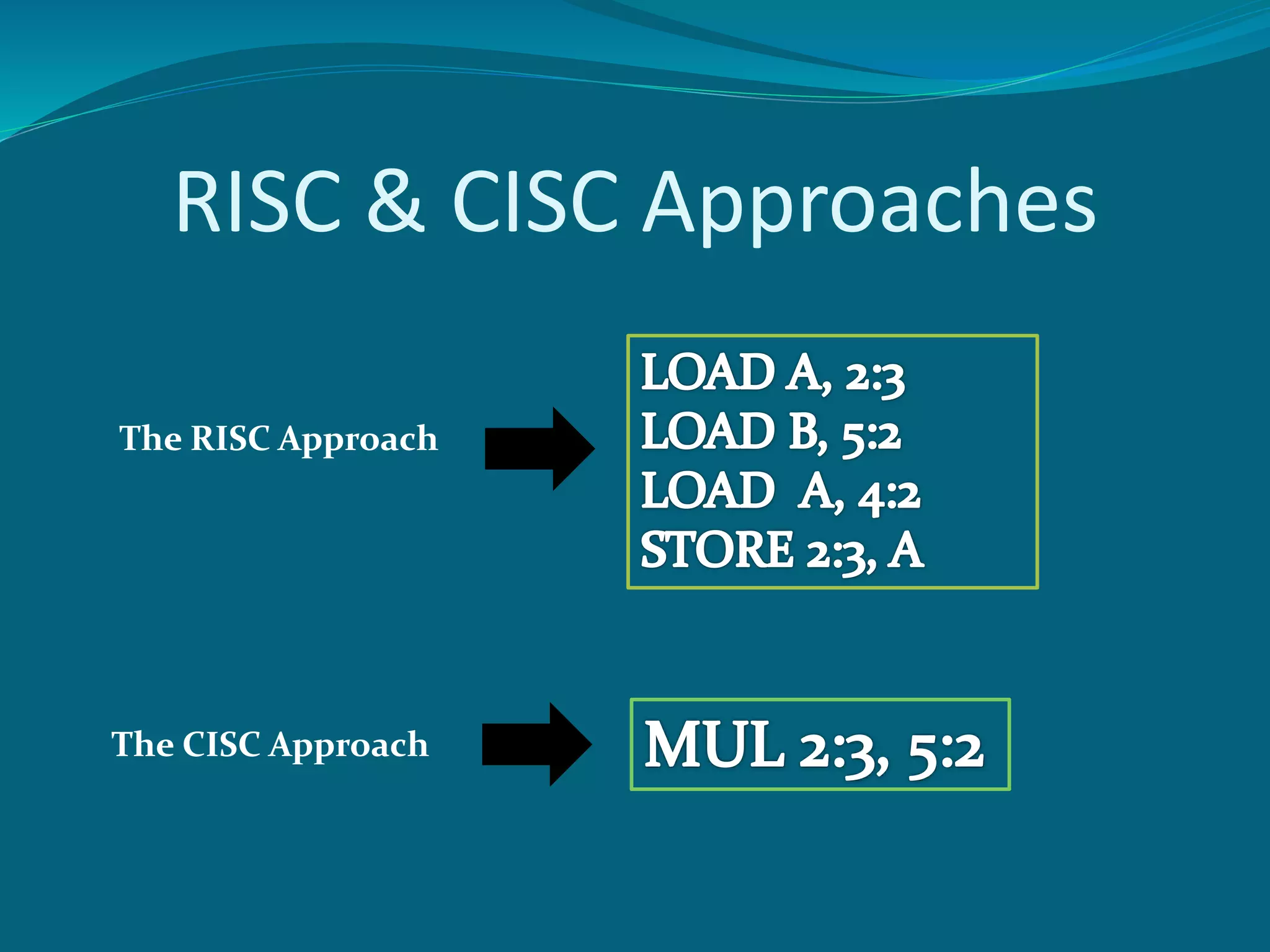

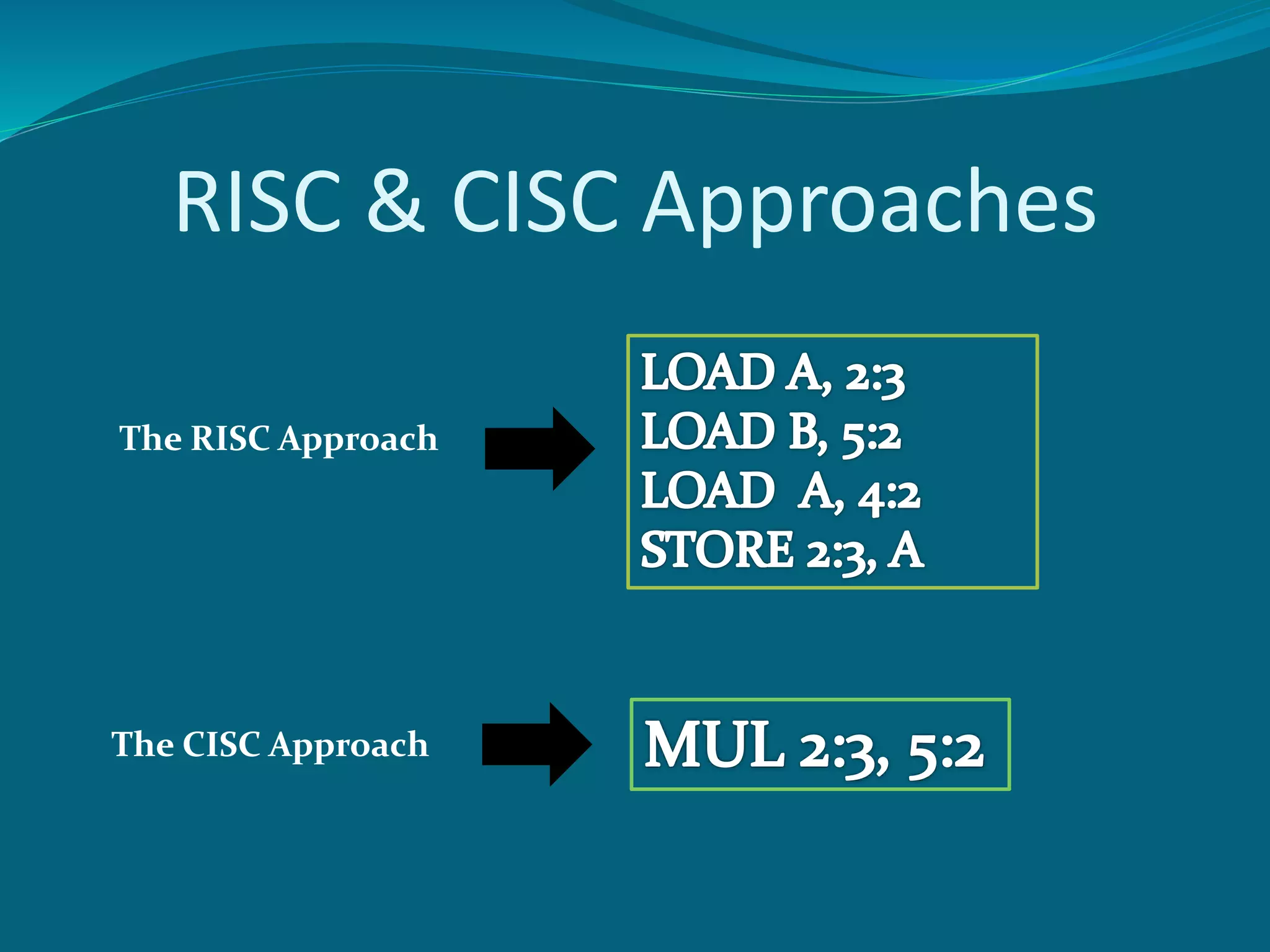

CISC processors have a large number of complex instructions that can perform operations directly from memory to memory. In contrast, RISC processors have a small set of simple instructions that operate only within registers, with load and store as separate instructions. The first RISC projects in the late 1970s-early 1980s from IBM, Stanford, and UC-Berkeley aimed for single-cycle execution with a fixed-length instruction format. RISC emphasizes hardware simplicity while CISC focuses on smaller code size and higher cycles per second.

Introduction of CISC (Complex Instruction Set Computer) and RISC (Reduced Instruction Set Computer) concepts by Adeel Rasheed.

CISC characterized by numerous complex instructions; RISC features a small, optimized instruction set.

Origin of RISC in the late 70s and early 80s with key projects from IBM, Stanford, and UC-Berkeley.

Key features of RISC processors include register operations, limited addressing modes, and efficiency.

CISC processors focus on hardware efficiency with complex multi-clock instructions and memory operations.

Contrasting approaches of CISC with its comprehensive instructions versus the simplified RISC methodology.

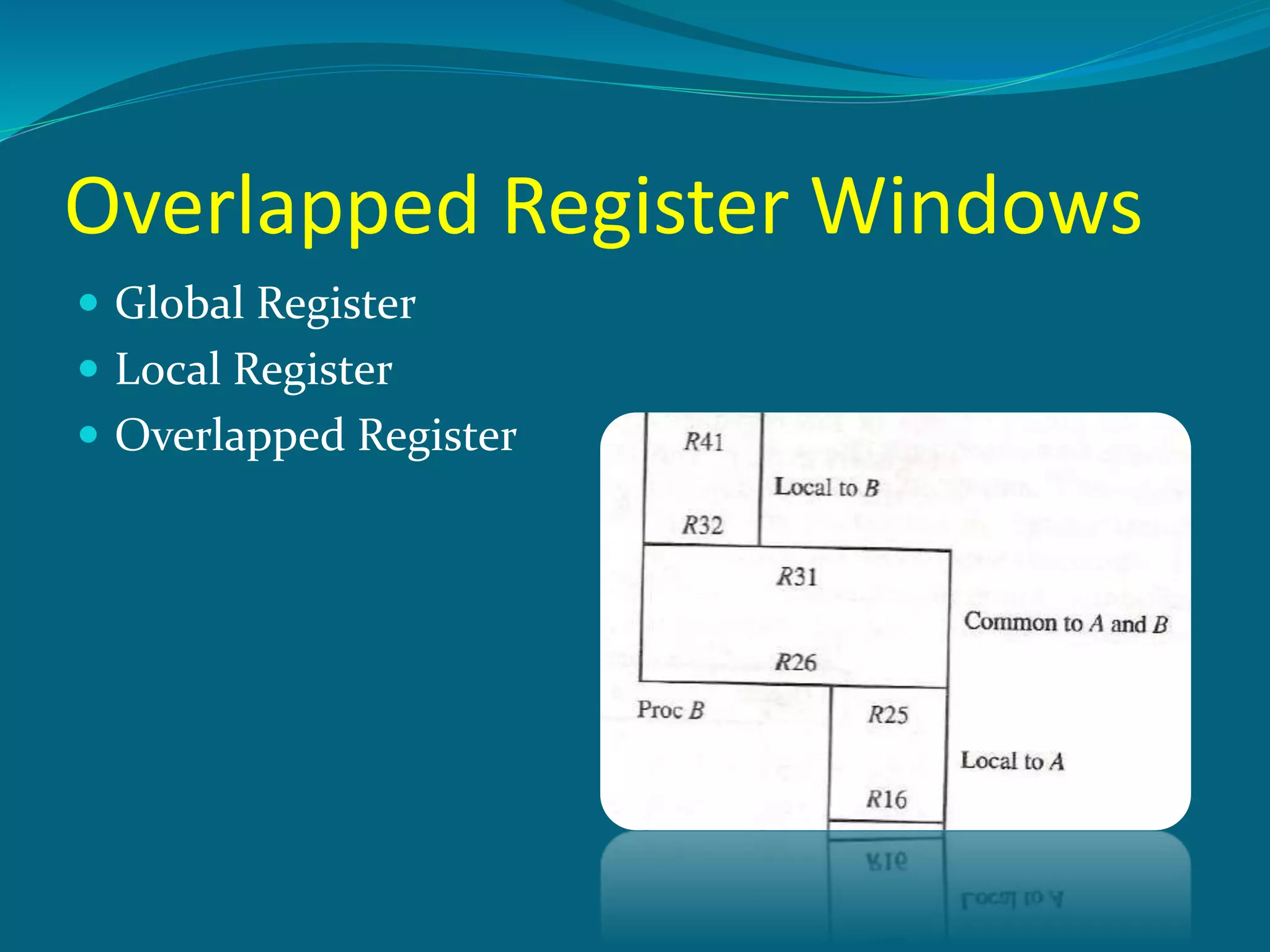

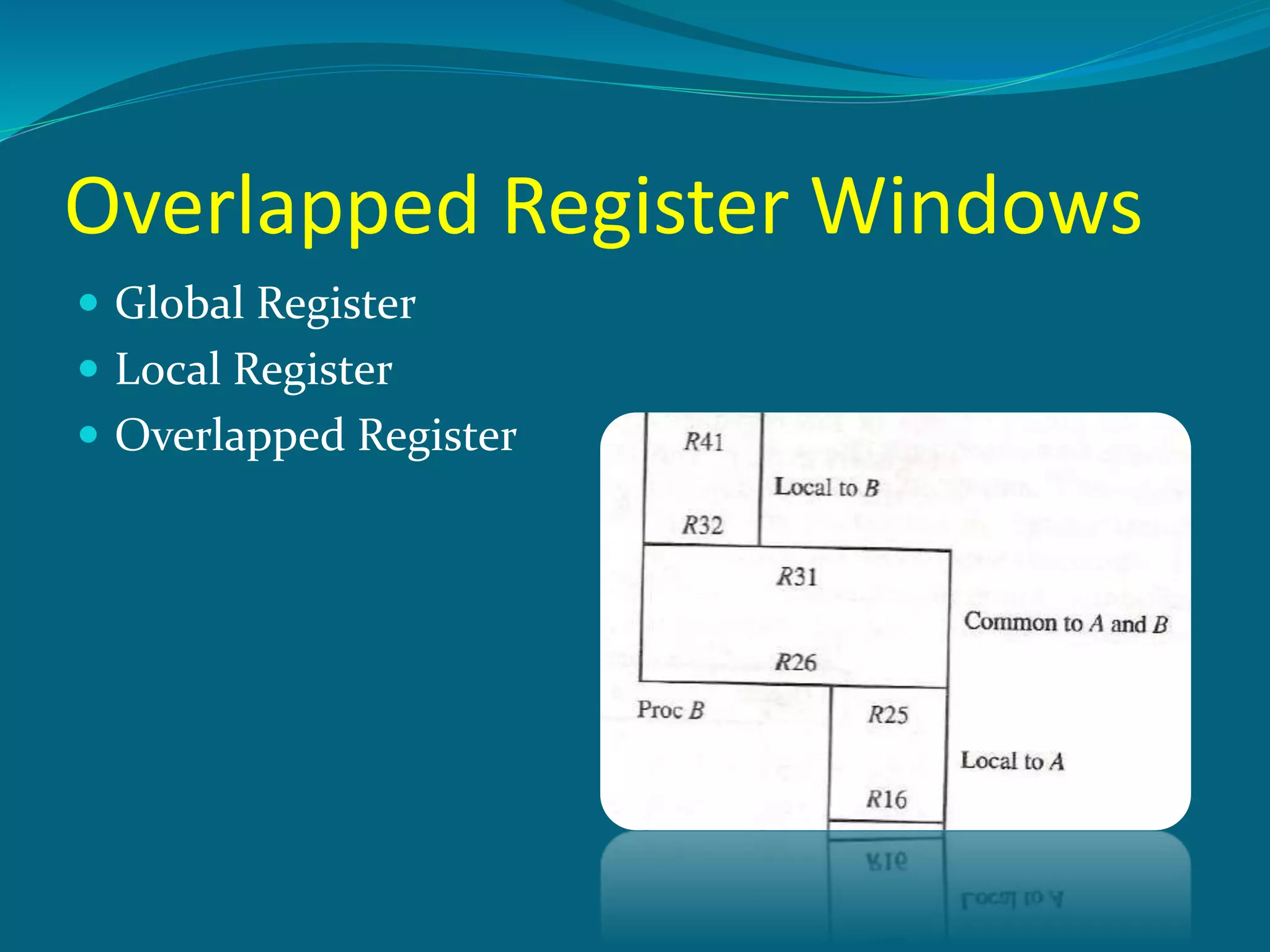

Introduction to overlapped register windows, comprising global, local, and overlapped registers in architecture.