0% found this document useful (0 votes)

5 views2 pagesMHW On Computer Architecture

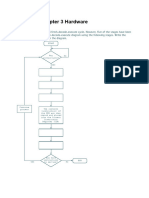

This document is a Computer Science assessment for Class IX focusing on Chapter 3, Computer Architecture, with a submission date of October 27, 2024. It includes questions about the von Neumann architecture, the fetch-decode-execute (FDE) cycle, and the components of a CPU. The assessment consists of multiple tasks including matching descriptions to buses, drawing diagrams, and sequencing stages of the FDE cycle.

Uploaded by

yiyadok303Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

5 views2 pagesMHW On Computer Architecture

This document is a Computer Science assessment for Class IX focusing on Chapter 3, Computer Architecture, with a submission date of October 27, 2024. It includes questions about the von Neumann architecture, the fetch-decode-execute (FDE) cycle, and the components of a CPU. The assessment consists of multiple tasks including matching descriptions to buses, drawing diagrams, and sequencing stages of the FDE cycle.

Uploaded by

yiyadok303Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 2