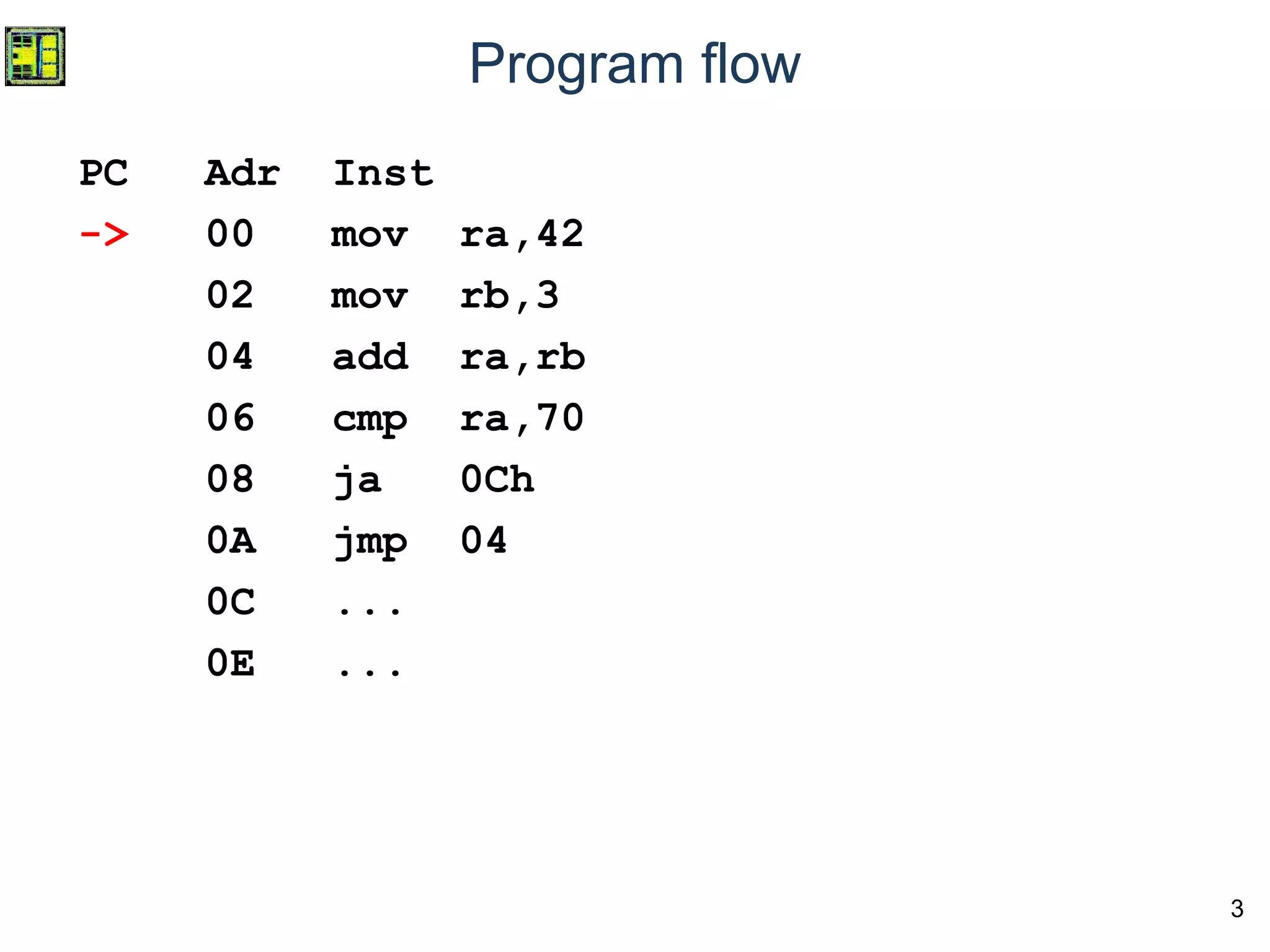

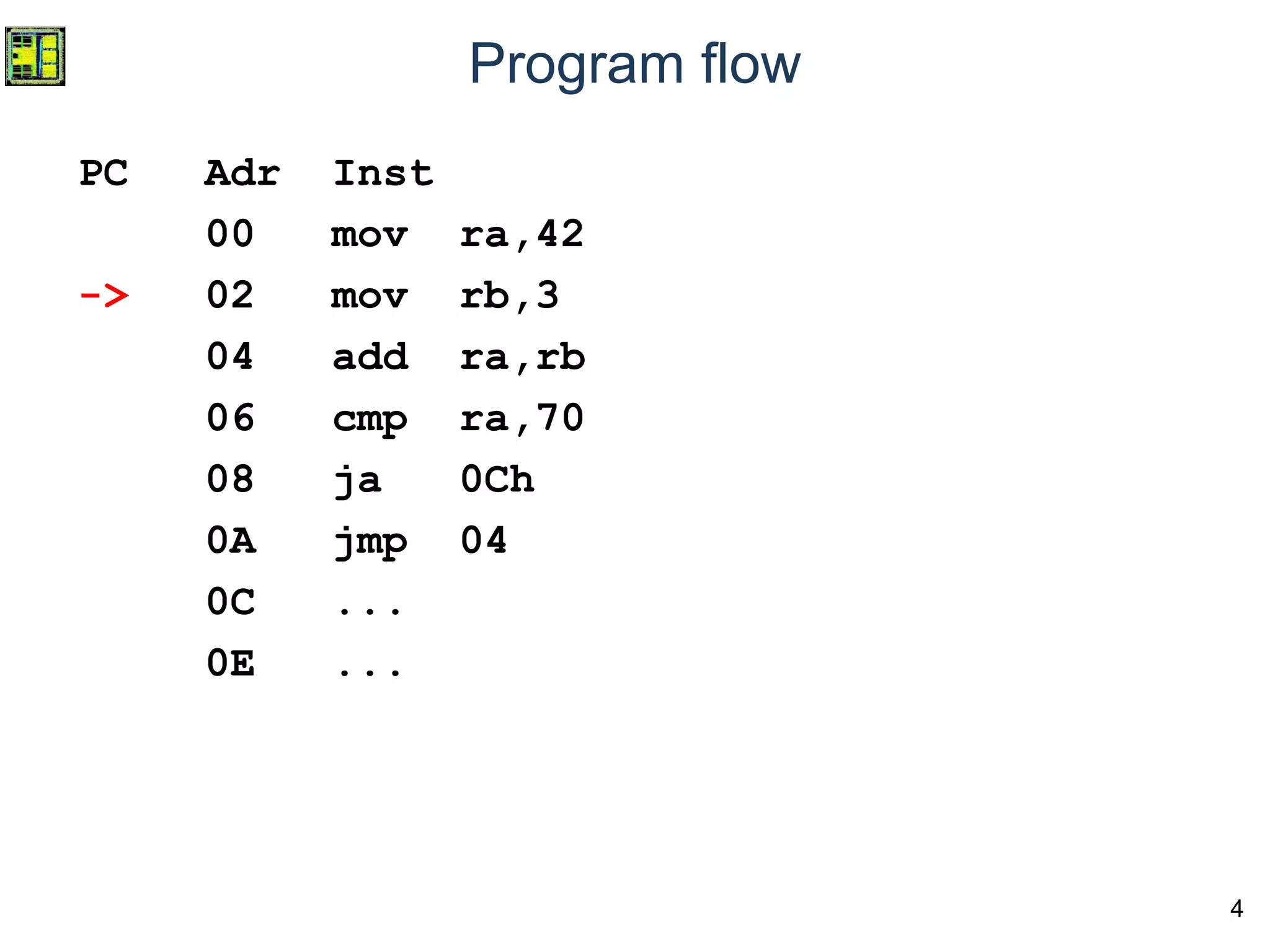

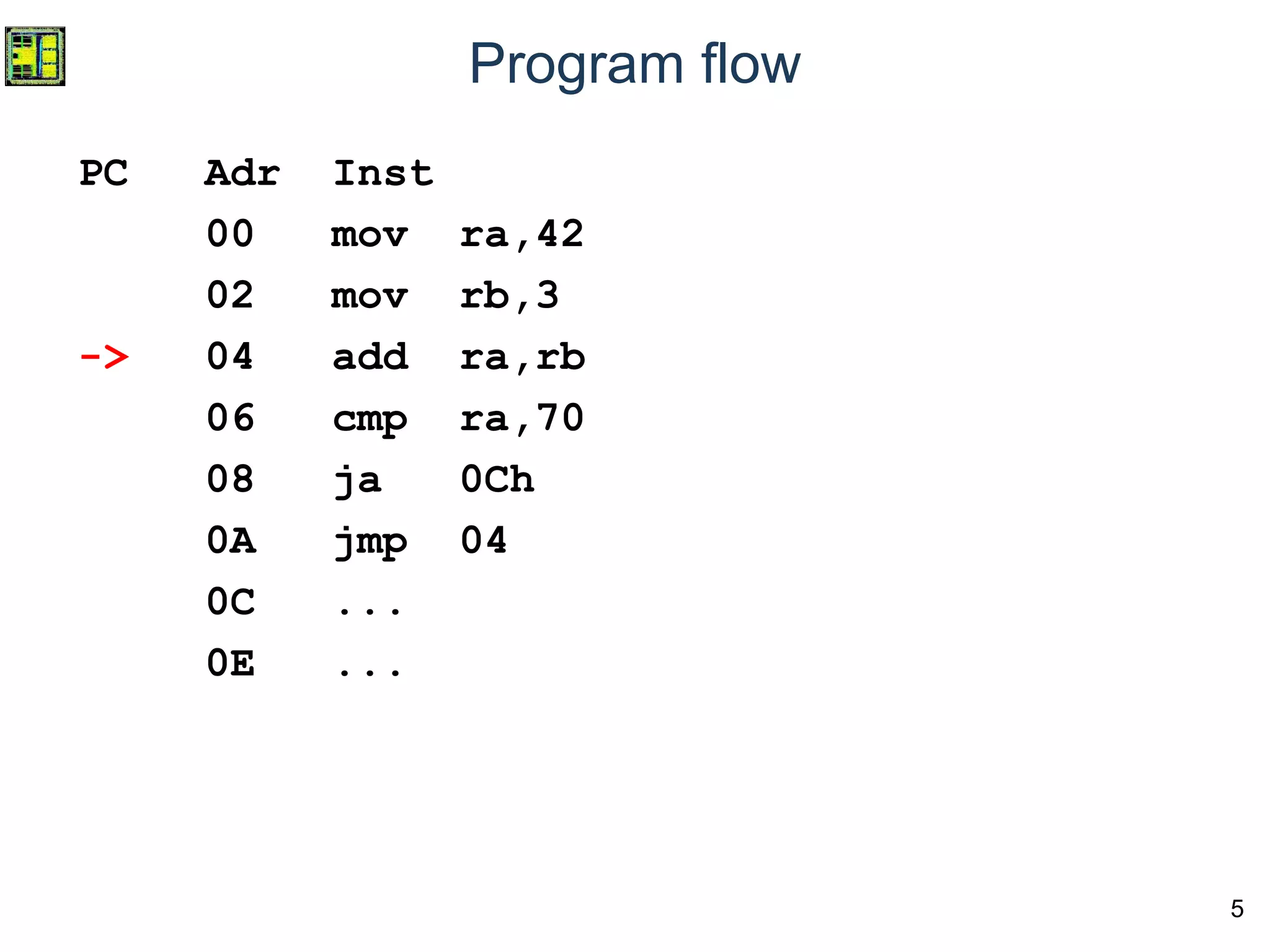

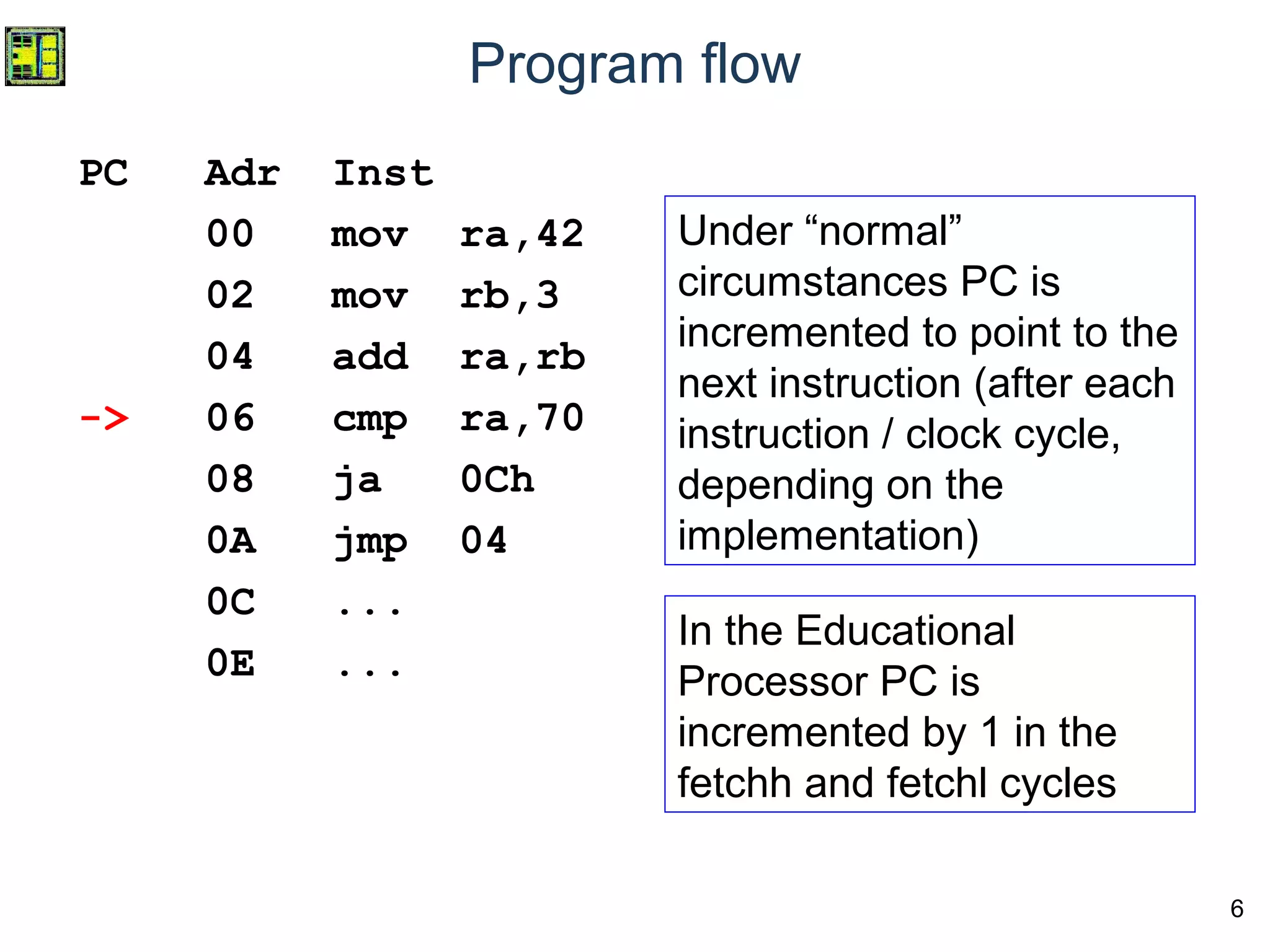

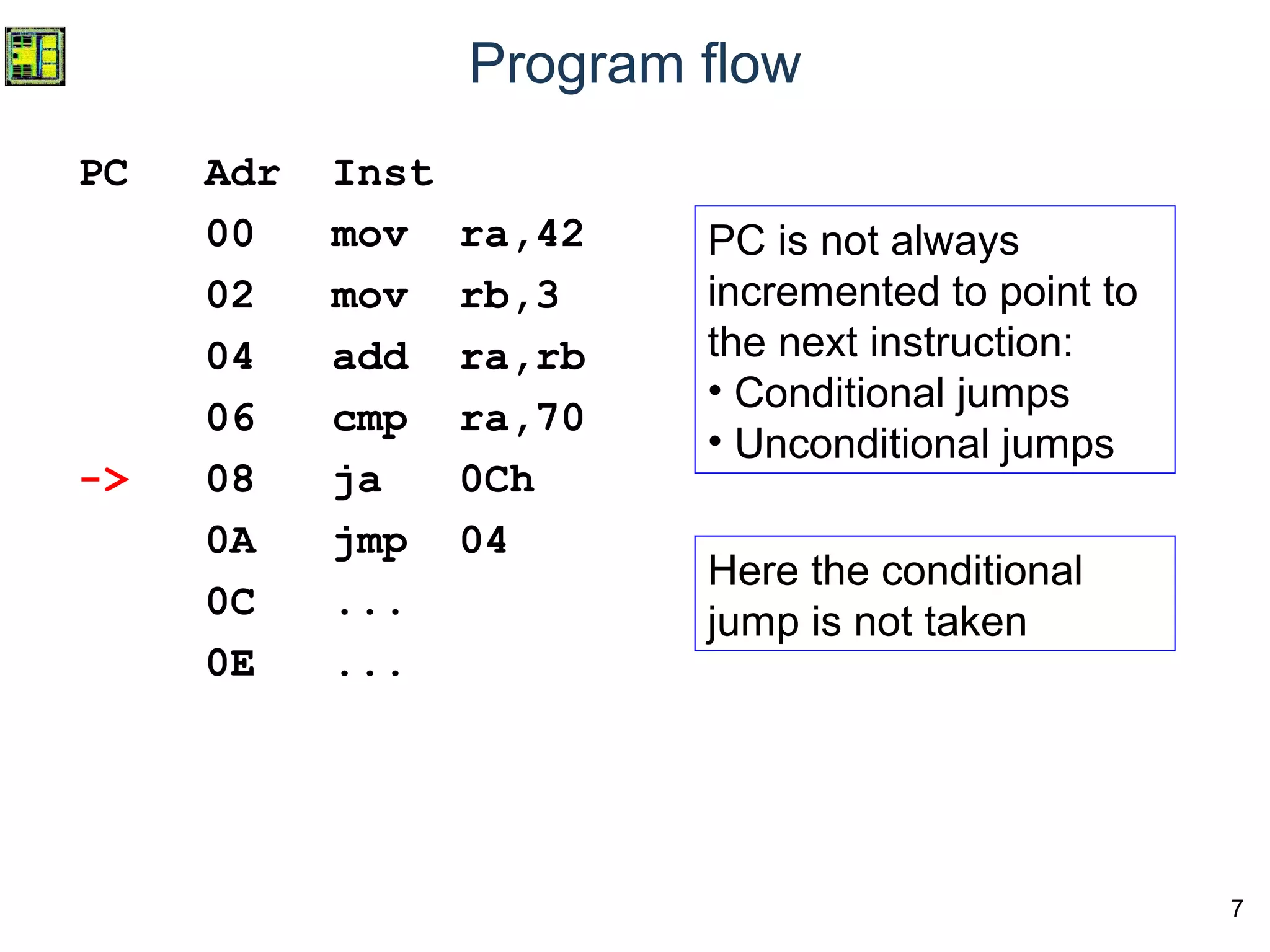

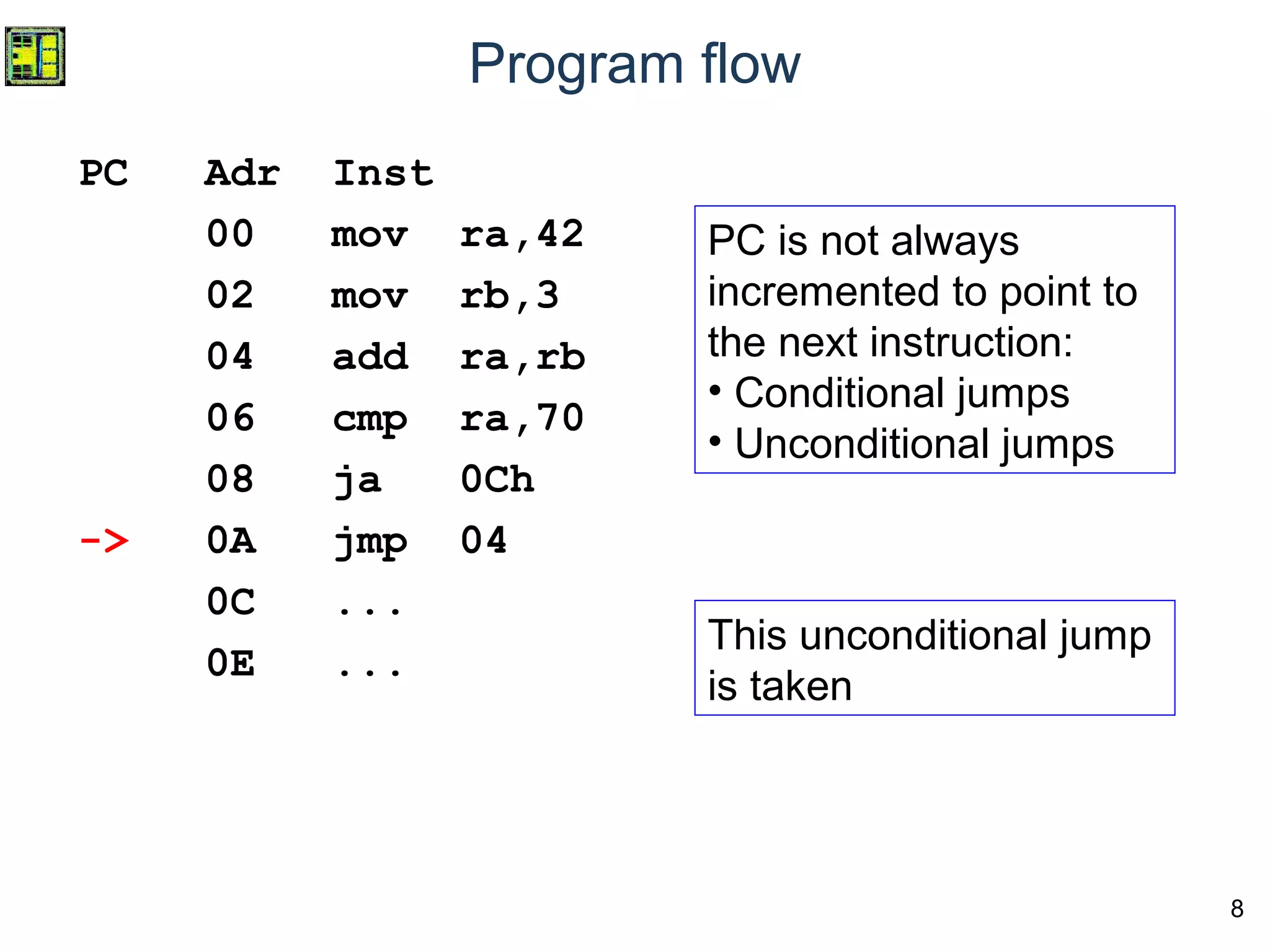

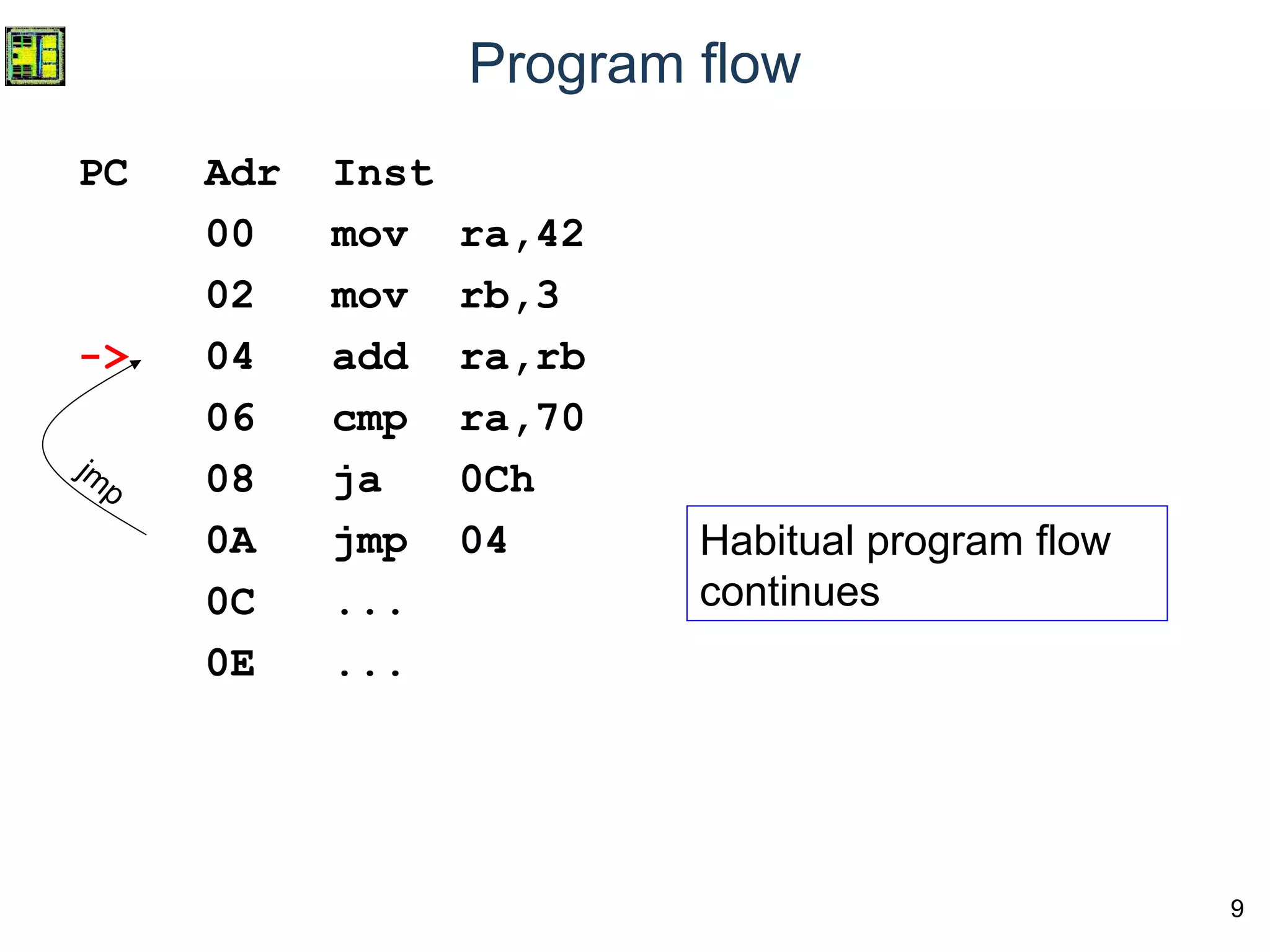

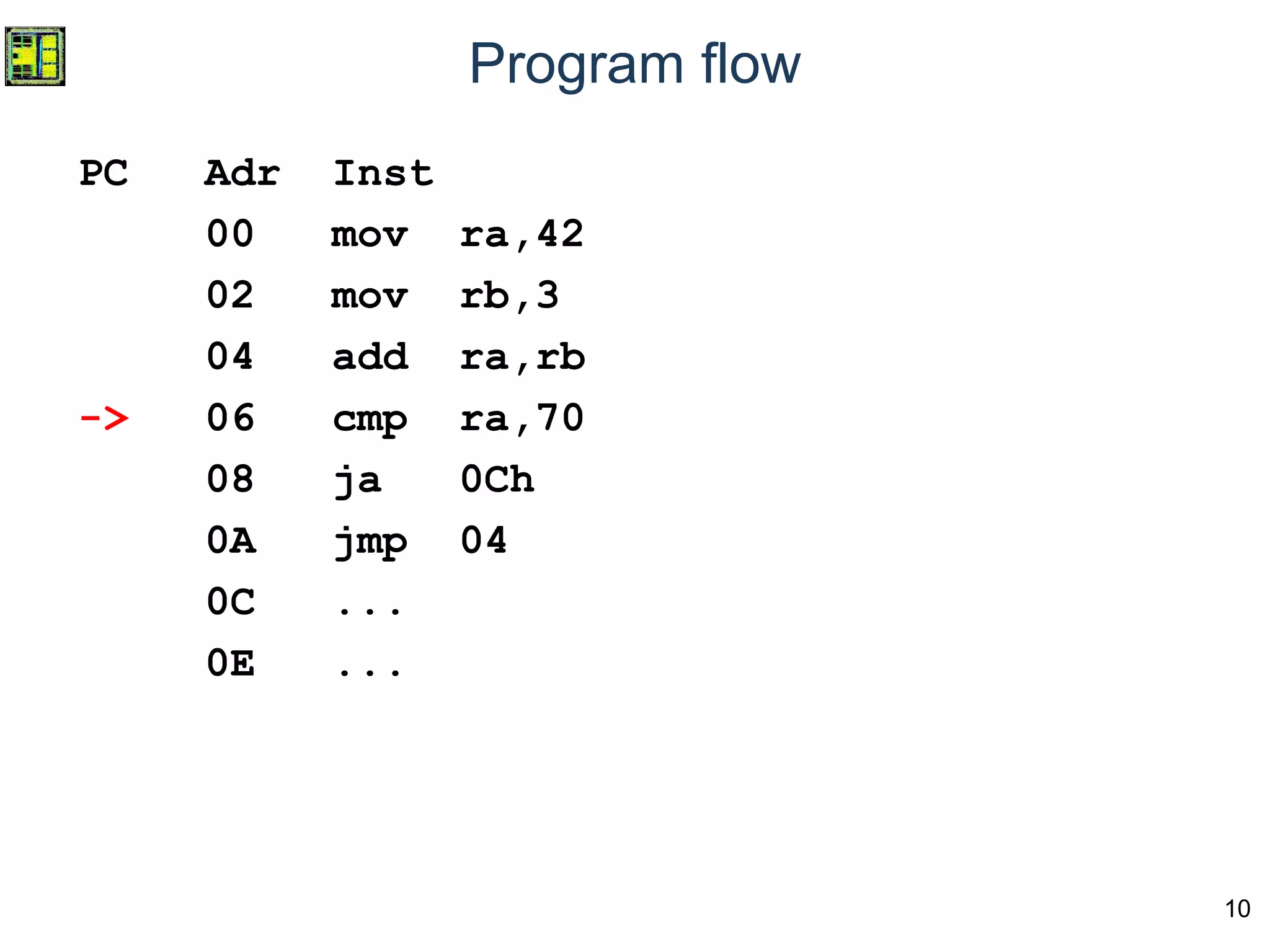

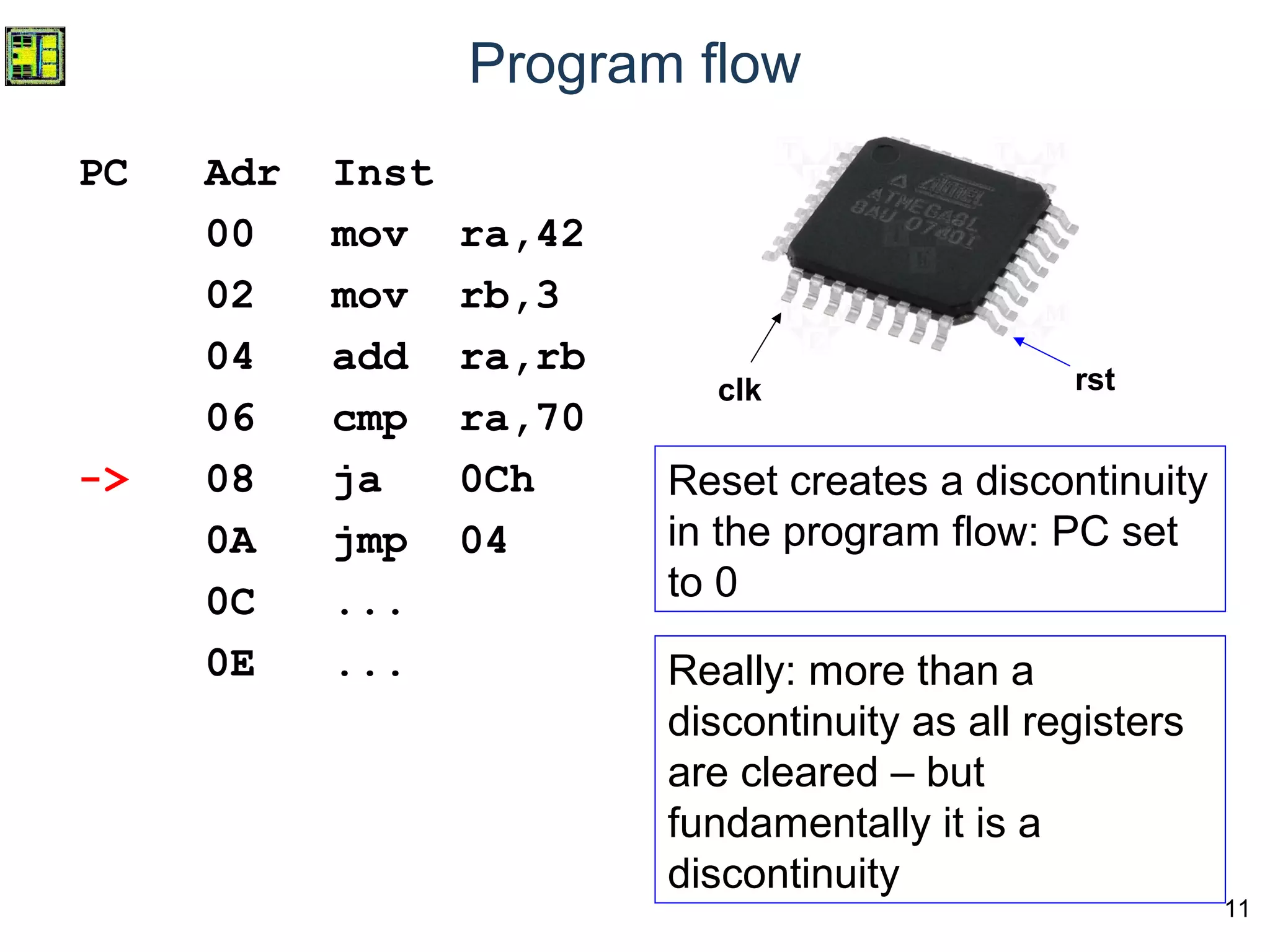

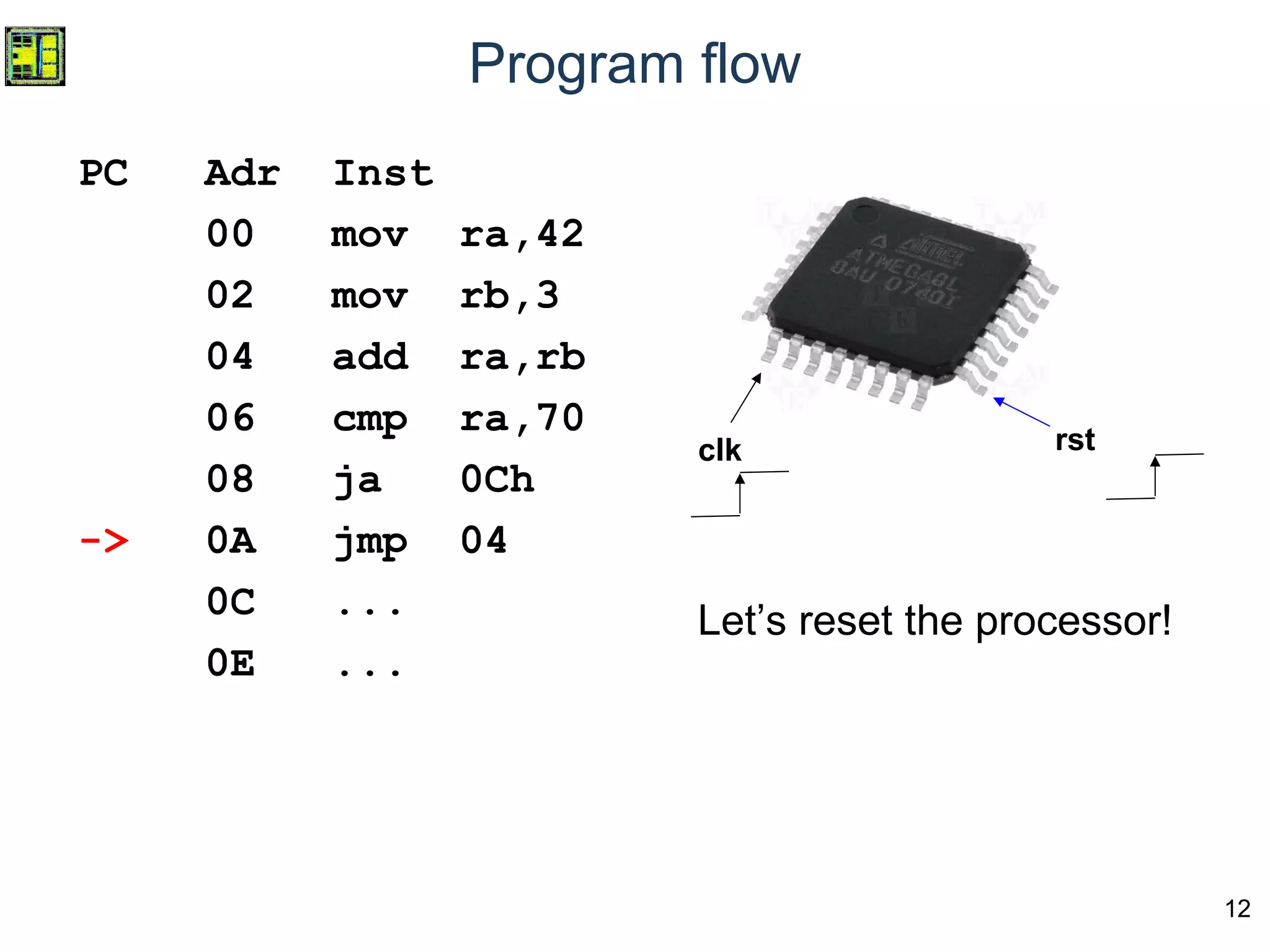

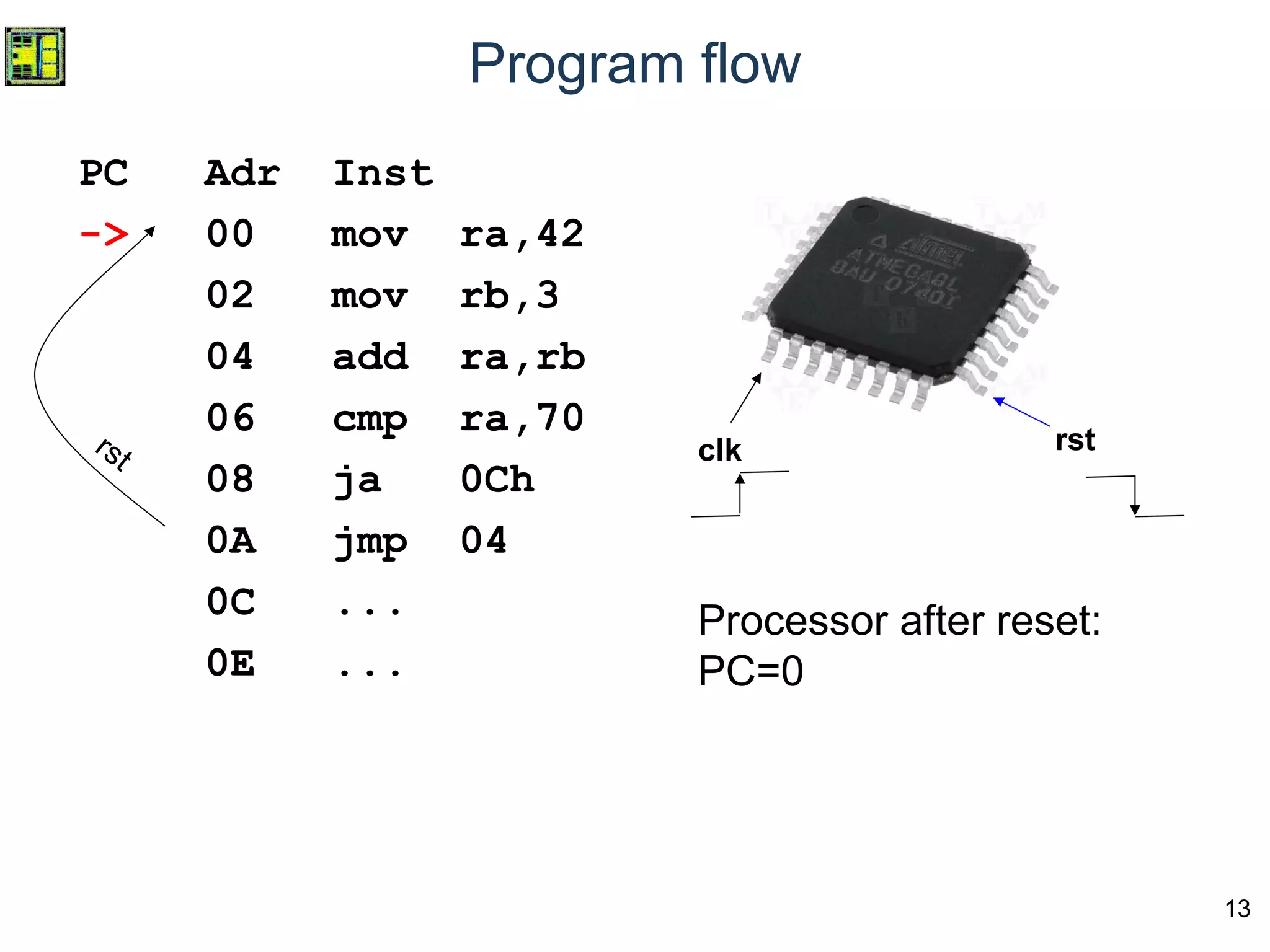

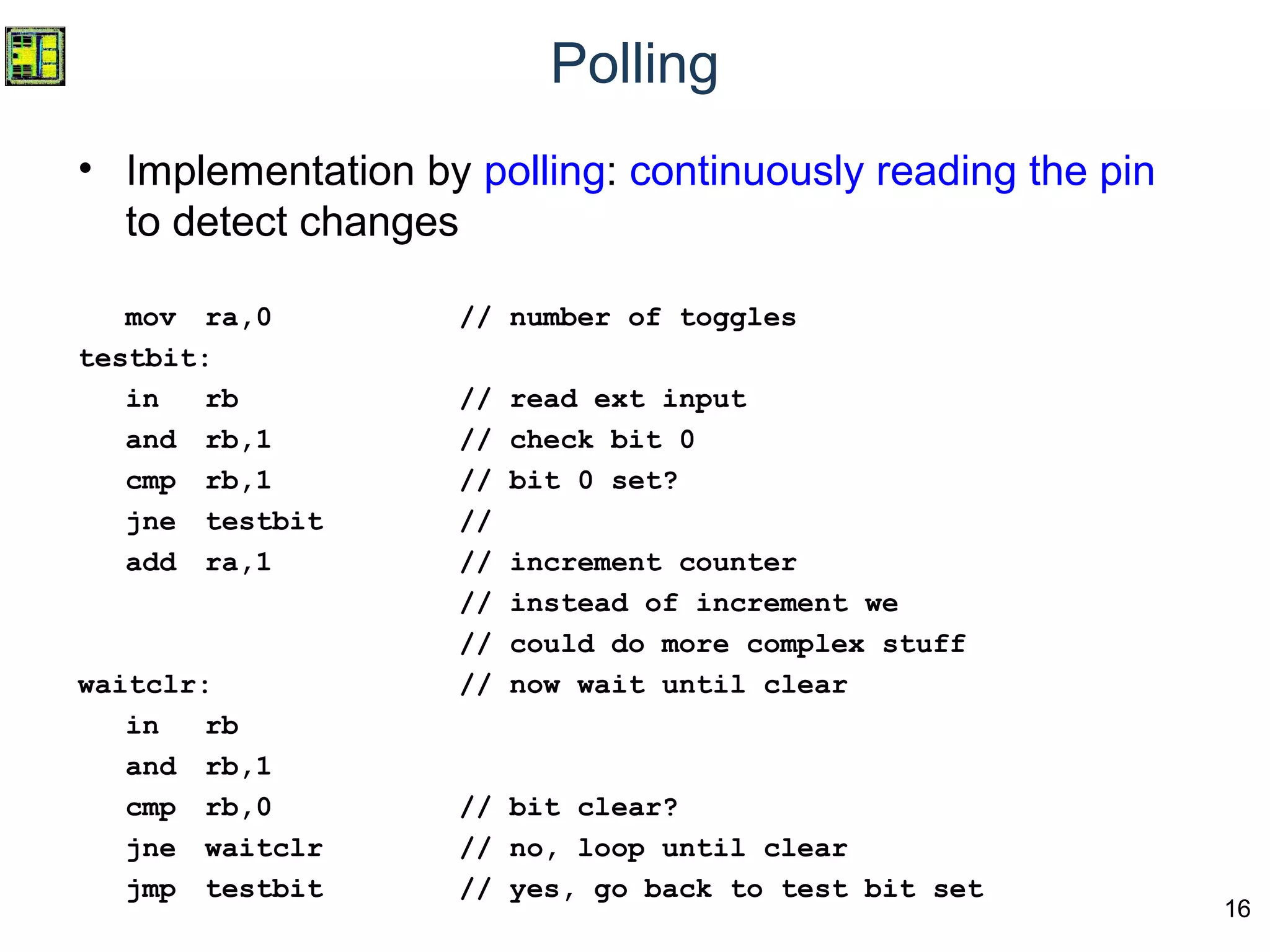

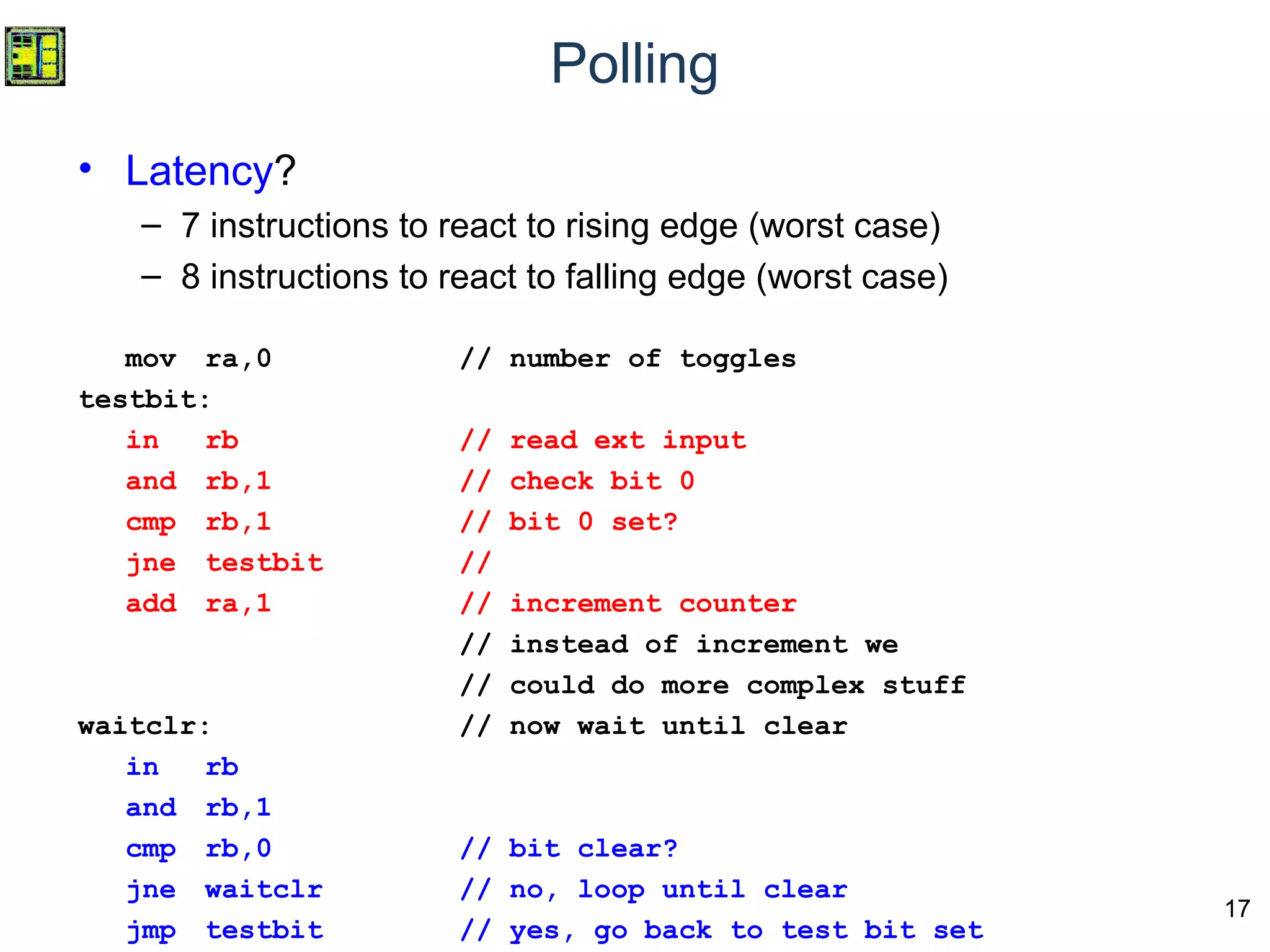

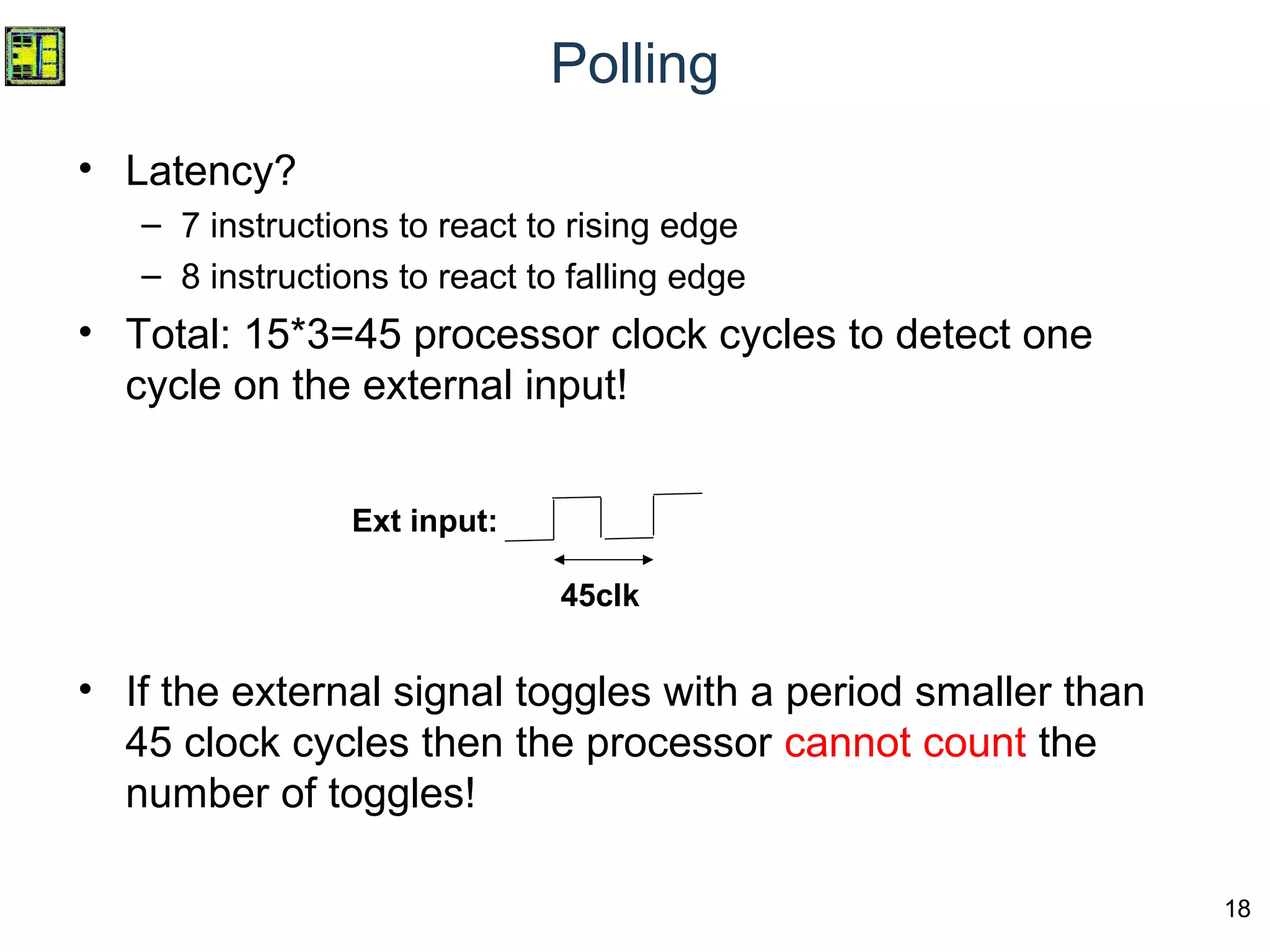

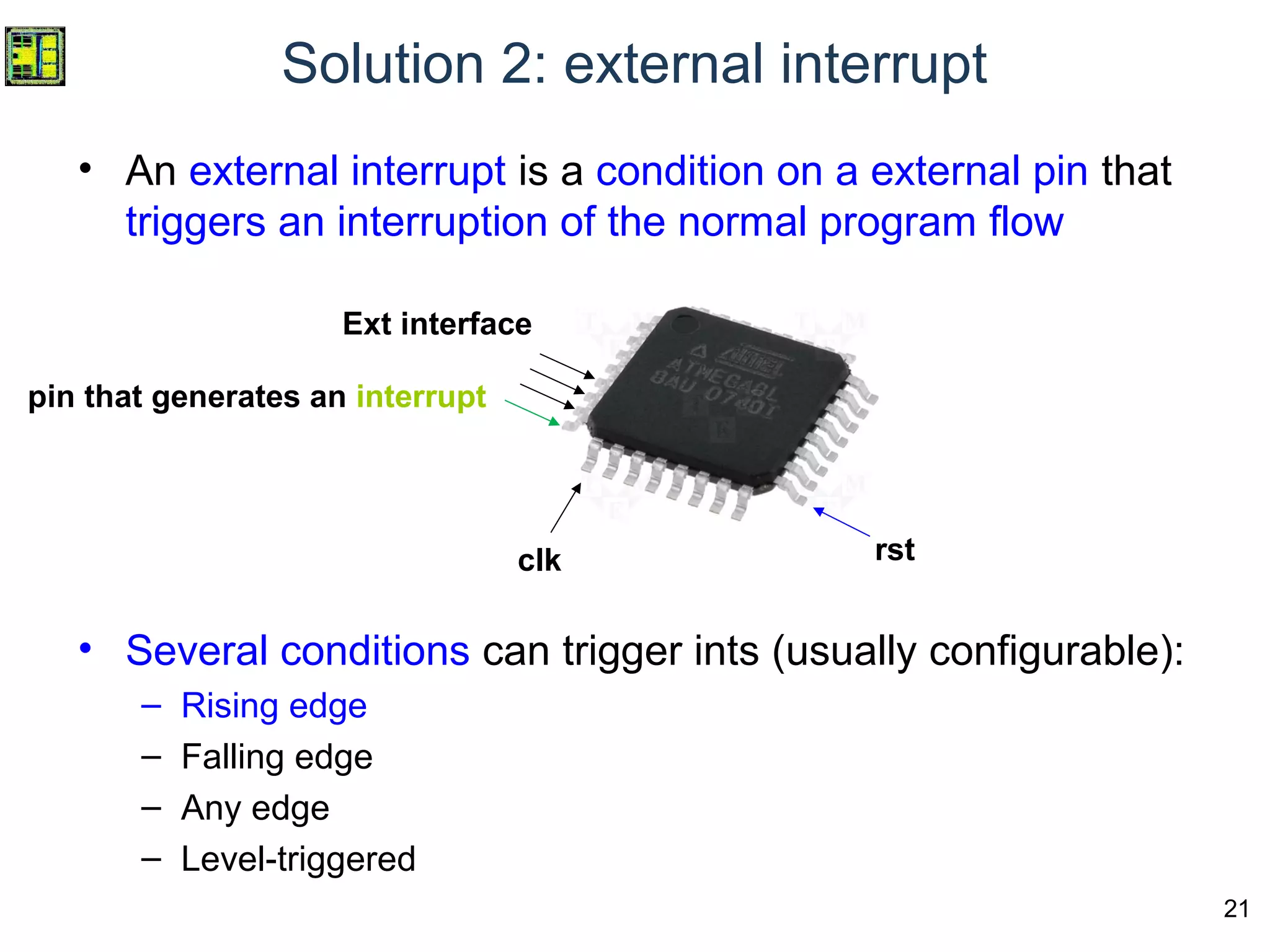

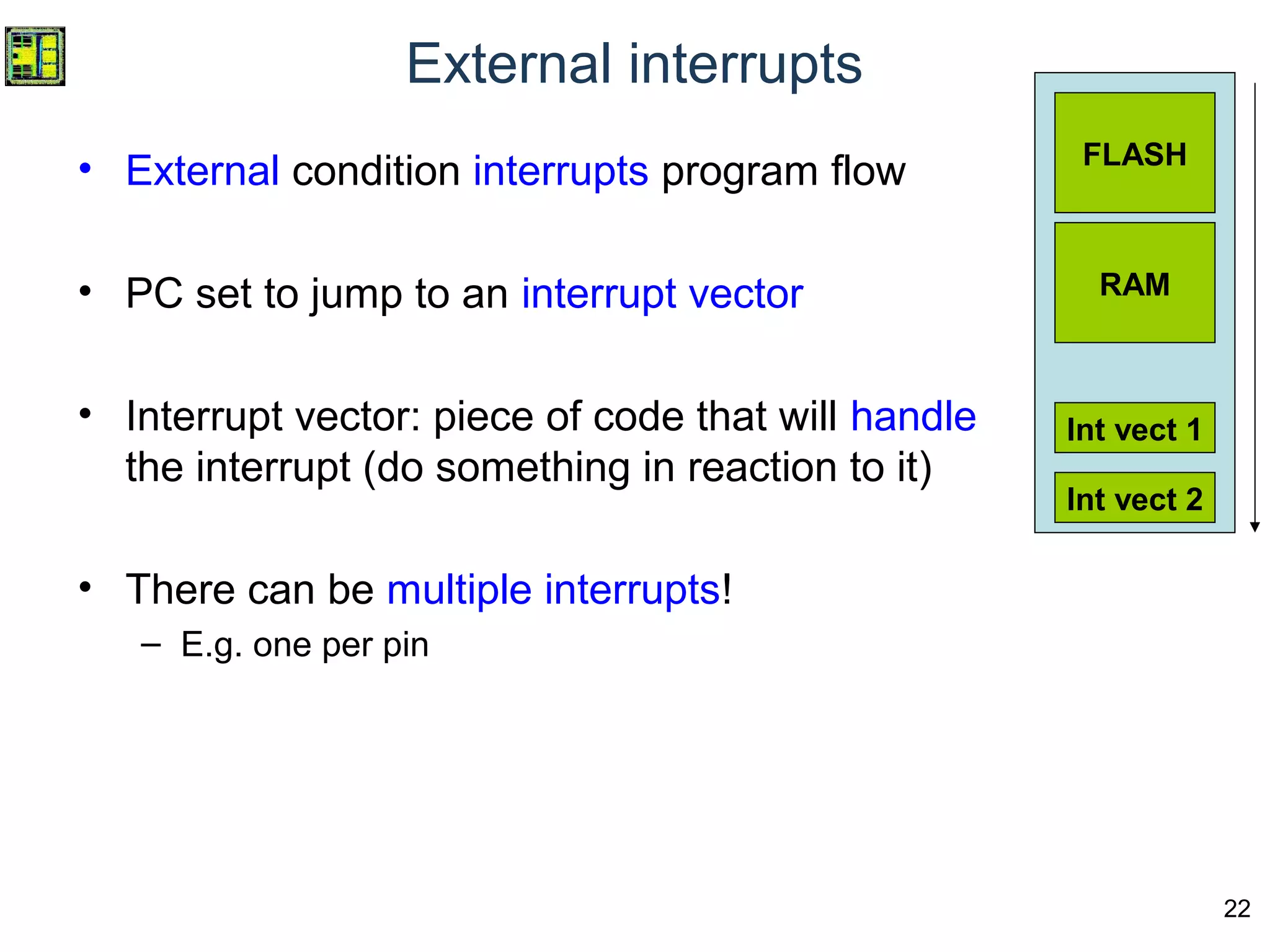

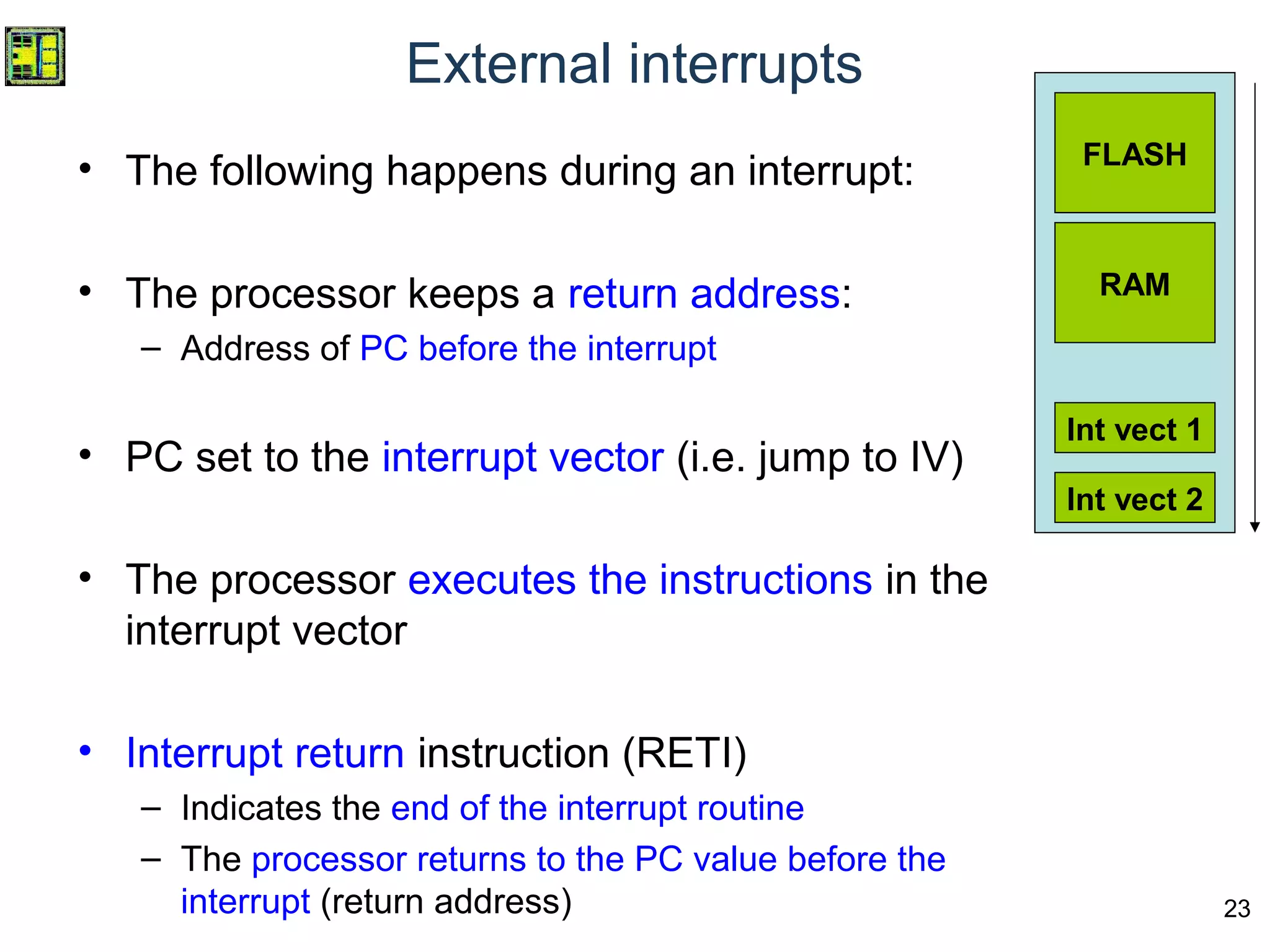

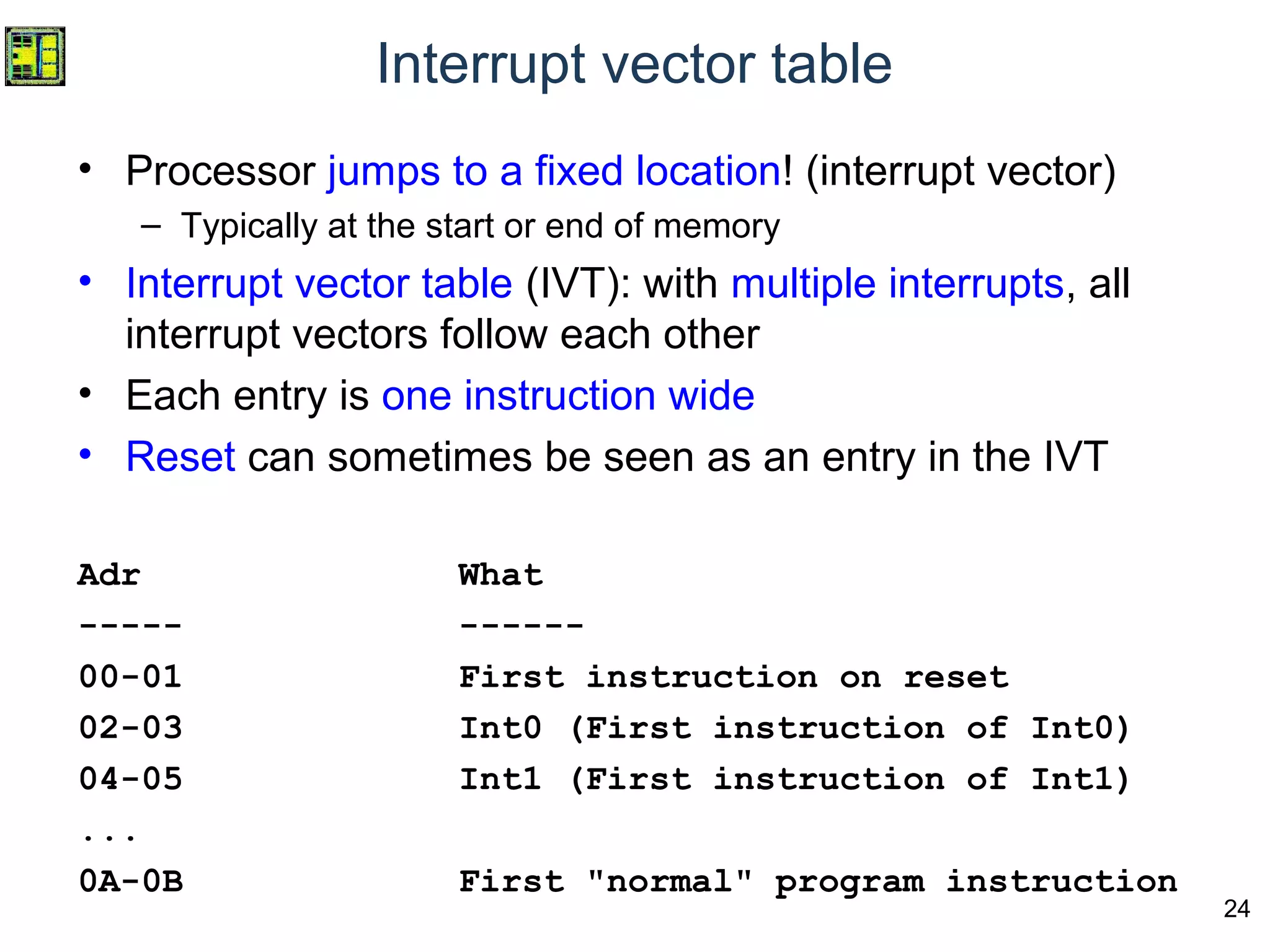

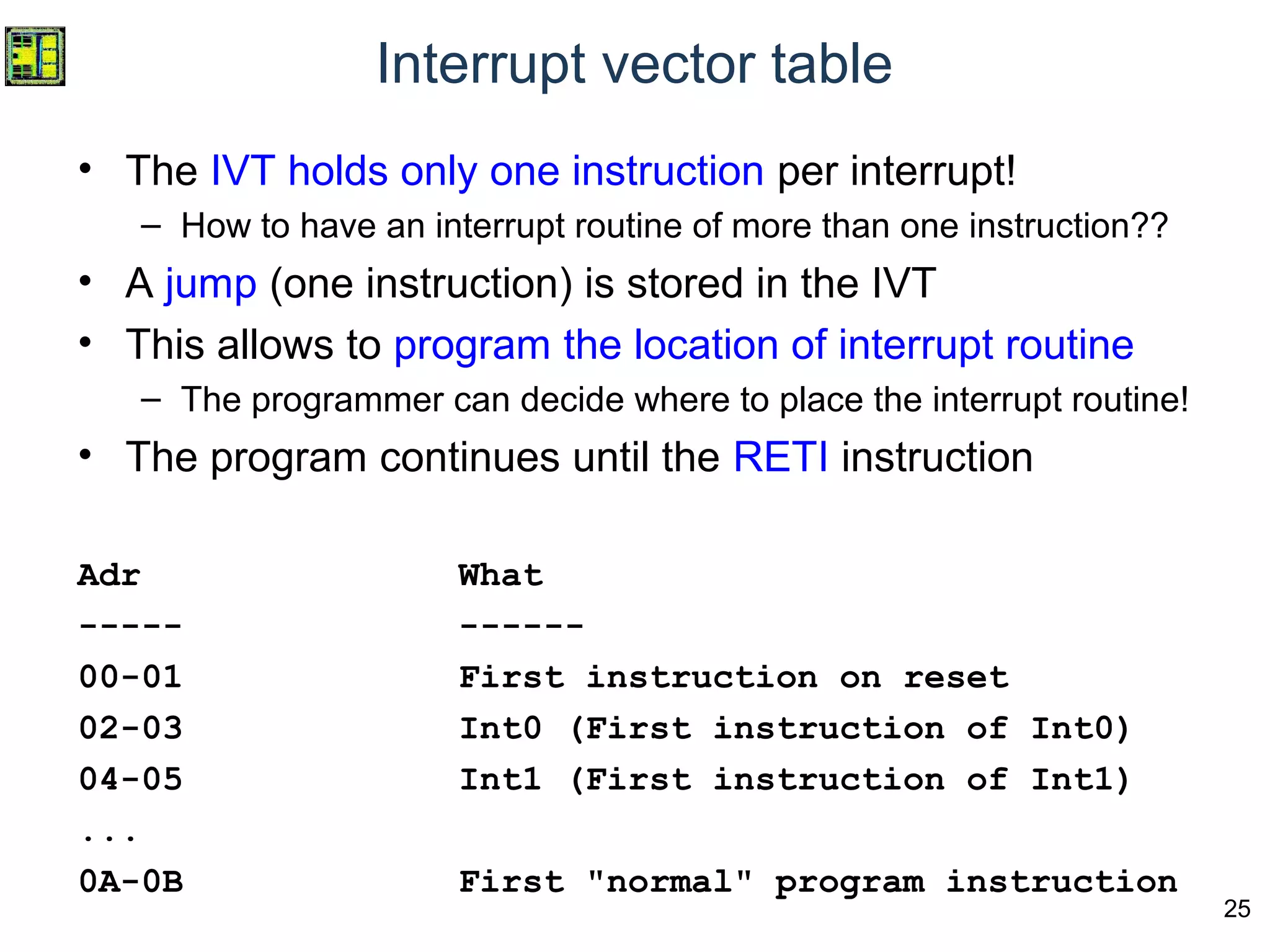

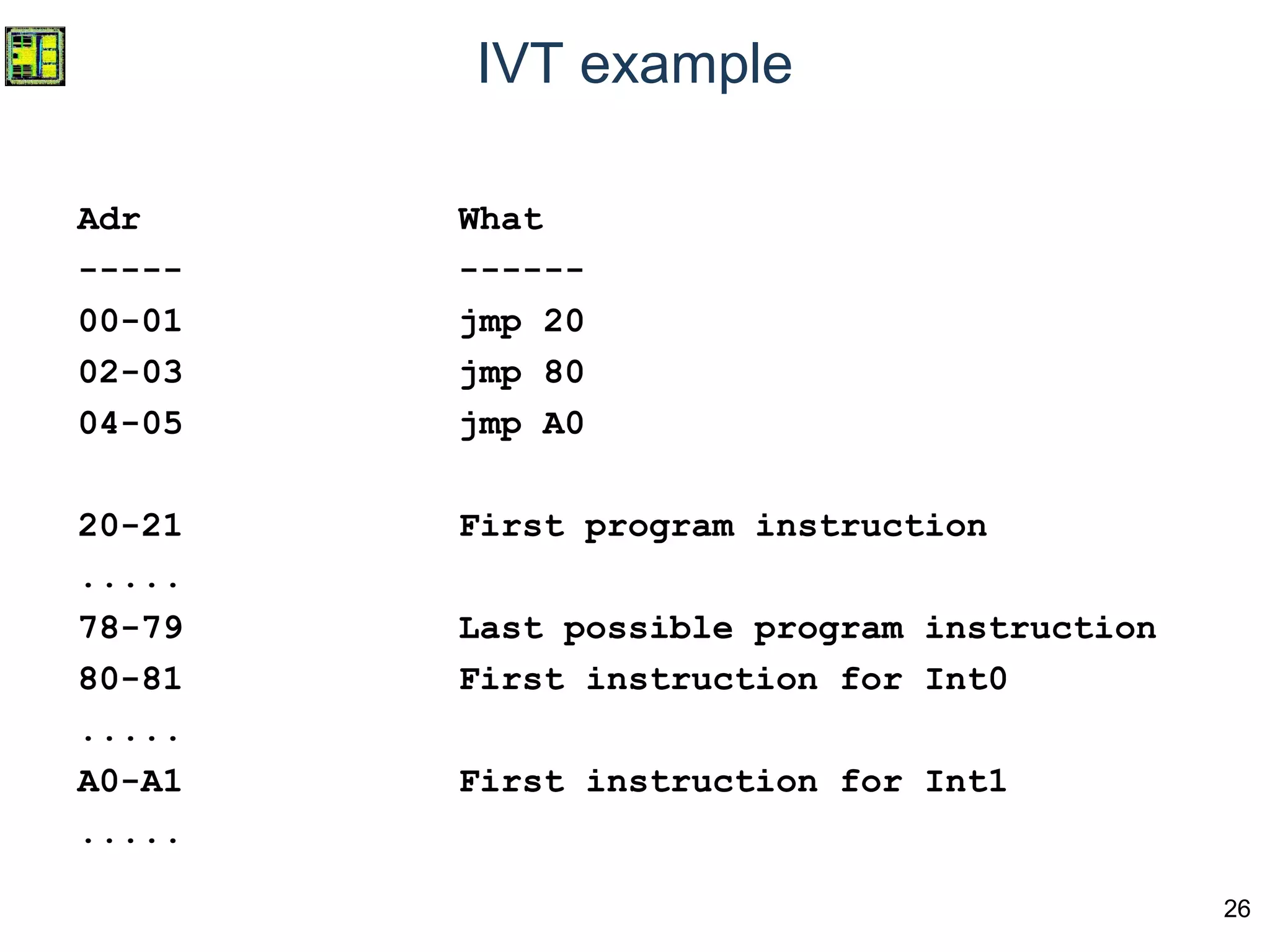

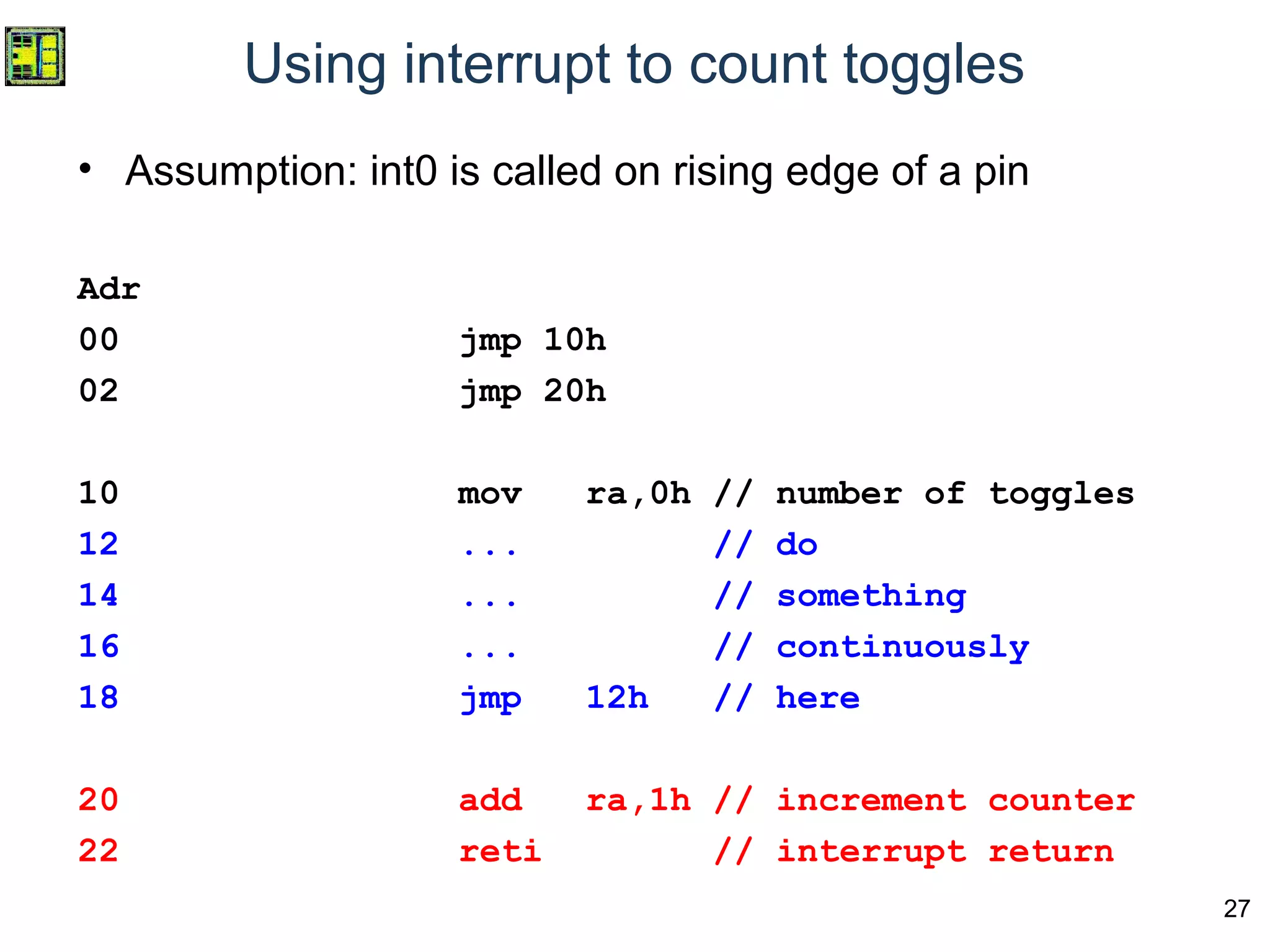

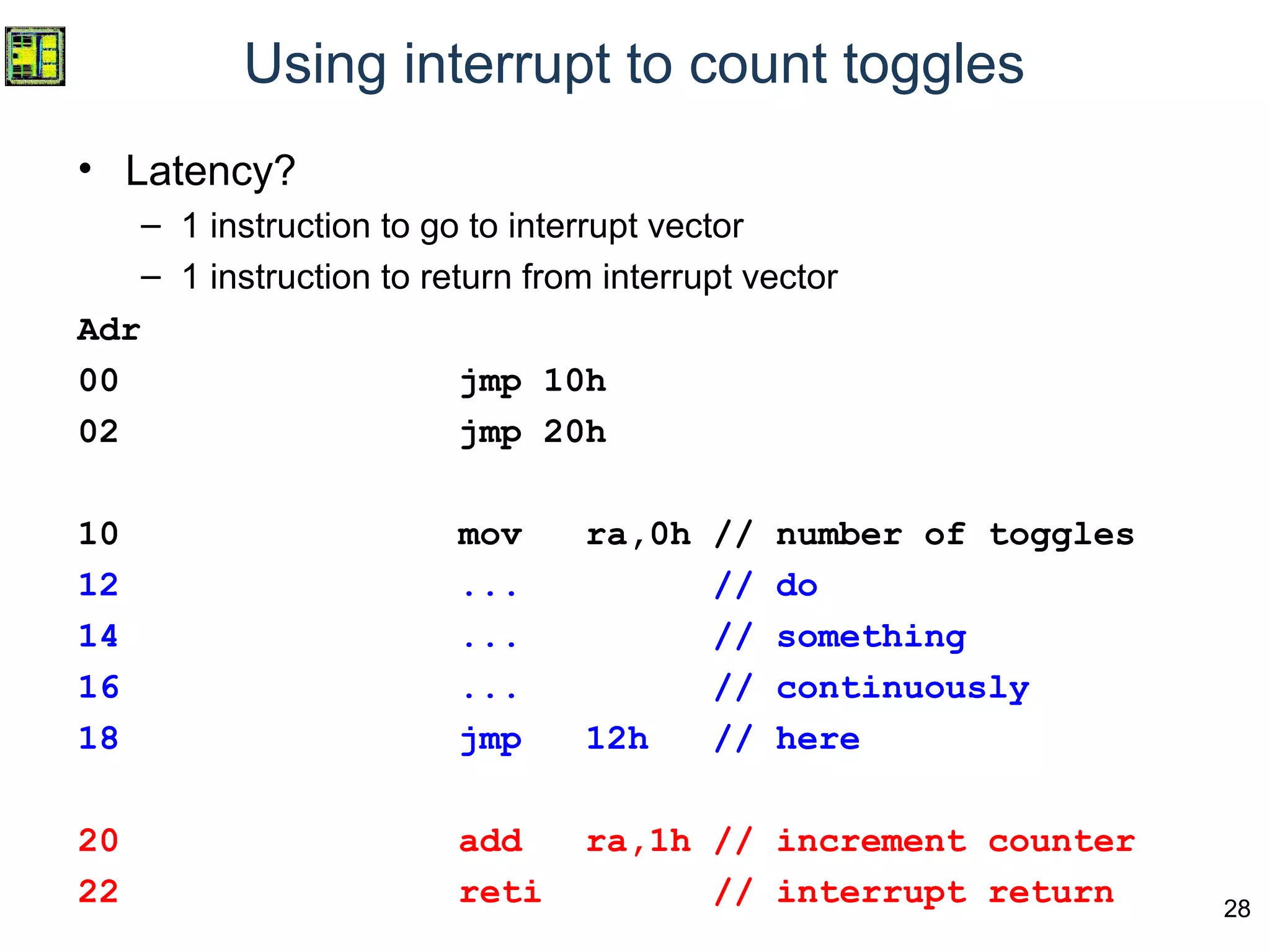

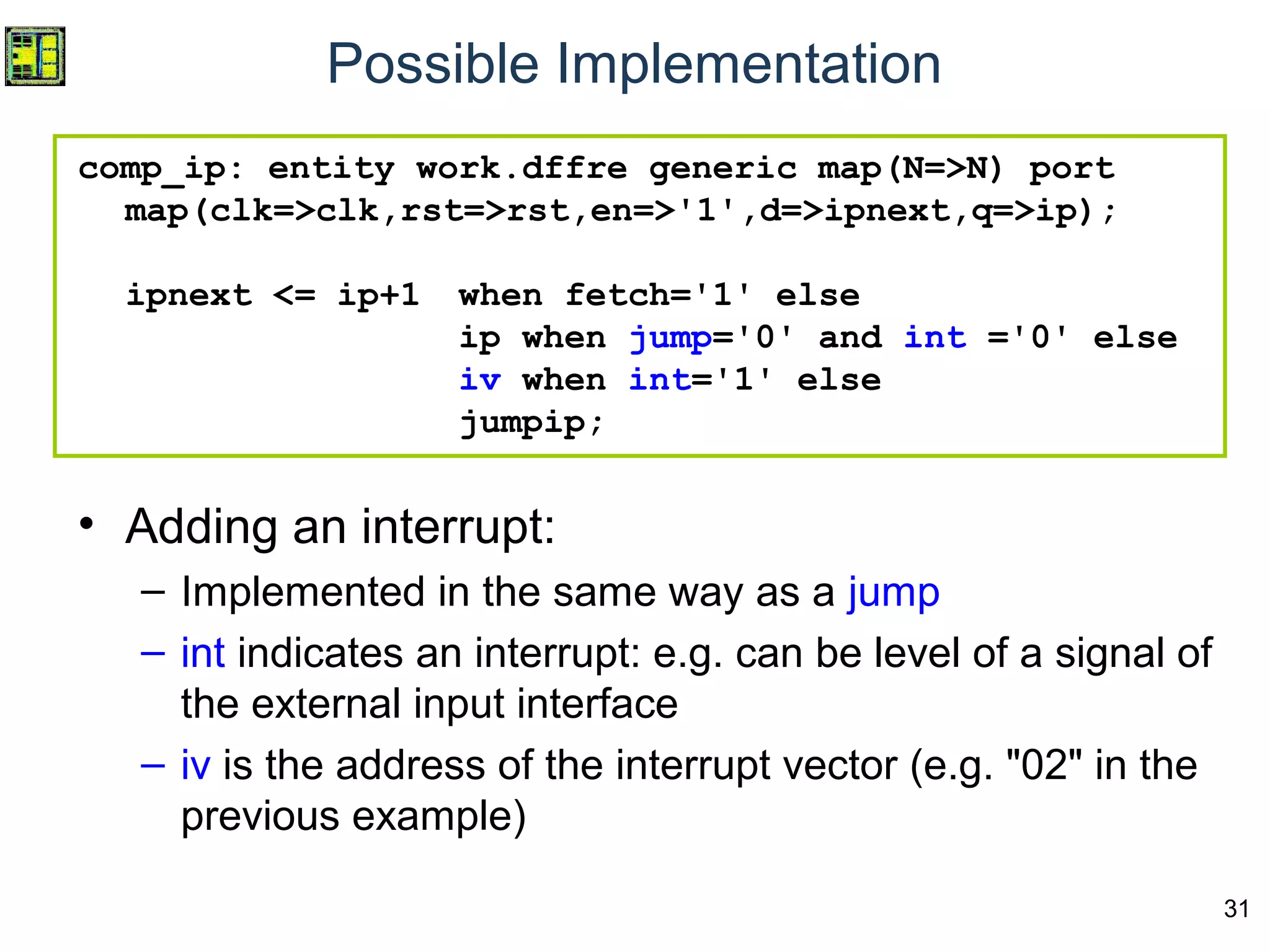

The document discusses digital systems and microprocessor design, focusing on interrupts as a means to change program flow upon hardware events. It explains the concepts of polling versus external interrupts for managing input pins and emphasizes the speed advantage of interrupts in multitasking environments. Additionally, it includes details about handling interrupts, the interrupt vector table, and the distinction between external and internal interrupts.