Downloaded 341 times

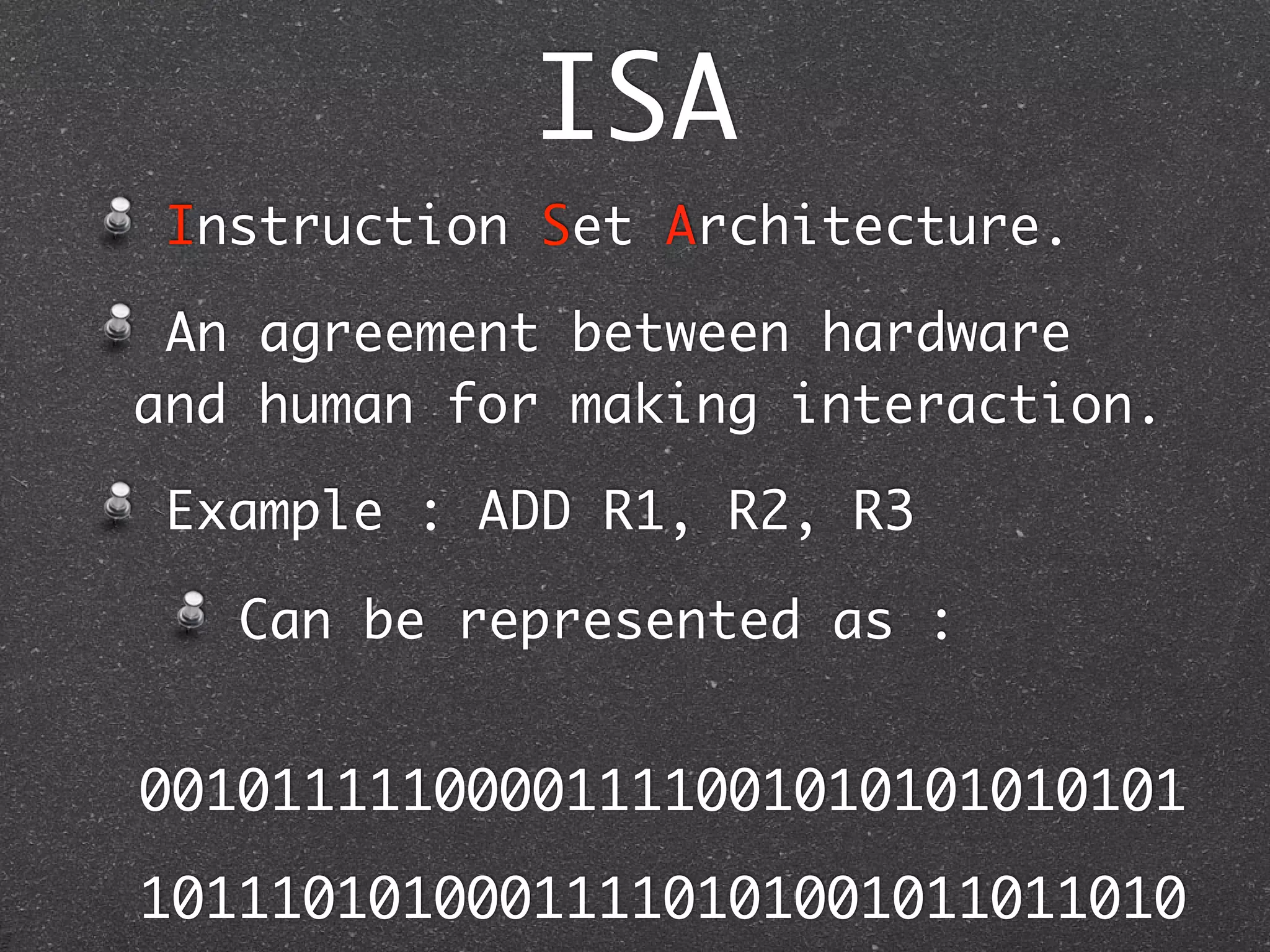

The document discusses the differences between CISC and RISC instruction set architectures. CISC aims to reduce storage usage and support compatibility, while making compilation easier and allowing complex assembly programming. RISC philosophy is to execute one instruction per clock cycle, use fixed-size instructions, only allow load/store instructions to access memory, and support high-level languages. While CISC was originally more common, the conclusion is that RISC provides more design simplicity, better pipelining, and is now preferable given cheaper memory.