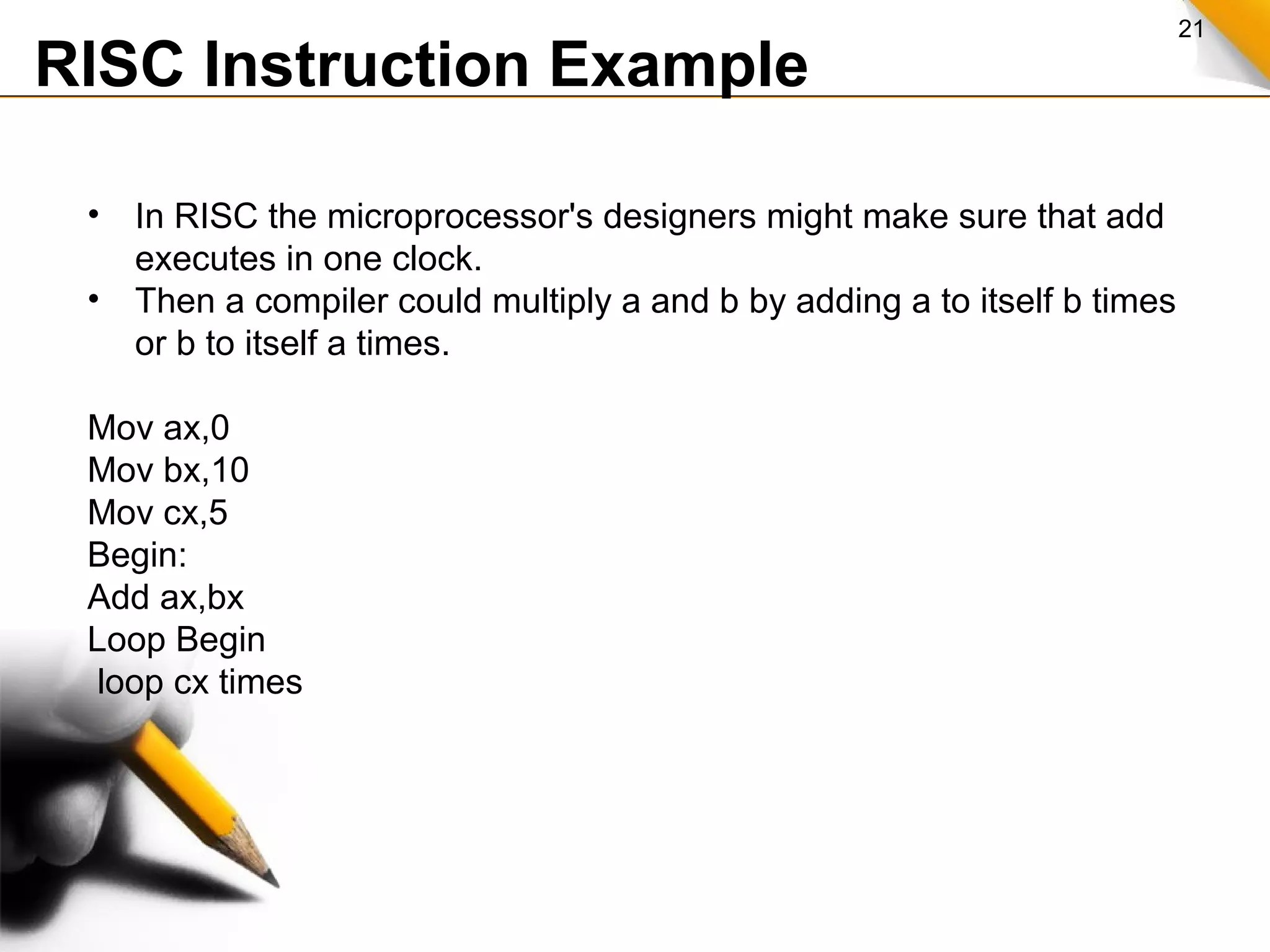

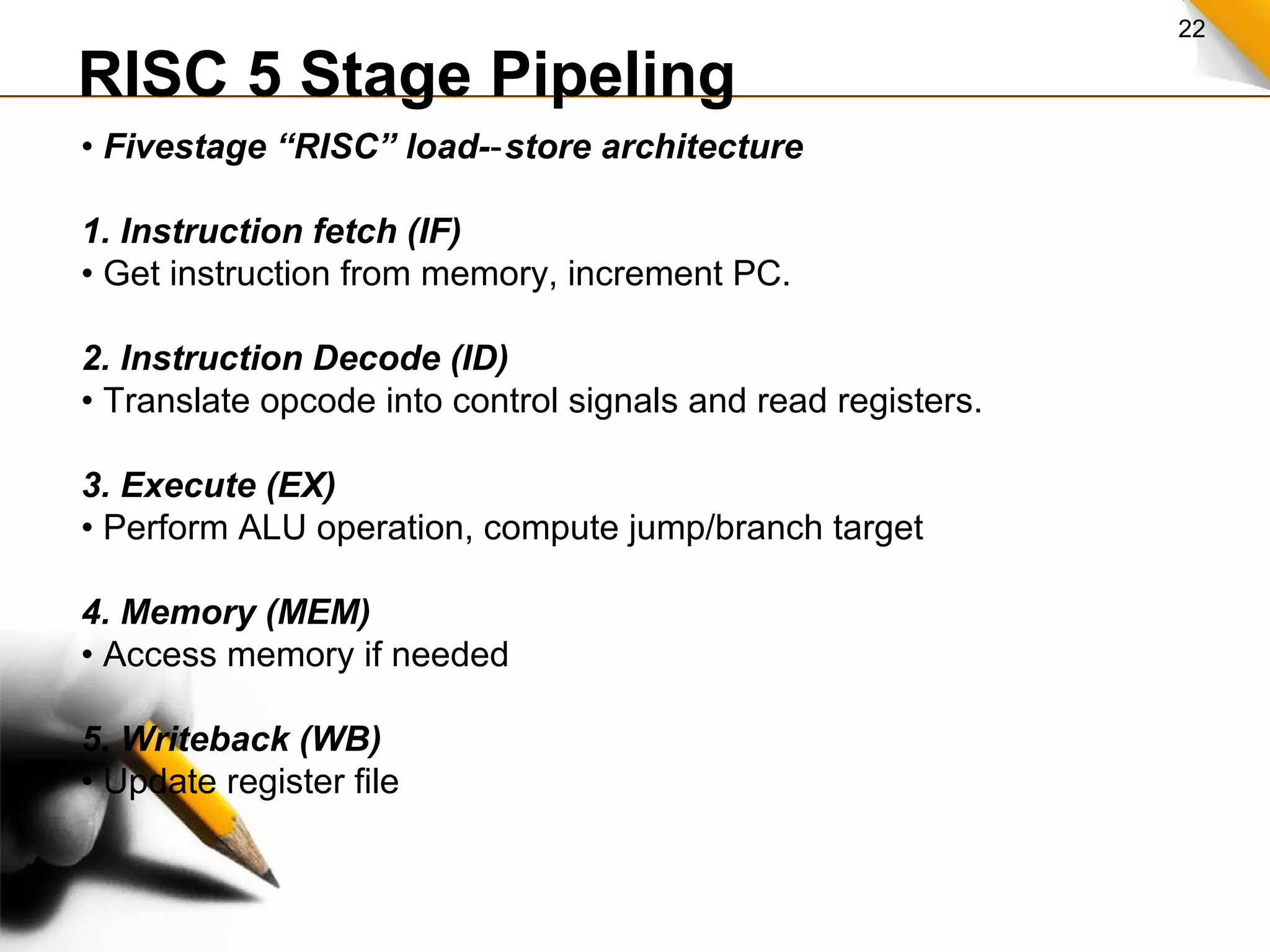

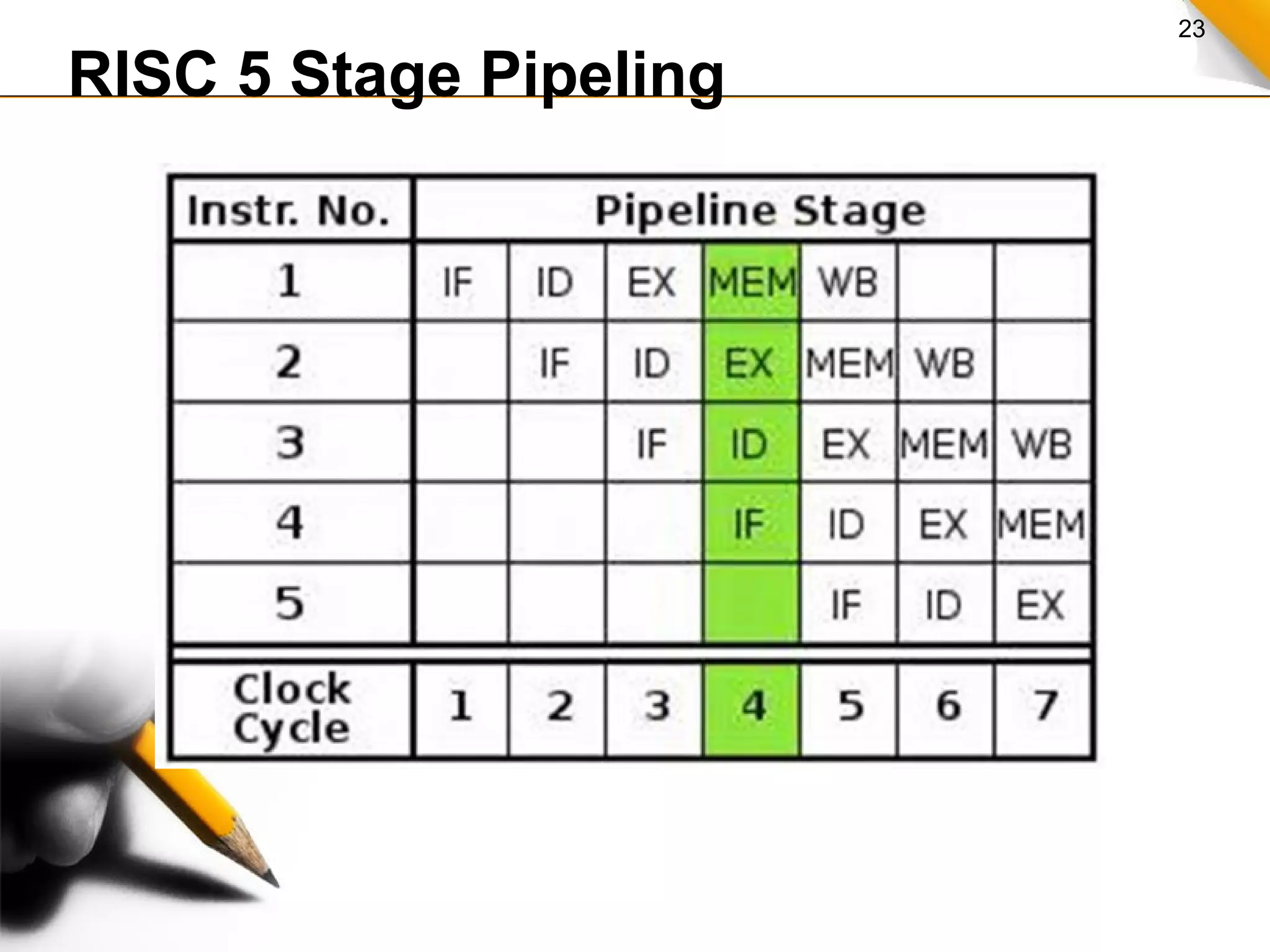

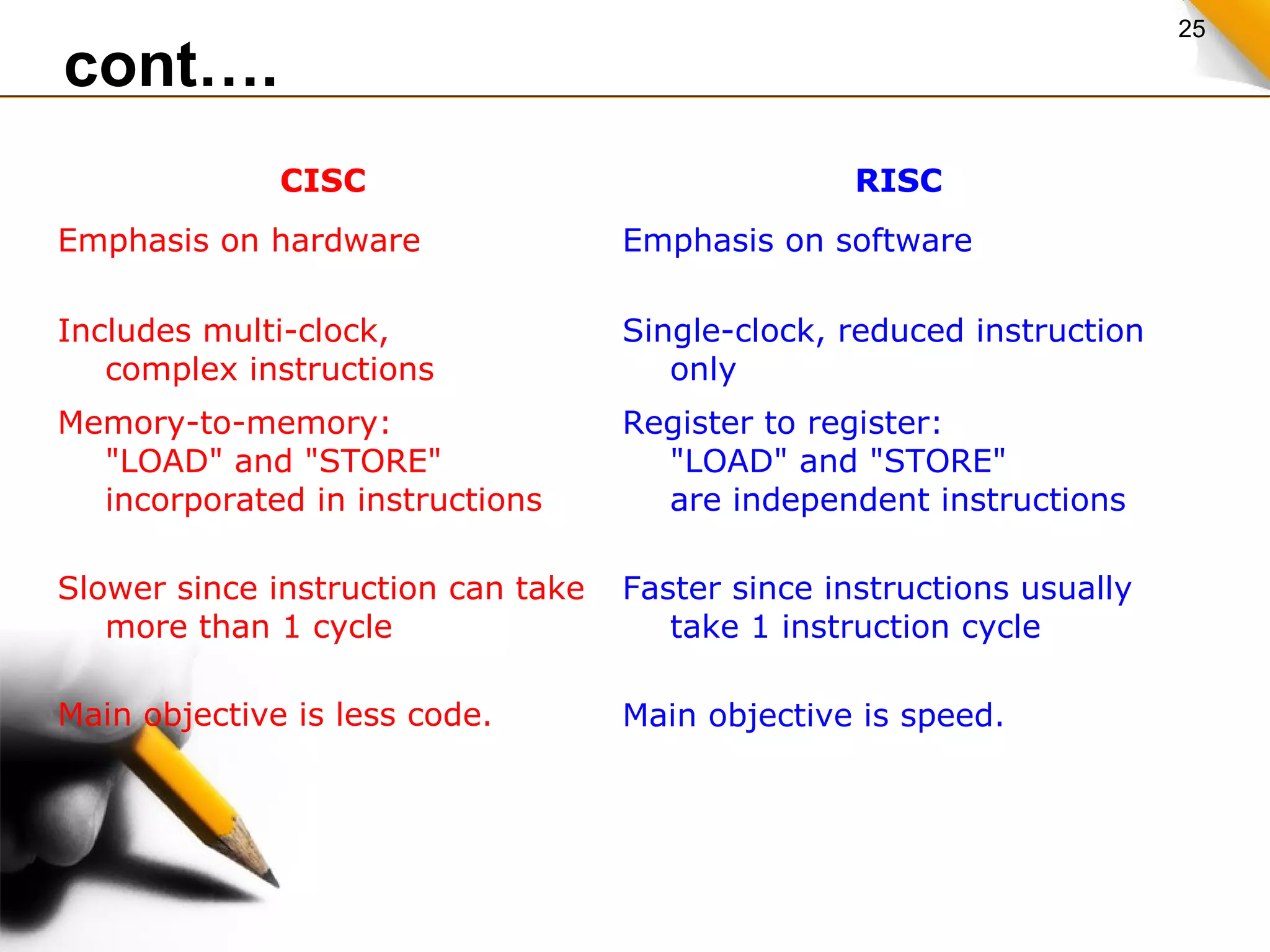

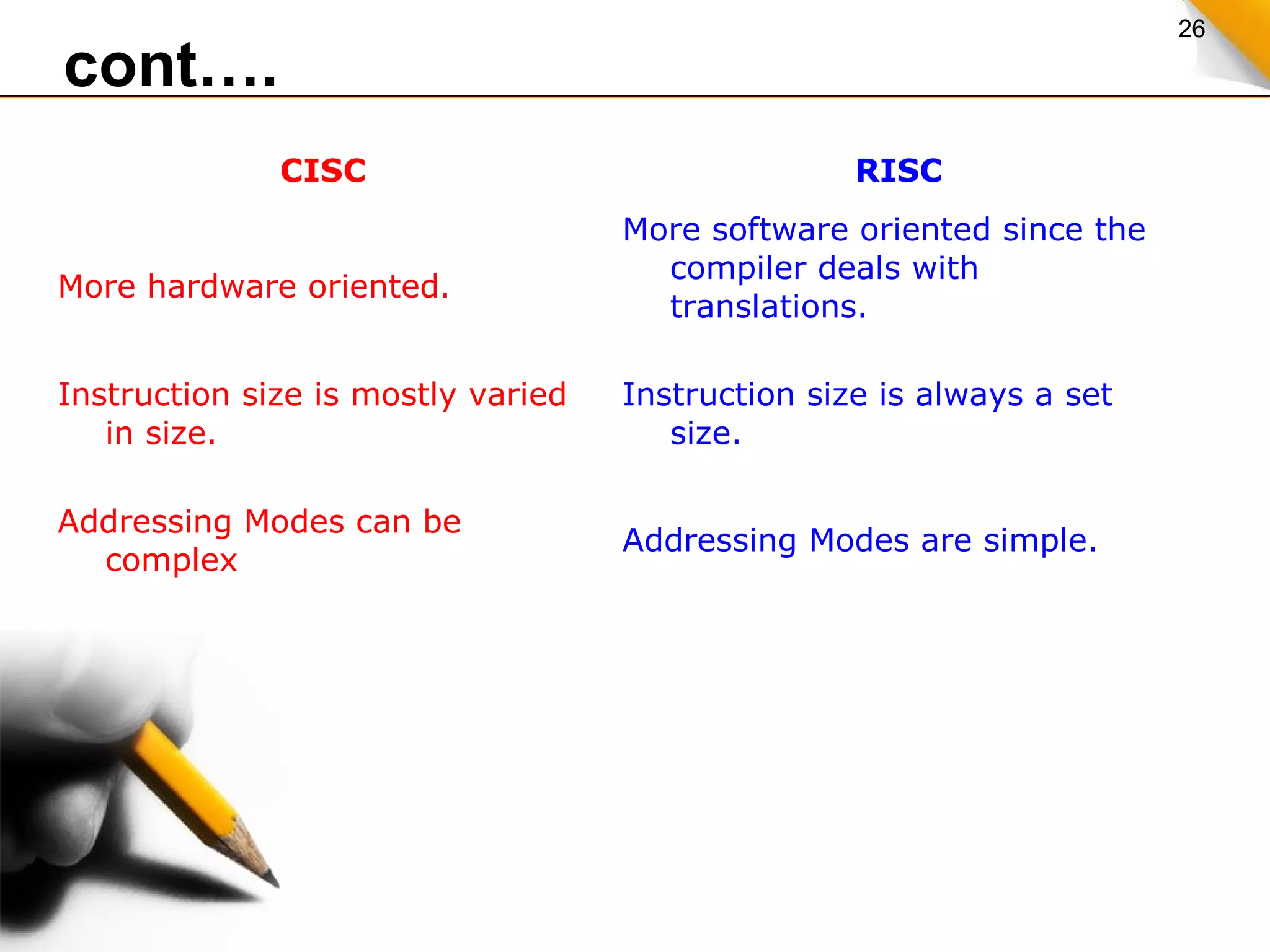

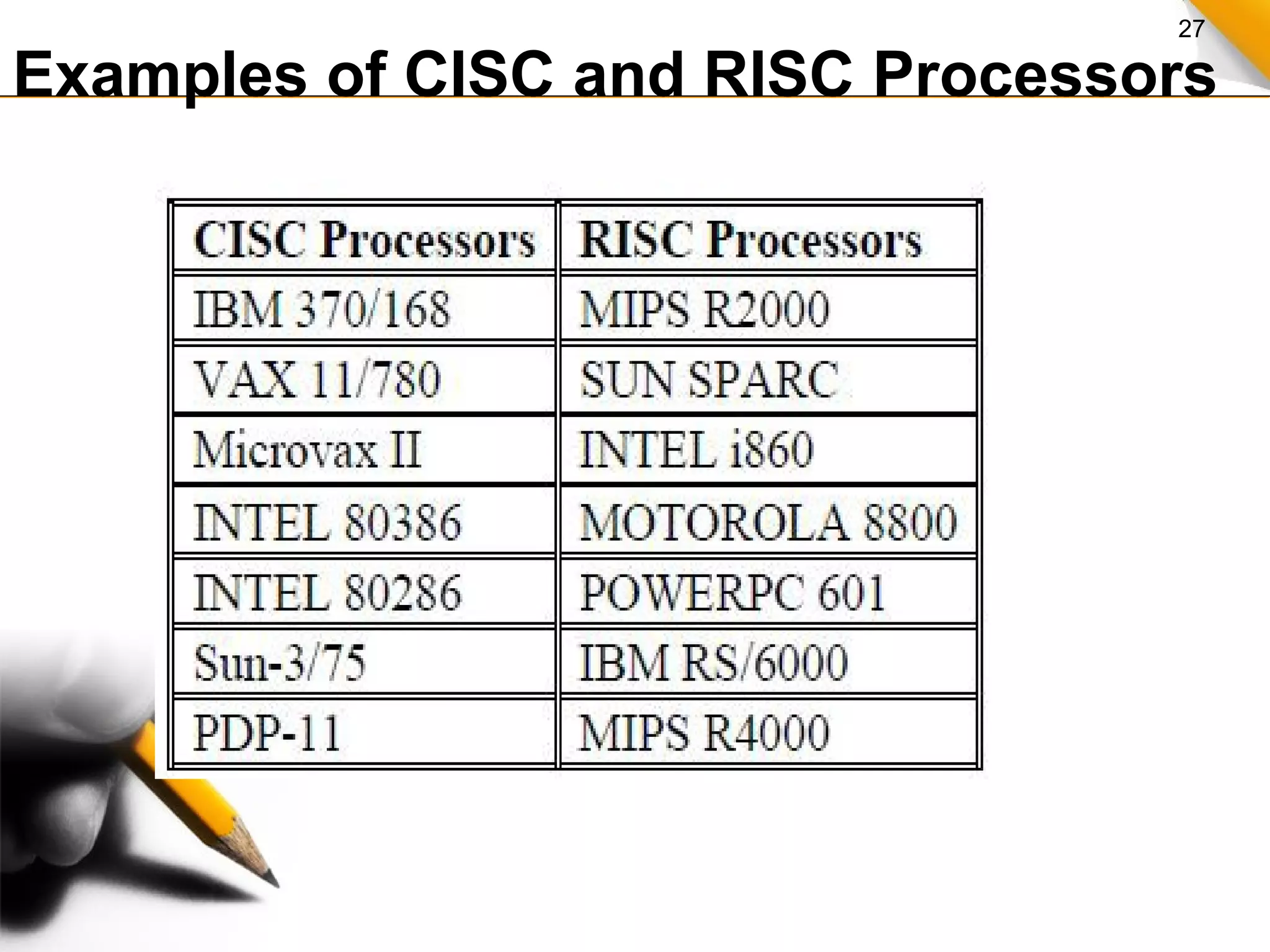

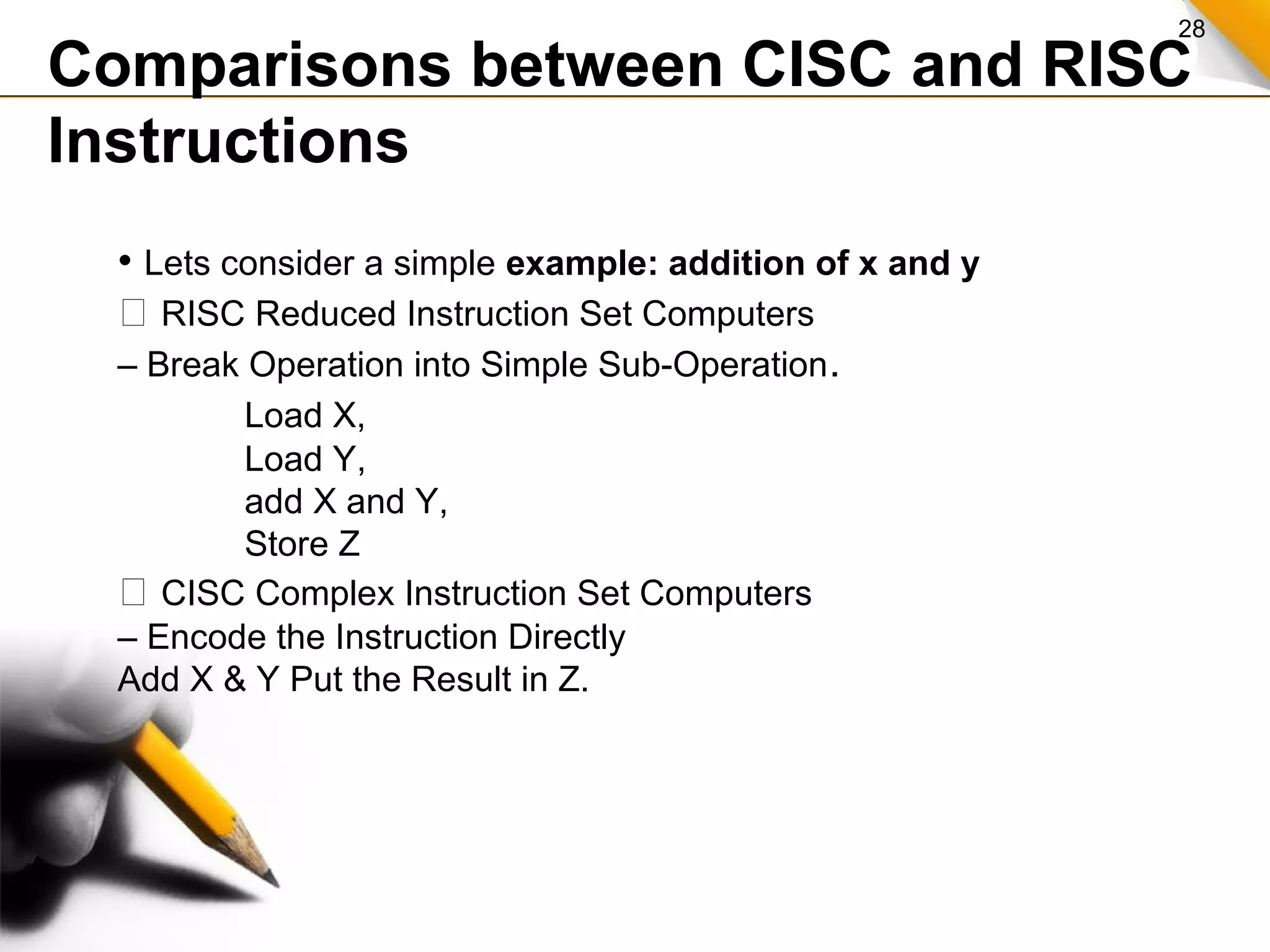

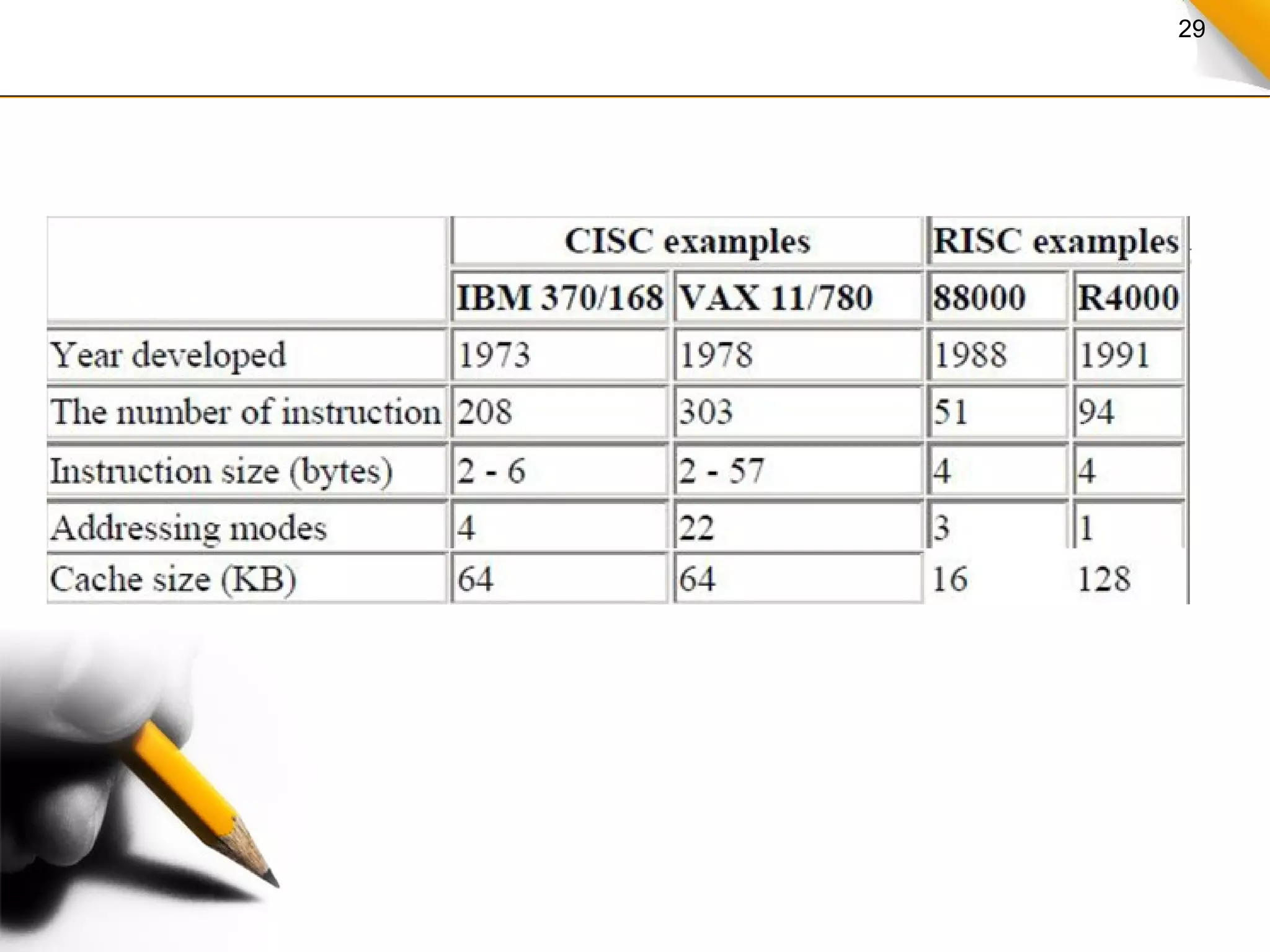

This document compares RISC and CISC processor architectures. It discusses that CISC processors have more complex instructions that can perform multiple operations, while RISC processors have simpler instructions that are optimized to complete in one clock cycle. CISC was developed earlier when memory was expensive, to reduce the number of instructions, while RISC focuses on increasing processor speed. RISC has advantages of faster execution and simpler hardware design, while CISC allows for more compact code.